Patents

Literature

45results about How to "Improve planarization" patented technology

Efficacy Topic

Property

Owner

Technical Advancement

Application Domain

Technology Topic

Technology Field Word

Patent Country/Region

Patent Type

Patent Status

Application Year

Inventor

Method for flattening wafer surface

InactiveCN101359595AImprove planarizationAfter-treatment detailsSemiconductor/solid-state device manufacturingMedia layerPhysics

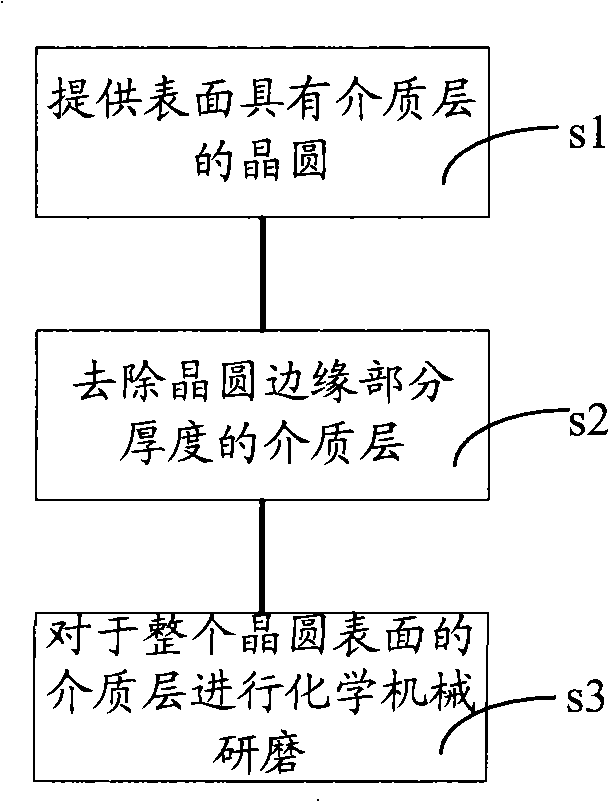

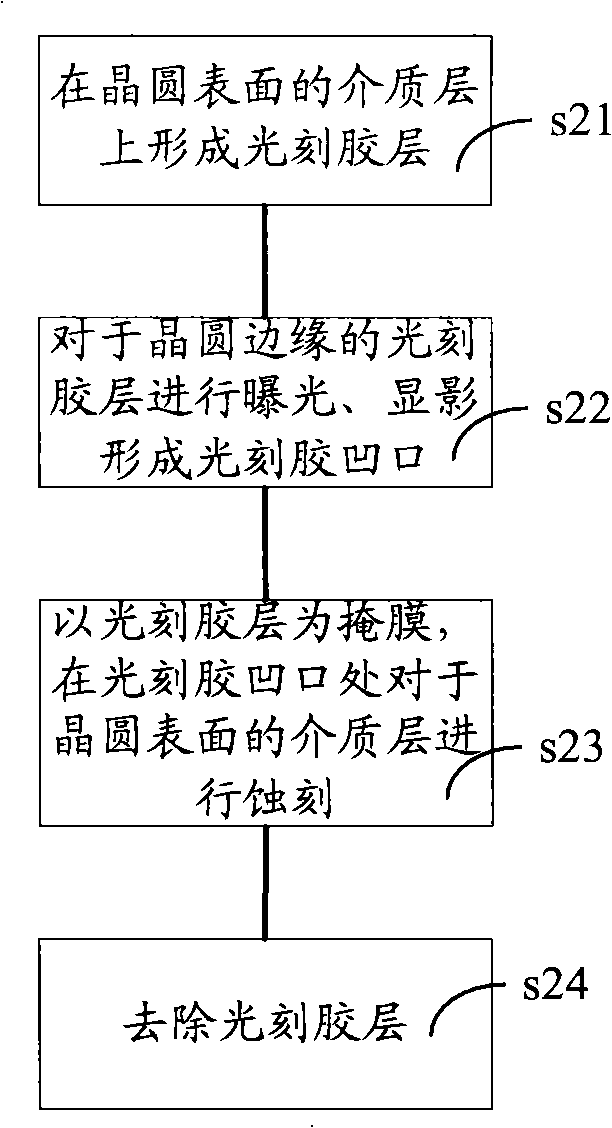

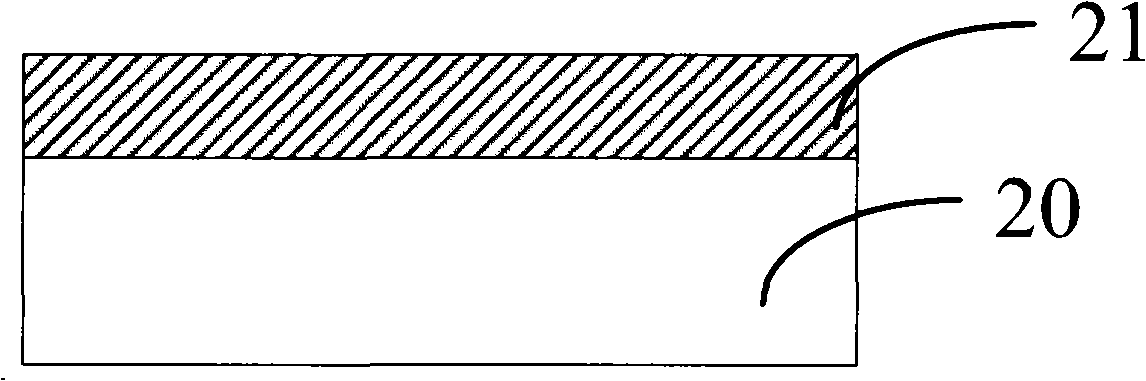

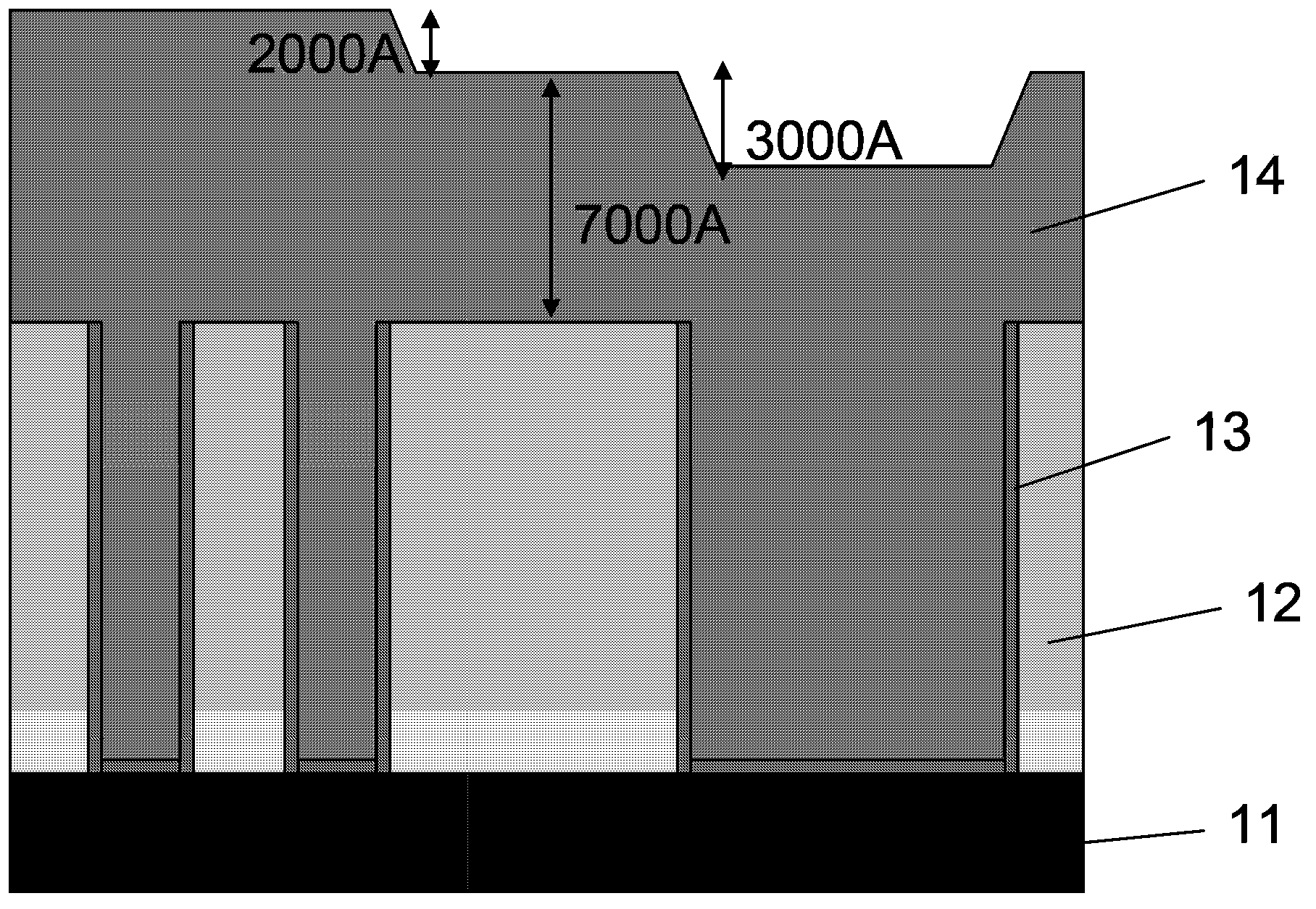

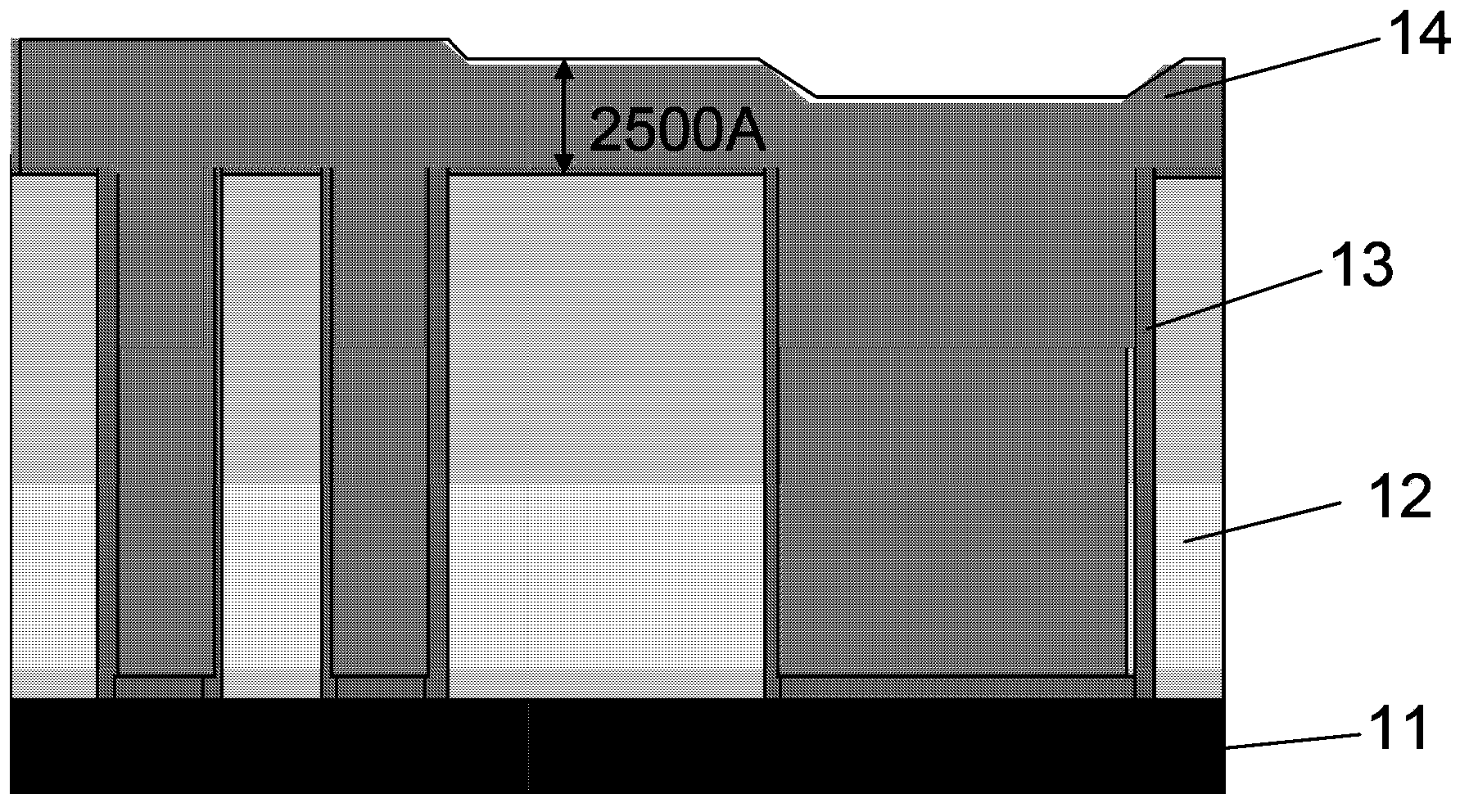

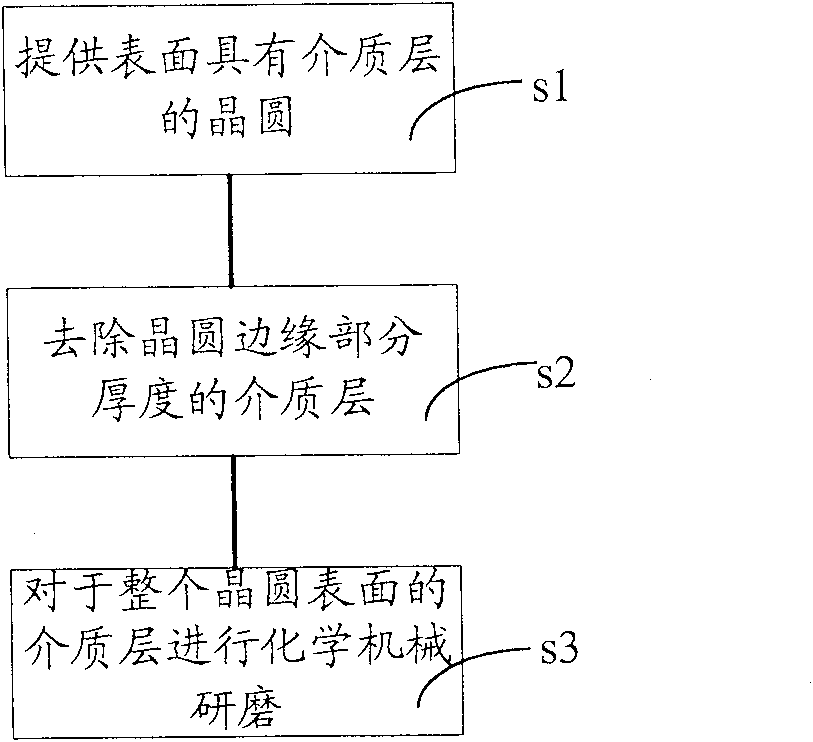

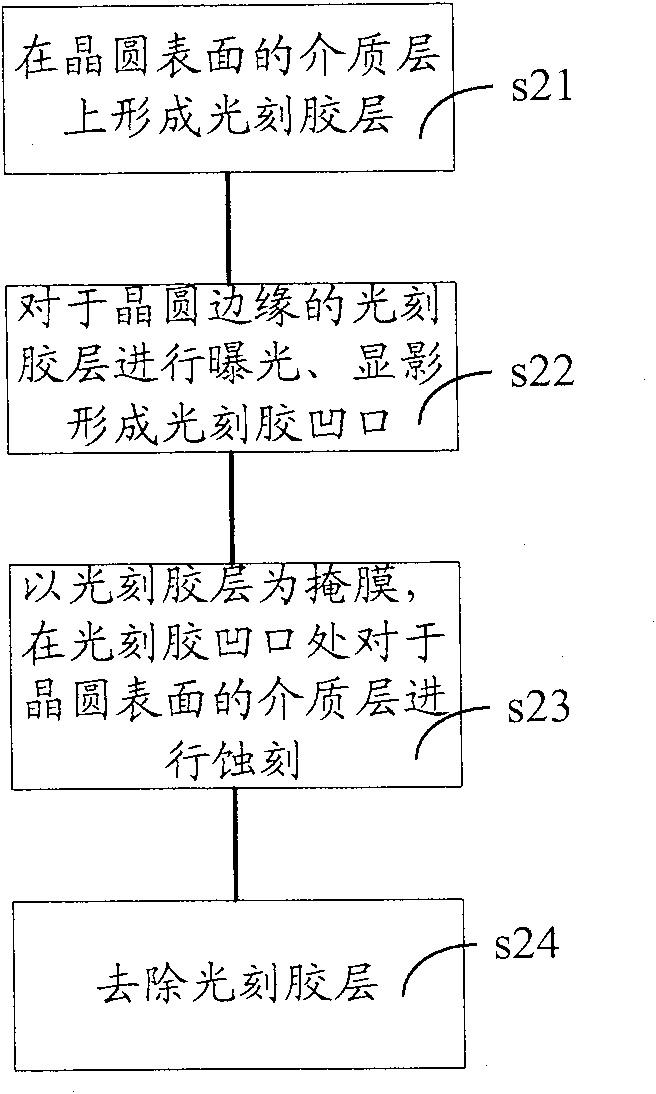

The invention discloses a method for smoothening the surface of a wafer, including the following steps: providing a wafer which is provided with a medium layer on the surface and is composed of a central area and a marginal area surrounding the central area; removing the medium layer at the marginal area; and chemically and mechanically rubbing the whole medium layer on the surface of the wafer; wherein the thickness of the medium layer at the marginal area after being rubbed by a test piece is bigger than the depth of the etched through hole; and the removed thickness of the medium layer at the marginal area is larger than or equal to the average thickness difference tested by a test piece between the medium layer at the central area and the marginal area of the chemically and mechanically rubbed wafer. The method for smoothening the surface of the wafer reduces thickness difference between the medium layer at the central area and the marginal area of the wafer after chemically and mechanically rubbing the surface of the medium layer on the surface of the wafer, thus improving the smoothness of the surface of the wafer.

Owner:SEMICON MFG INT (SHANGHAI) CORP +1

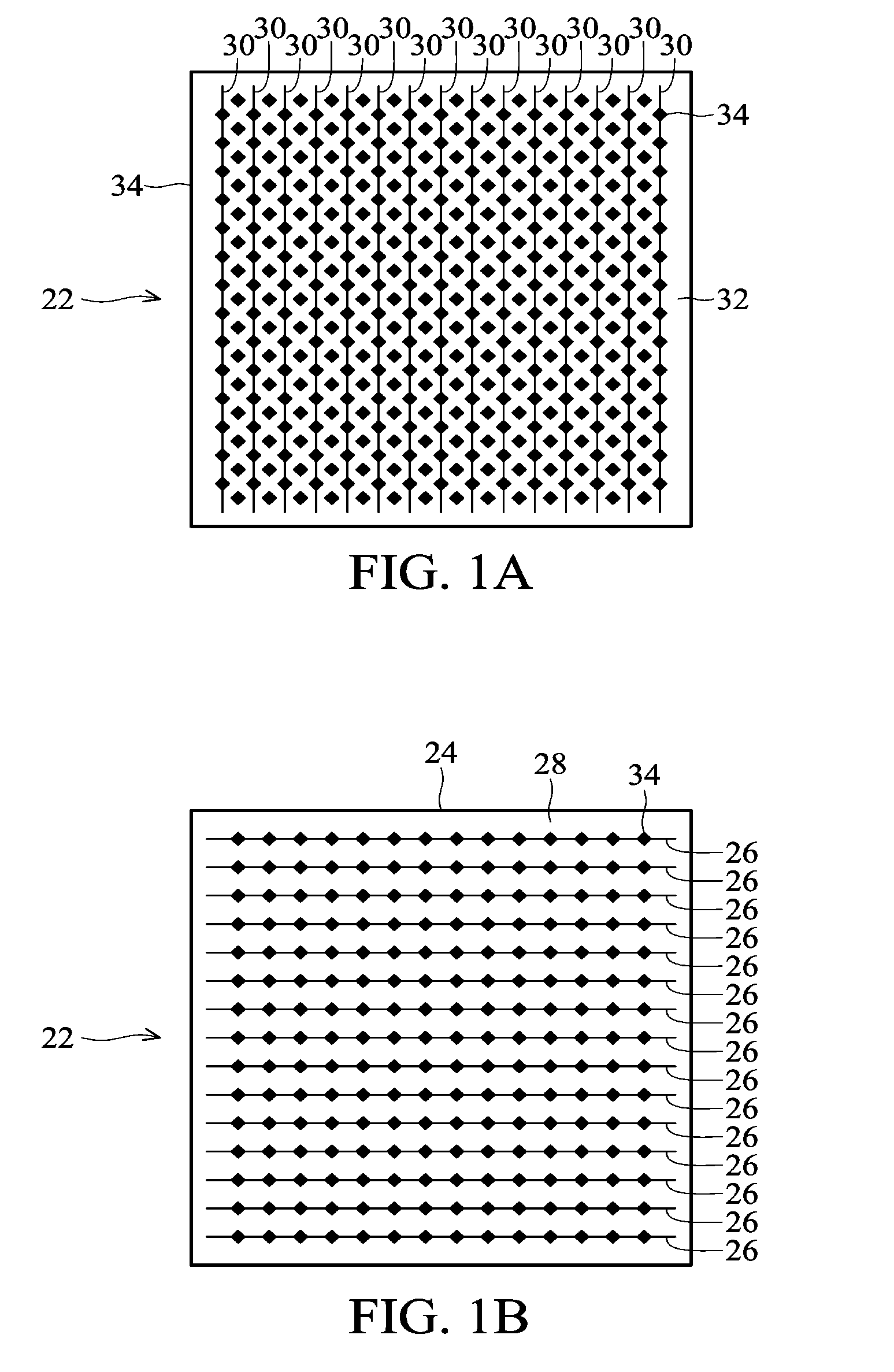

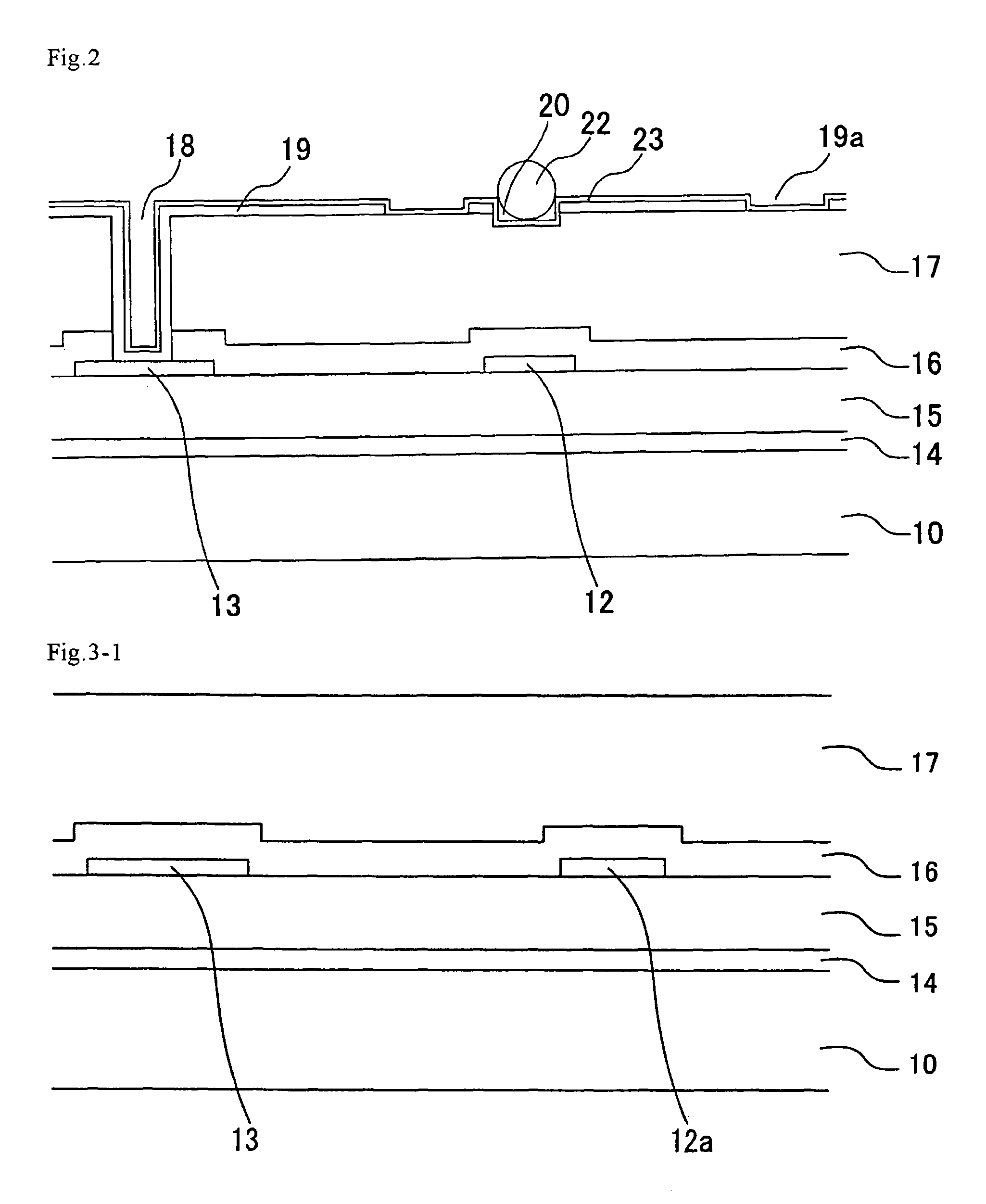

Touch sensitive device

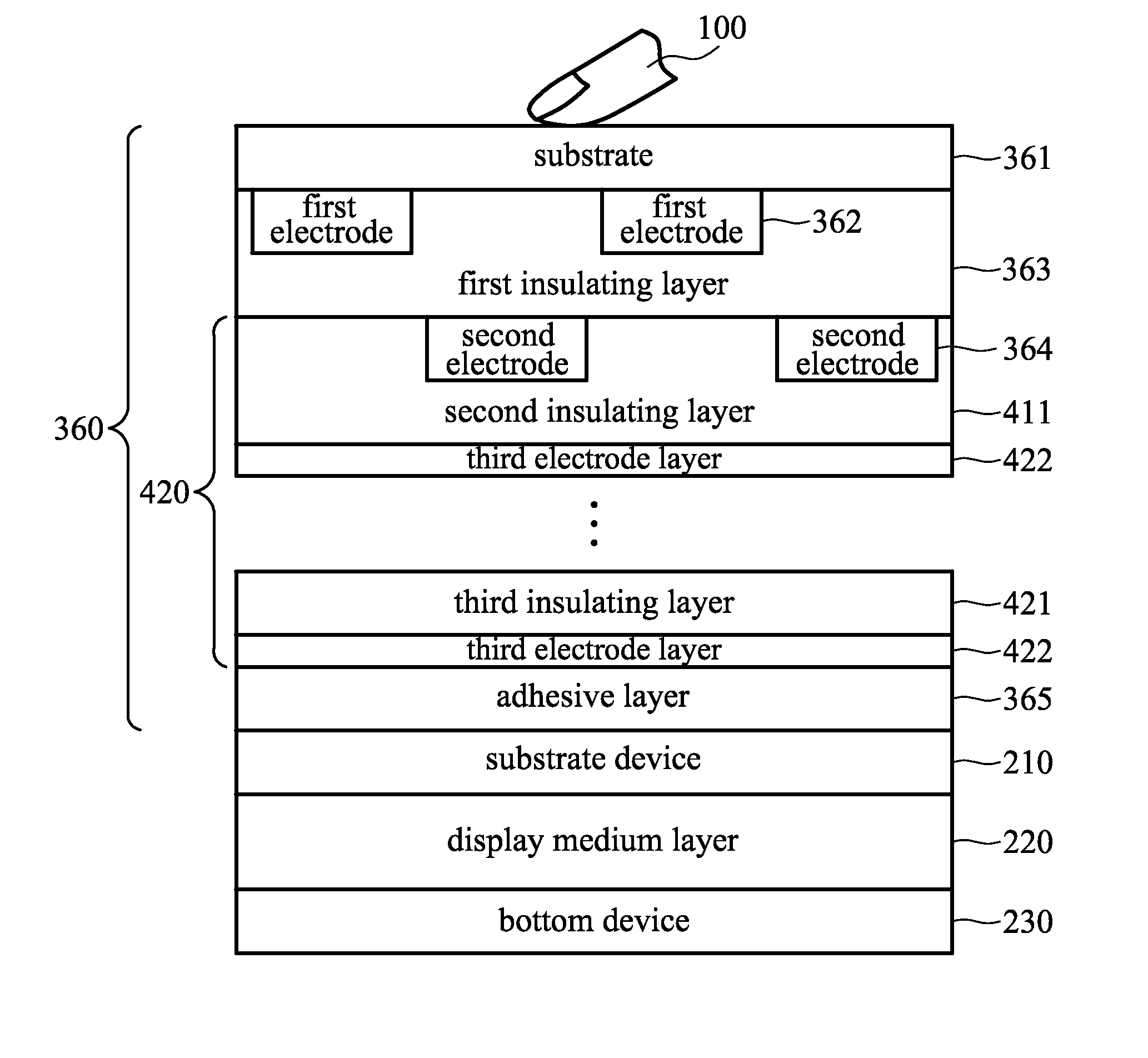

ActiveUS8982088B2Improve performanceImprove planarizationTransmission systemsCathode-ray tube indicatorsElectrical and Electronics engineeringElectrode

Owner:HANNSTAR DISPLAY CORPORATION

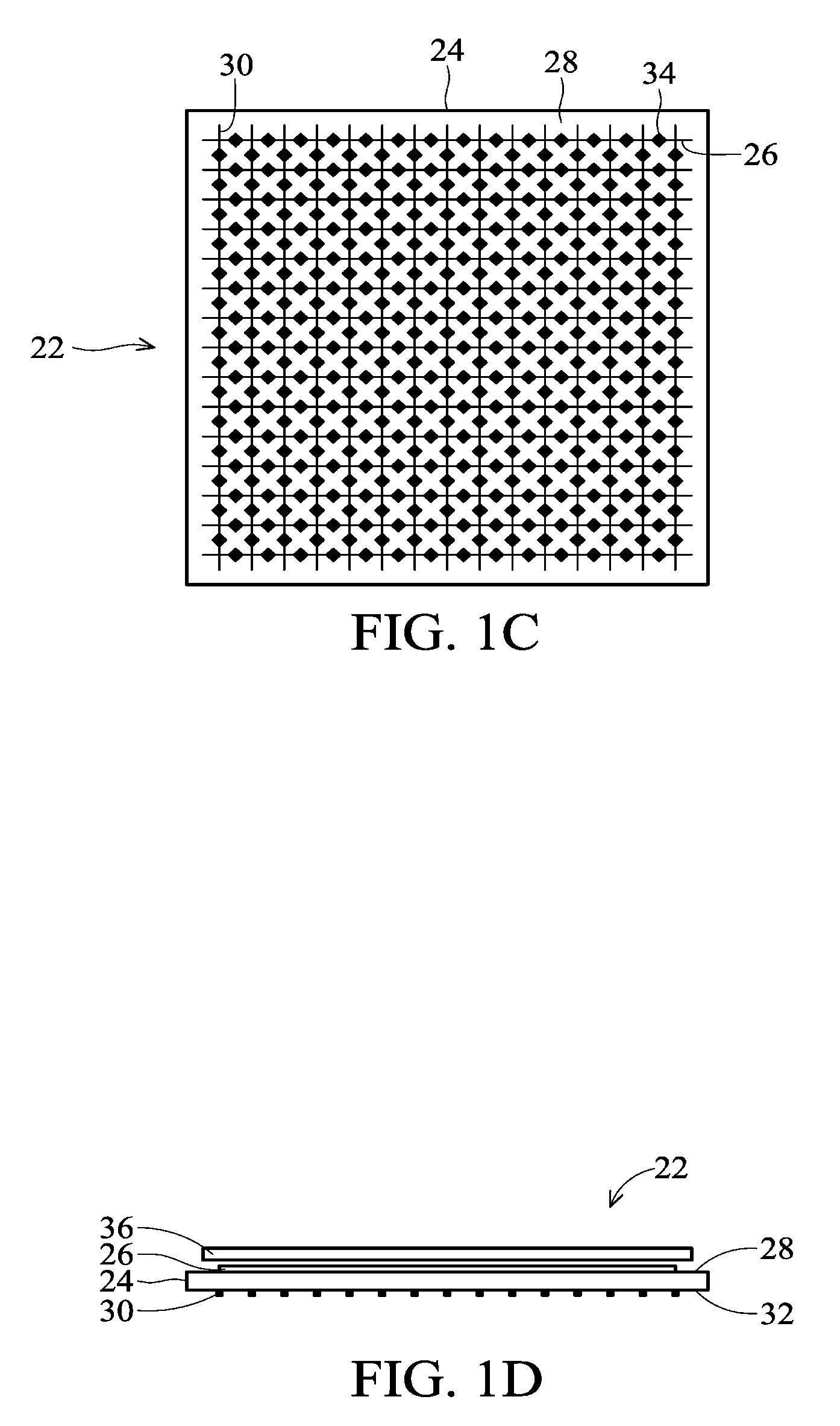

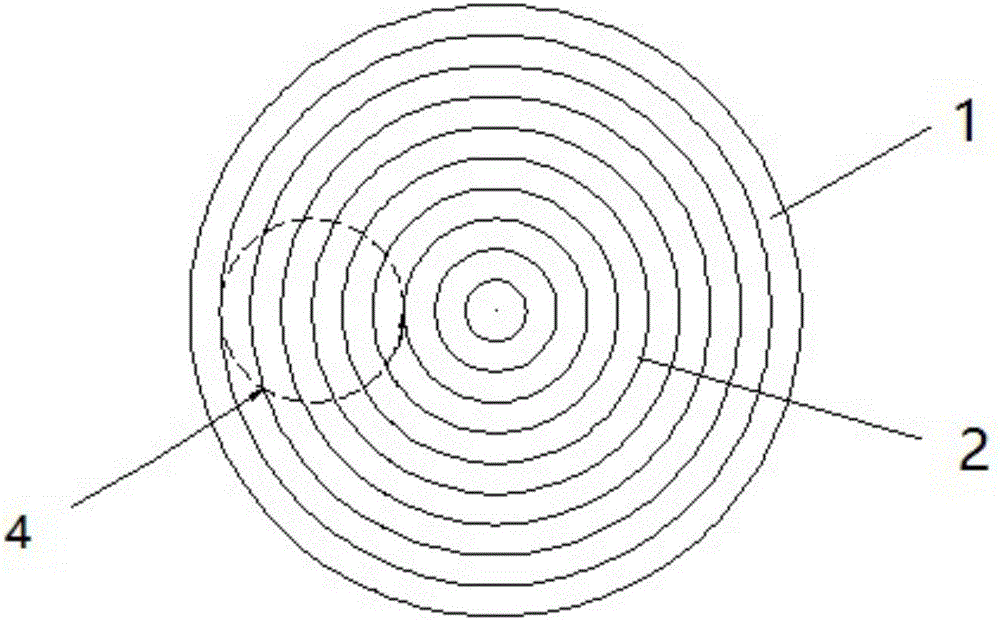

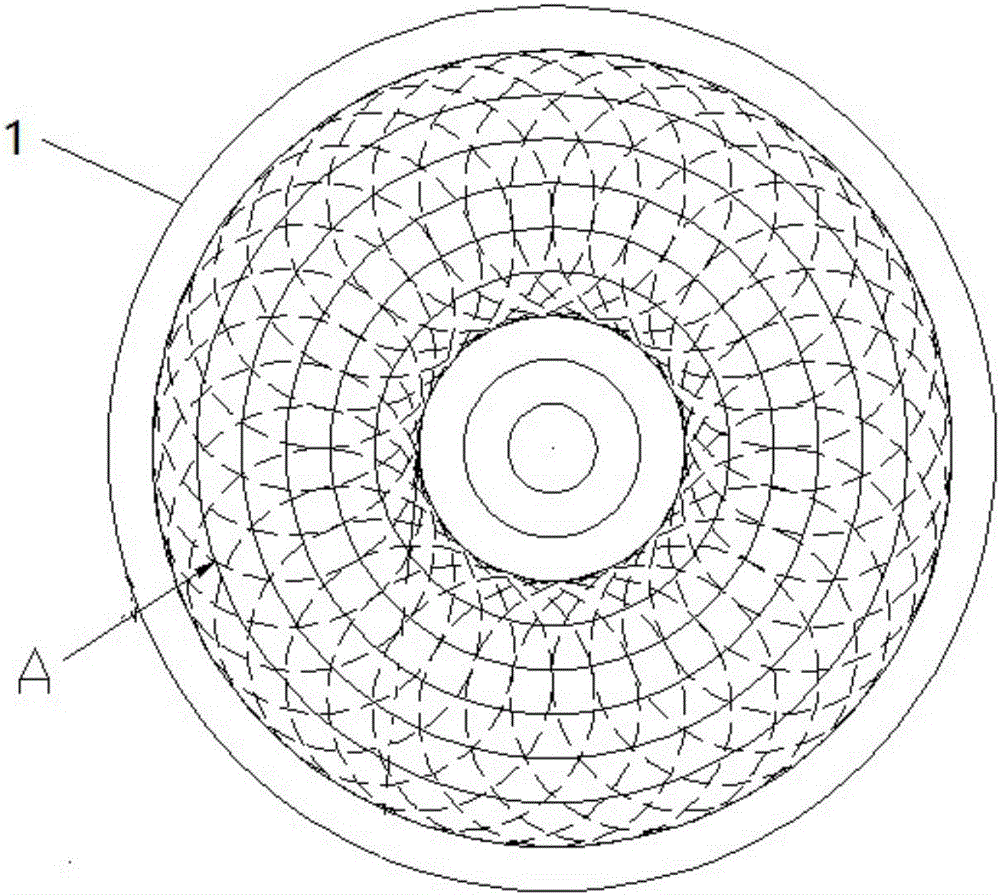

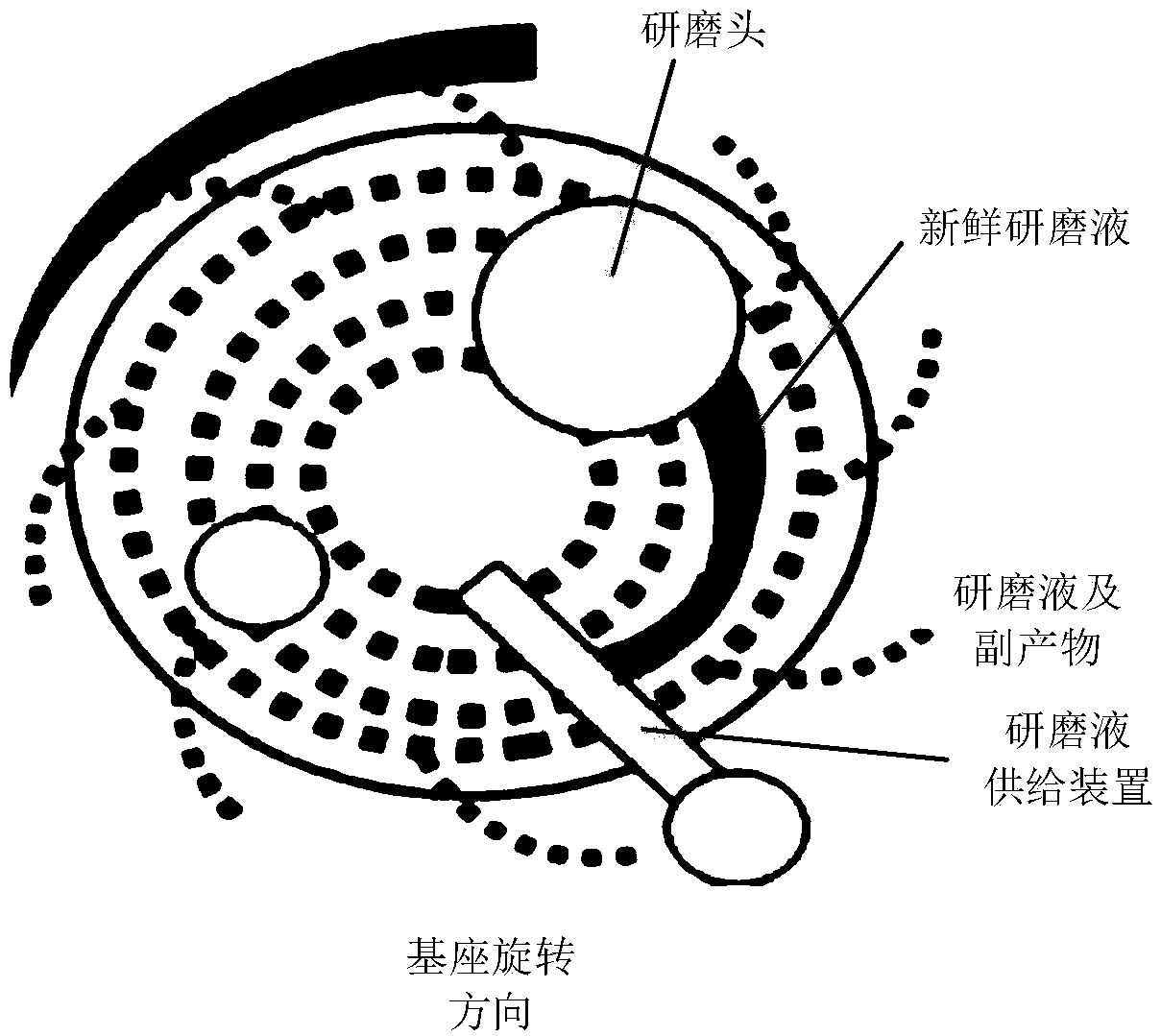

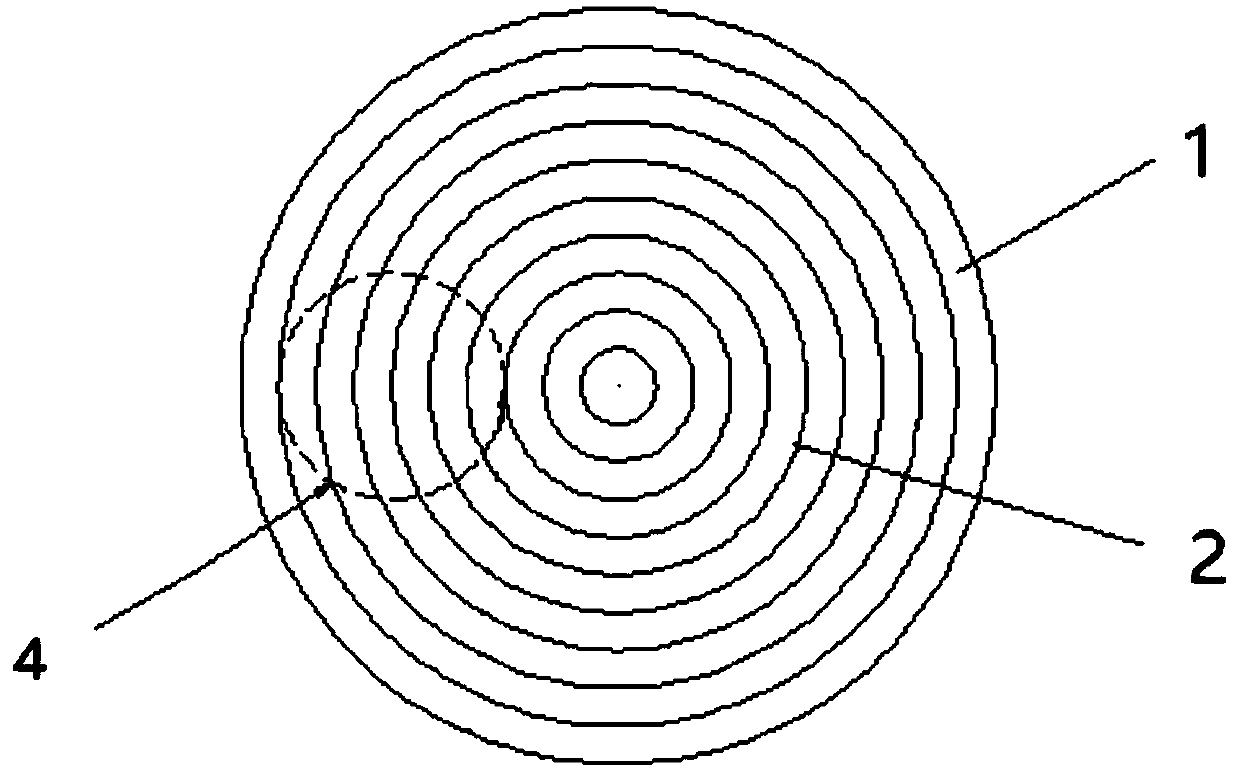

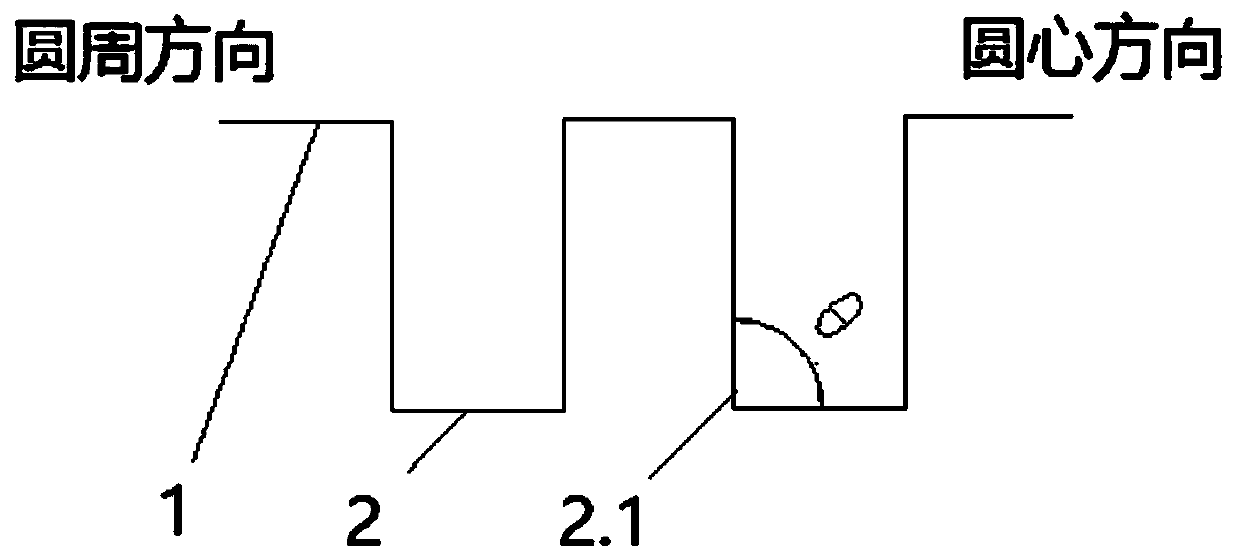

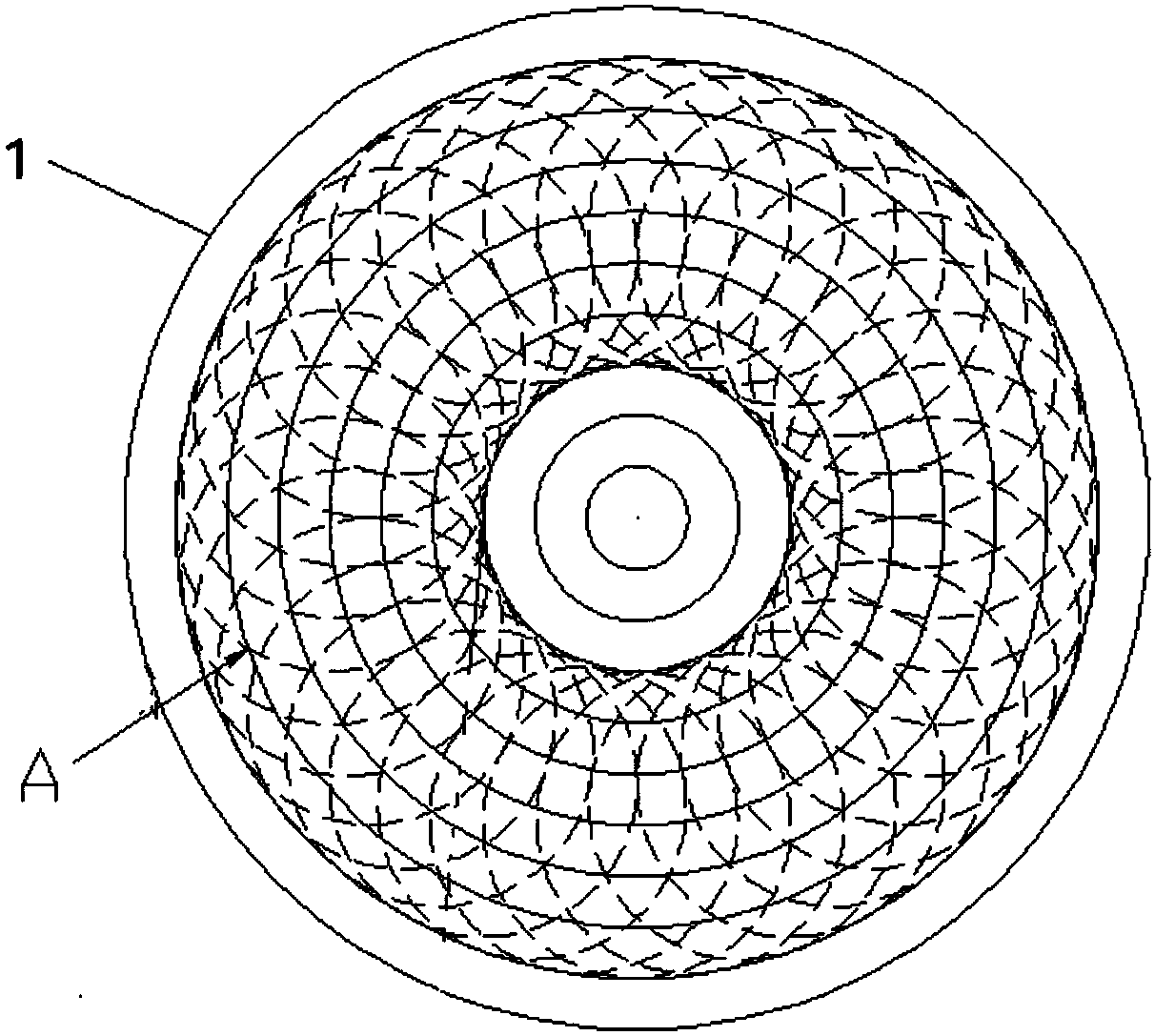

Polishing pad

The invention discloses a polishing pad for solving the problems of nonuniform distribution of polishing liquid and need of further improvement of the polishing speed and the leveling degree in a traditional polishing pad. The polishing pad at least comprises a circular polishing layer; a groove for flowing the polishing liquid is formed in the upper surface of the polishing layer; the groove consists of a peripheral groove and a radial groove; the peripheral groove is a peripheral geometric center symmetry pattern with the circle center of the polishing layer as center; the edges m of the pattern are not fewer than 3; and the radial groove is a straight line or / and a curve scattered from the peripheral direction along the circle center, and has an intersecting point with the peripheral groove. The polishing pad is simple in structure, can enable the polishing liquid to uniformly distribute and flow in a polishing area, keeps uniform concentration of reactants and products in the polishing liquid in the polishing area to the greatest extent, accelerates the polishing speed, and improves the wafer planar degree.

Owner:HUBEI DINGLONG CO LTD

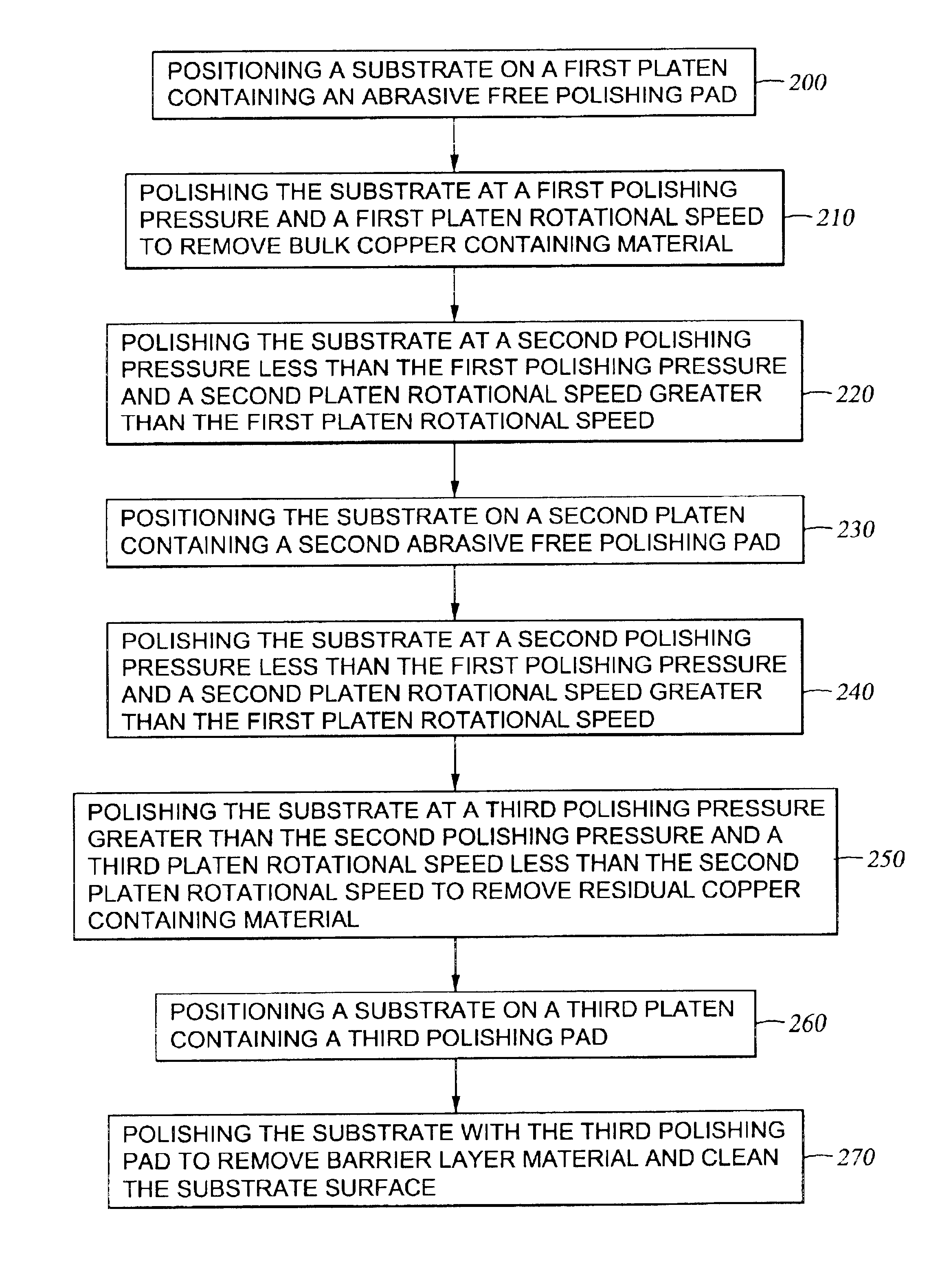

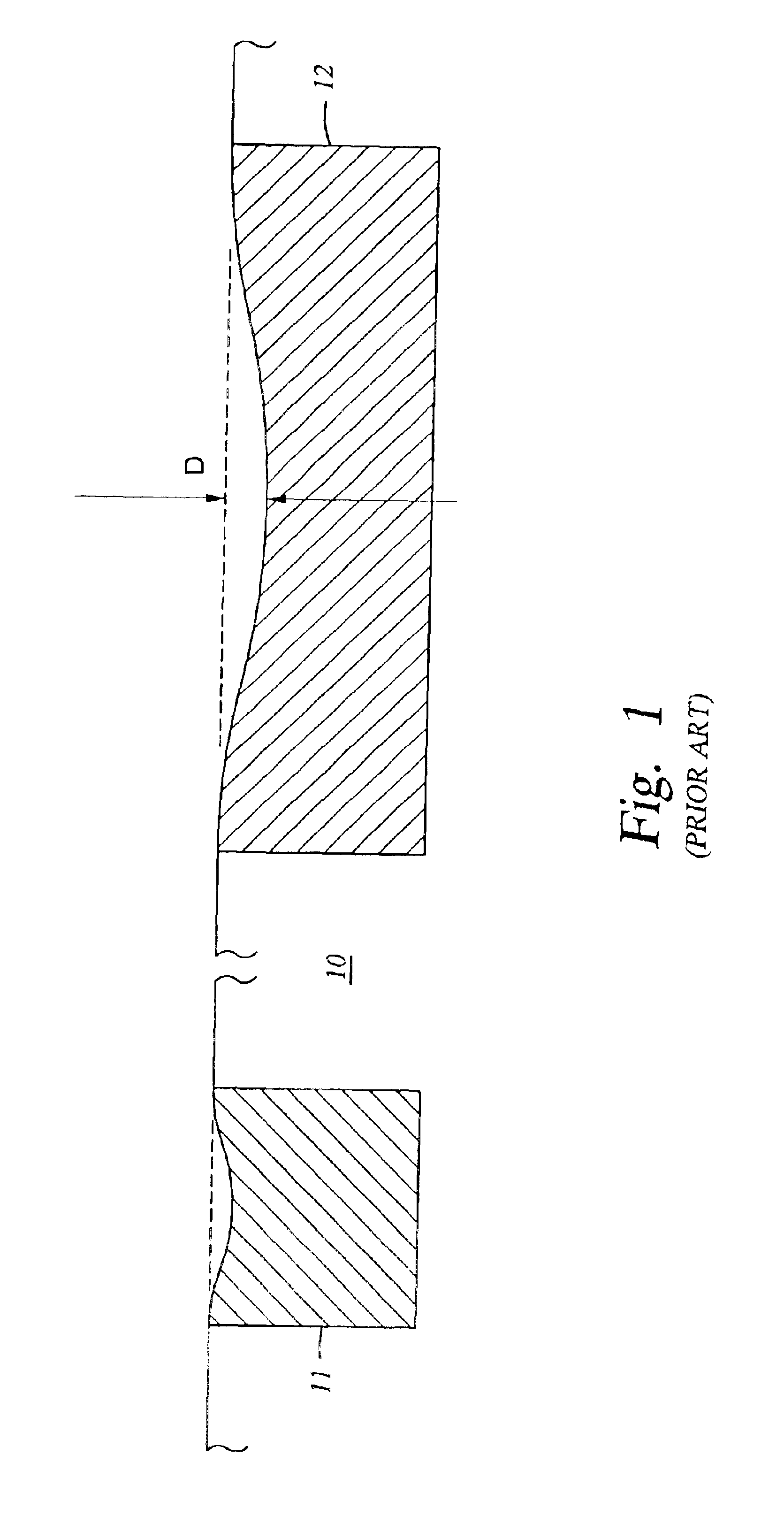

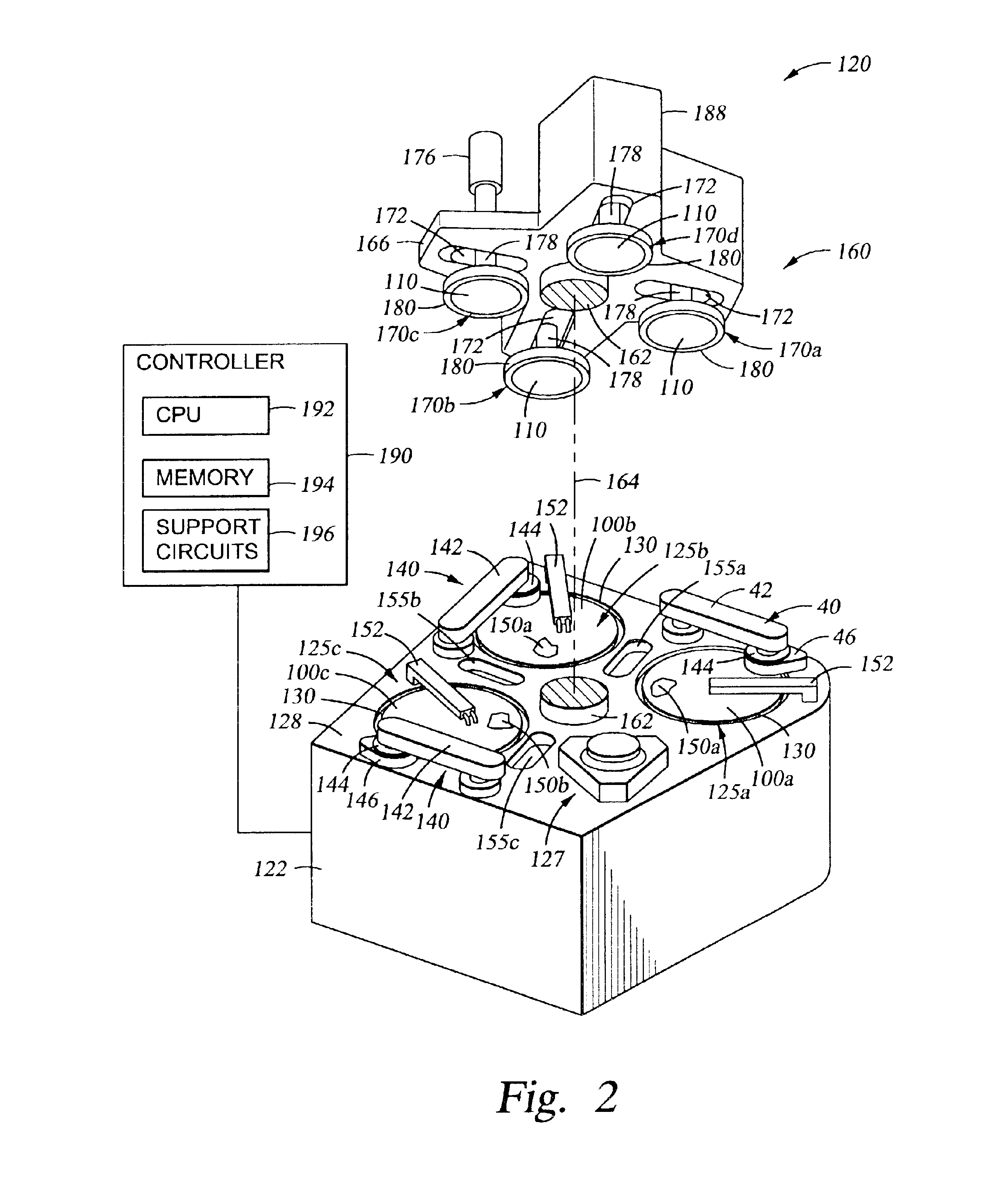

Method for chemical mechanical polishing of semiconductor substrates

InactiveUS6821881B2Improve polish uniformityImprove planarizationSemiconductor/solid-state device manufacturingLapping machinesChemical-mechanical planarizationLow-k dielectric

Methods and apparatus for processing substrates to improve polishing uniformity, improve planarization, remove residual material and minimize defect formation are provided. In one aspect, a method is provided for processing a substrate having a conductive material and a low dielectric constant material disposed thereon including polishing a substrate at a polishing pressures of about 2 psi or less and at platen rotational speeds of about 200 cps or greater. The polishing process may use an abrasive-containing polishing composition having up to about 1 wt. % of abrasives. The polishing process may be integrated into a multi-step polishing process.

Owner:APPLIED MATERIALS INC

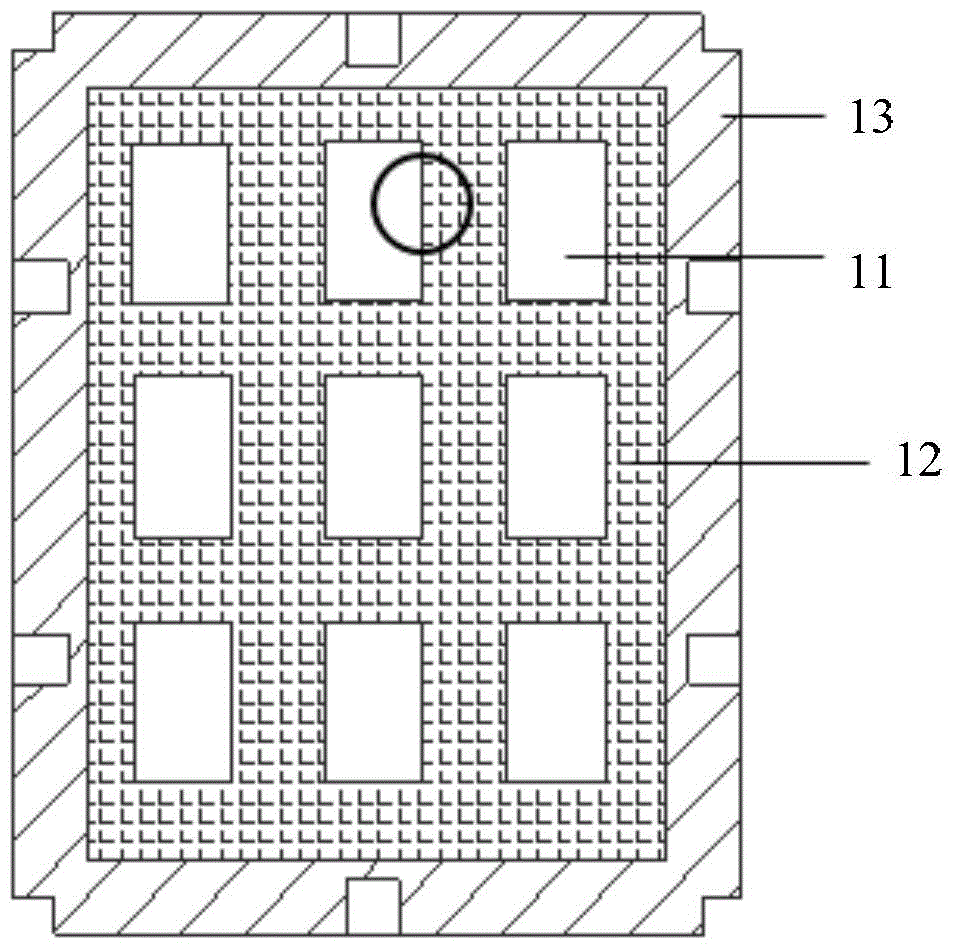

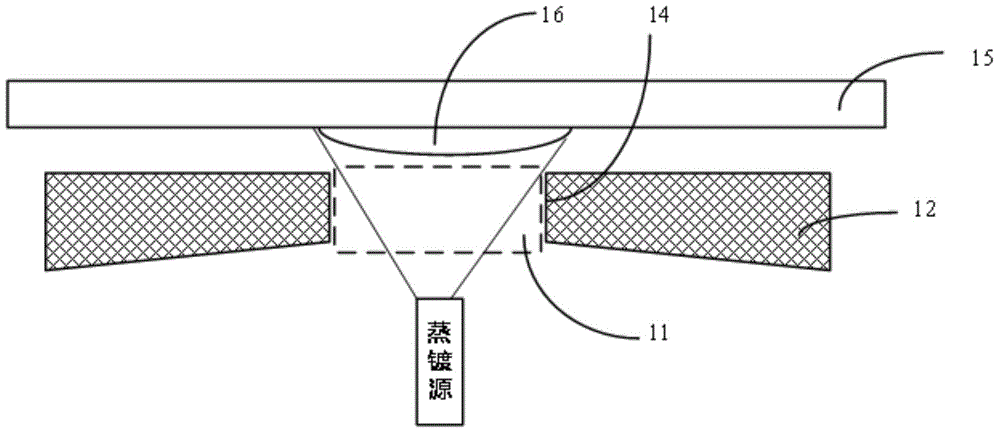

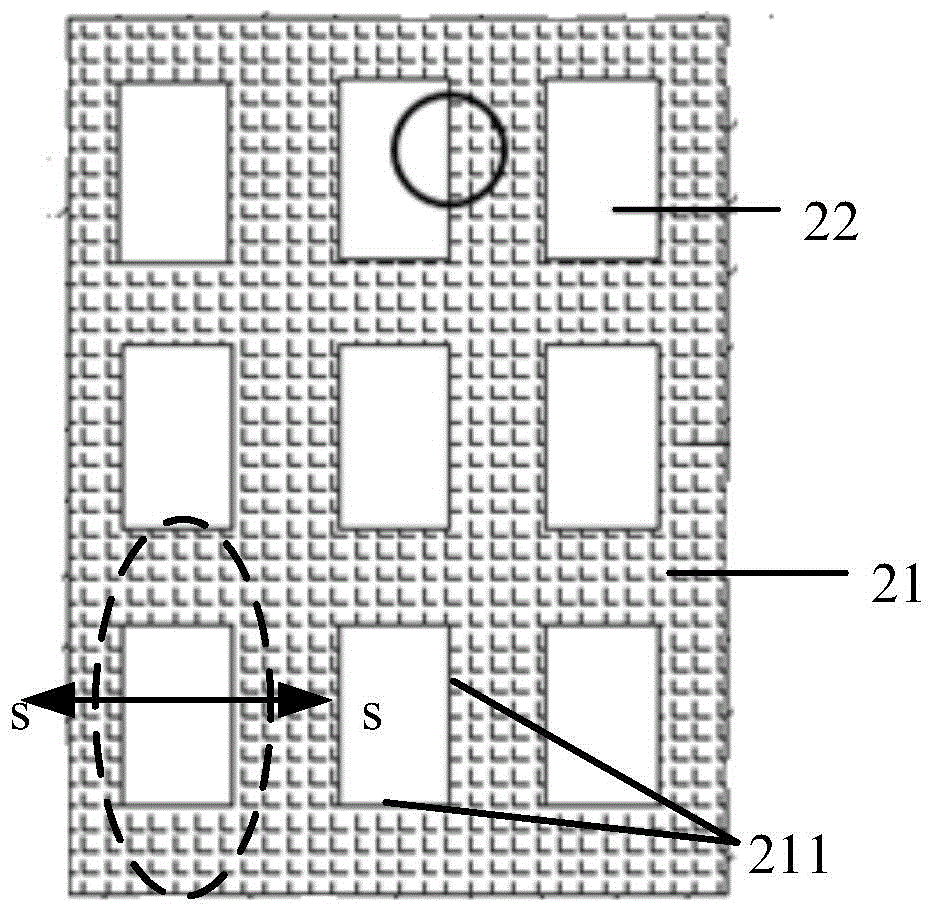

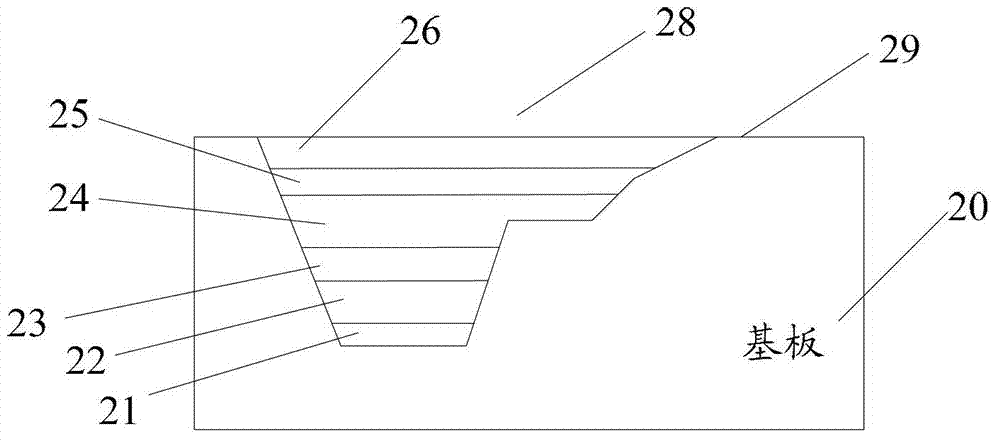

Mask plate, manufacturing method thereof, display panel and display device

ActiveCN104862647AImprove planarizationAvoid breakingVacuum evaporation coatingSolid-state devicesEngineeringLaser cutting

The invention discloses a mask plate, a manufacturing method thereof, a display panel and a display device. According to the mask plate, the manufacturing method thereof, the display panel and the display device, a traditional mask plate is improved, particularly, a notch is formed at the positions where at least part of the side cut surface of each opening of the mask plate intersects with the surface of one side close to a substrate during evaporation, the notches are formed through the chemical etching method or the laser cutting method, the area of the side, close to the substrate, of an opening is made to be larger than the area of the side, away from the substrate, of the opening during evaporation, in this way, the area of the marginal area of an evaporated film on the substrate is increased, the flatness of the marginal area is improved, the possibility that the metal film formed in the later stage breaks due to the fact that a step is too high is avoided, and the yield of products is increased.

Owner:BOE TECH GRP CO LTD

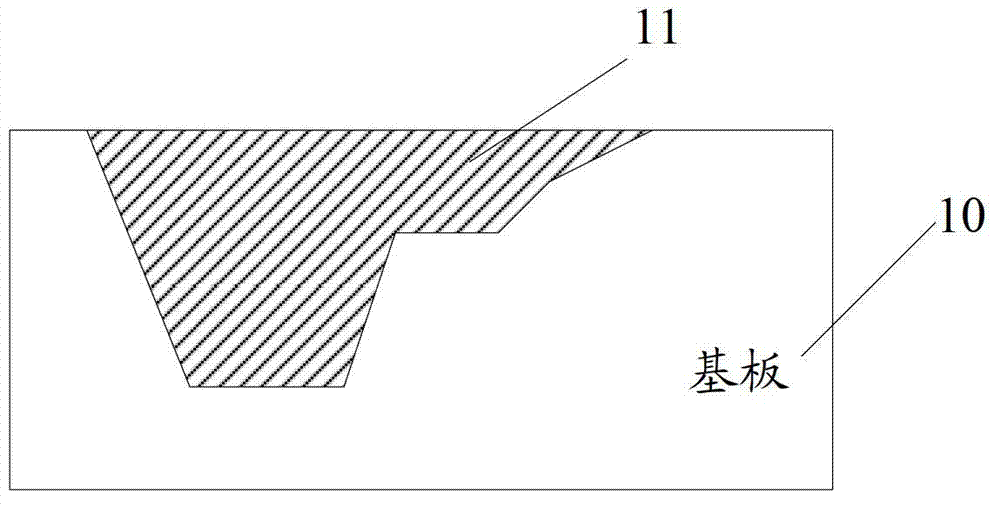

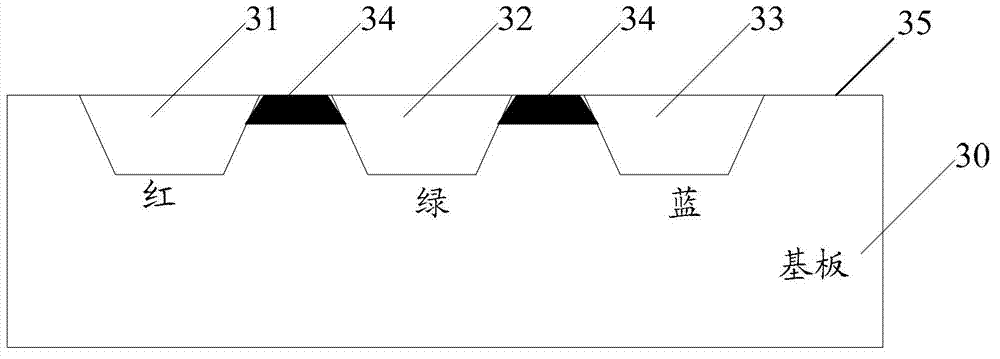

Liquid crystal display substrate, manufacturing method thereof, liquid crystal panel and display device

InactiveCN102789089AImprove planarizationImprove qualitySemiconductor/solid-state device manufacturingPhotosensitive material processingLiquid-crystal displayDisplay device

The embodiment of the invention provides a liquid crystal display substrate and relates to the technical field of the liquid crystal display. According to the invention, the surface of the liquid crystal display substrate can achieve higher flat degree. The liquid crystal display substrate comprises a substrate and display parts, wherein a groove is arranged on the substrate; the display parts are formed in the groove; upper surfaces of the display parts formed at the top end in the groove are horizontal or in the same horizontal plane; when a single display part is formed at the top end in the groove, the upper surface of the single display part is horizontal; and when a plurality of display parts are formed at the top end in the groove, the upper surfaces of the display parts are in the same horizontal plane. The embodiment of the invention also provides a manufacturing method of the liquid crystal display substrate, a corresponding liquid crystal panel and a display device.

Owner:BOE TECH GRP CO LTD

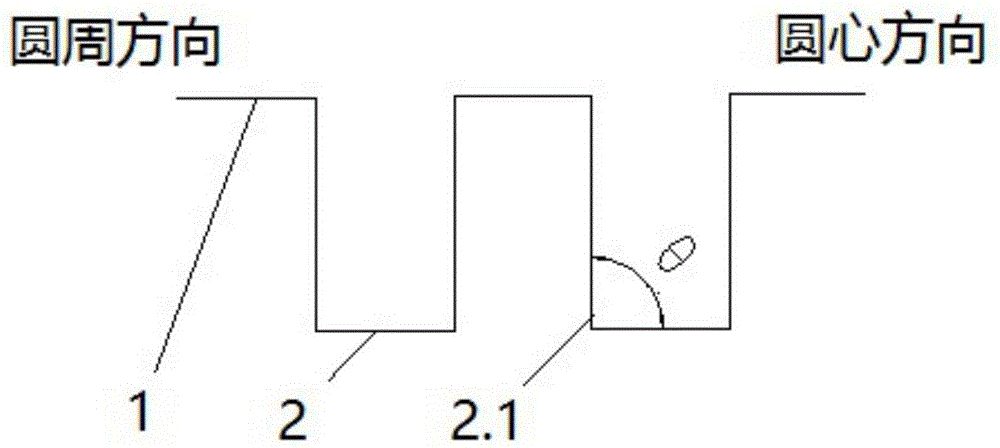

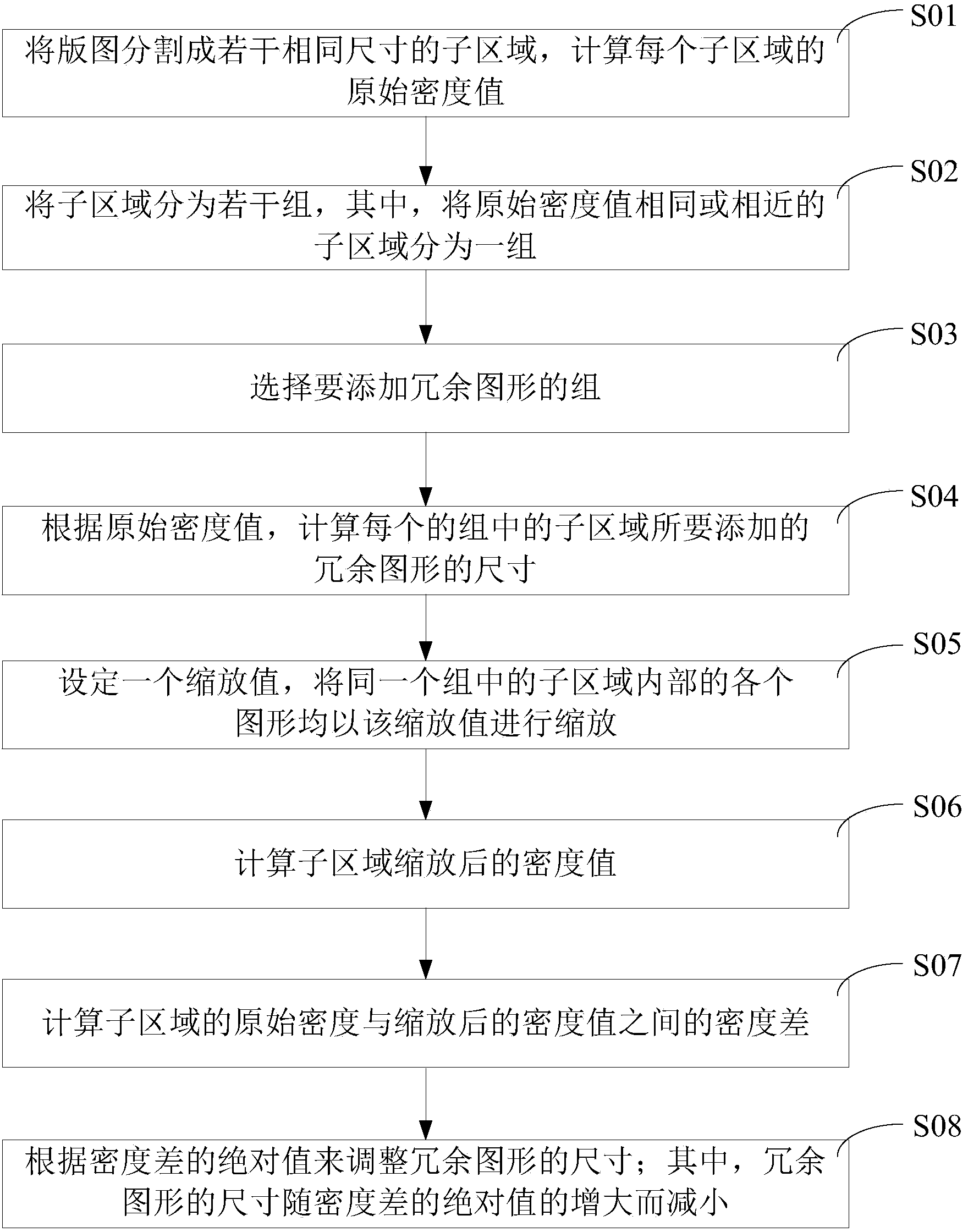

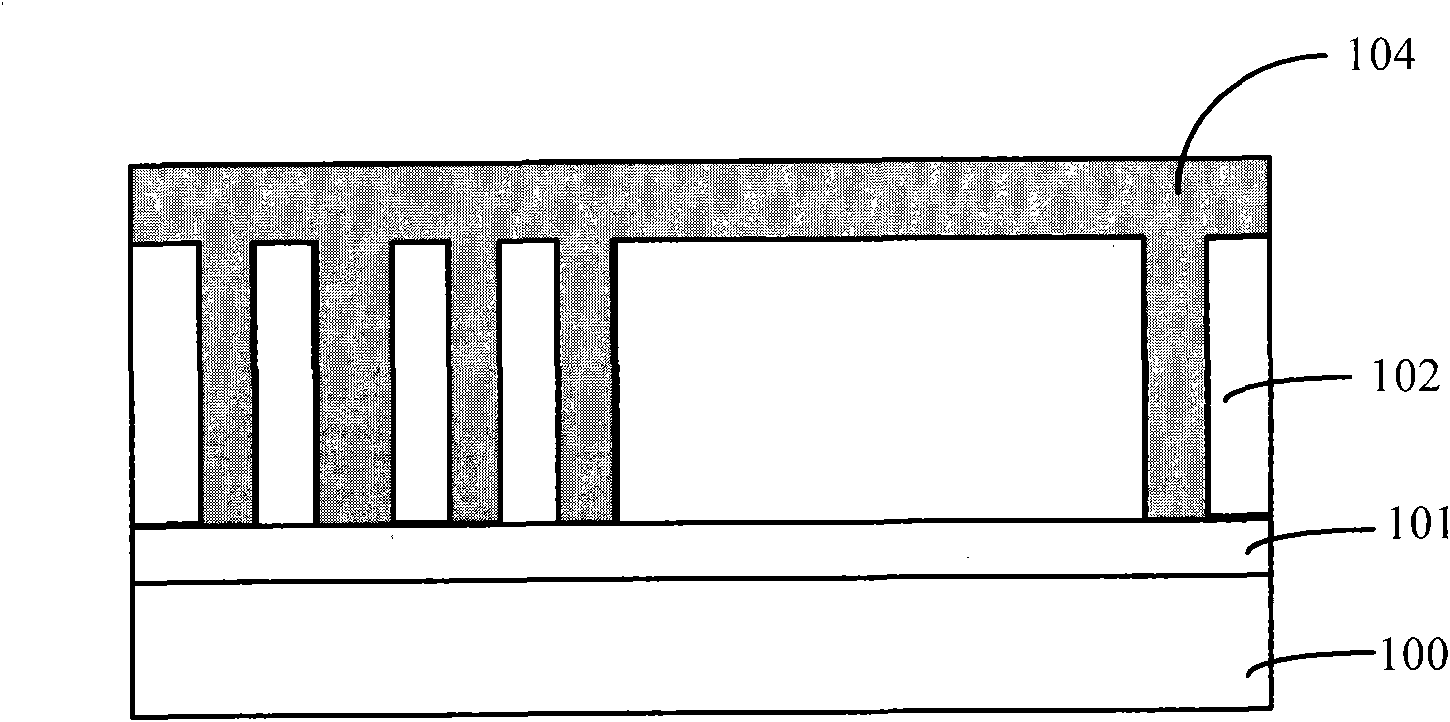

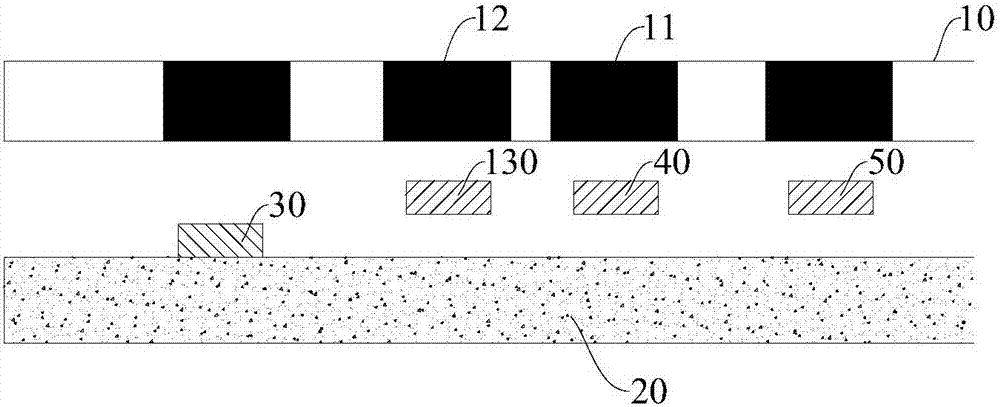

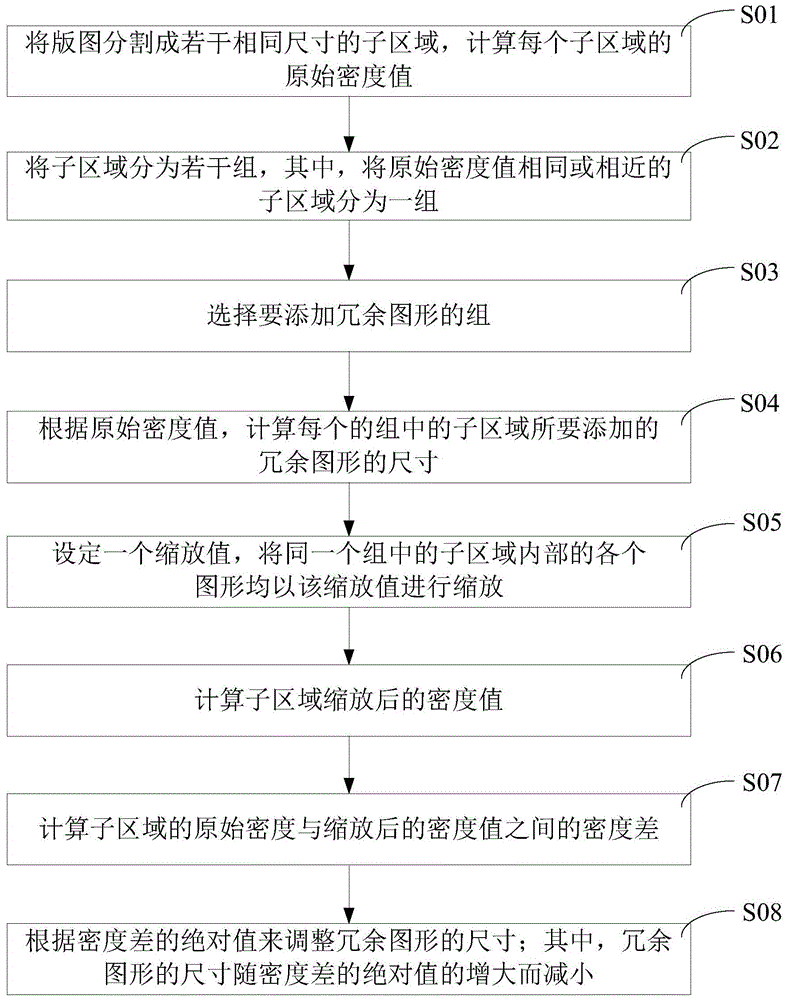

Method for adding redundant graphics

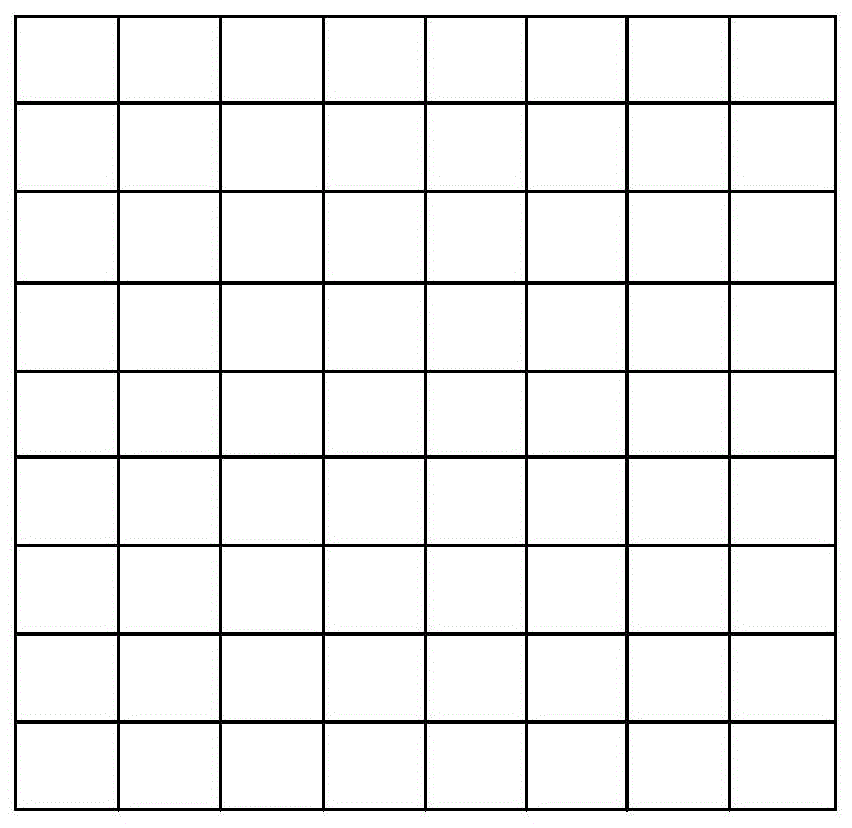

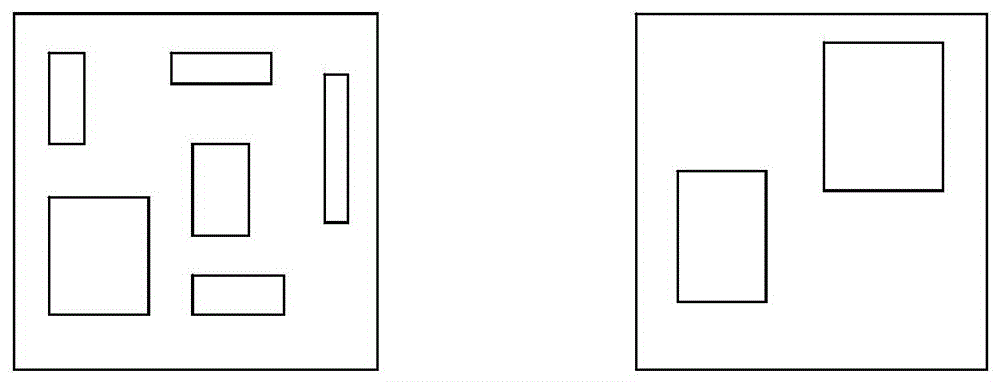

ActiveCN103855044AReduce density distribution varianceUniform density distributionSemiconductor/solid-state device manufacturingGraphicsDensity distribution

The invention provides a method for adding redundant graphics. The method comprises the following steps: dividing a domain into a plurality of subdomains in the same size and calculating an original density value of each subdomain; dividing the subdomains into a plurality of groups and taking the subdomains with the same or similar original density values as one group; selecting the groups in which the redundant graphics need to be added; calculating the sizes of the redundant graphics needing to be added in the subdomains of each group according to the density values; setting a scaling value and scaling each of the redundant graphics in the subdomains of the same group according to the scaling value; calculating the scaled density values of the subdomains; calculating a density difference of the original density values and the scaled density values of the subdomains; and adjusting the sizes of the redundant graphics according to an absolute value of the density difference, wherein the sizes of the redundant graphics are decreased along with the increasing of the absolute value of the density difference. According to the method, the homogeneous density distribution of wafers is ensured; the density distribution difference of the domain and the wafers is reduced, so that the flatness degree is improved.

Owner:SHANGHAI HUALI MICROELECTRONICS CORP

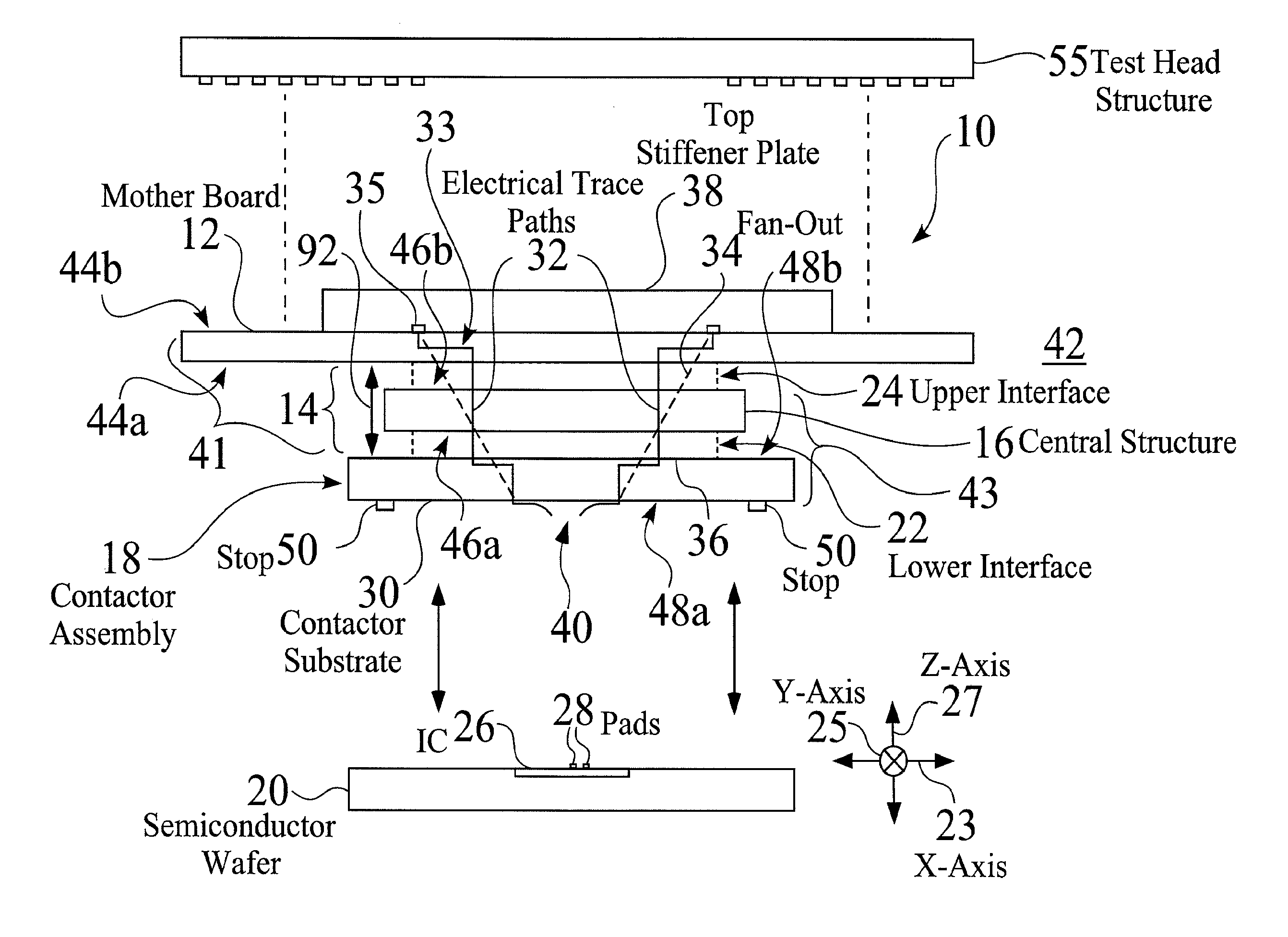

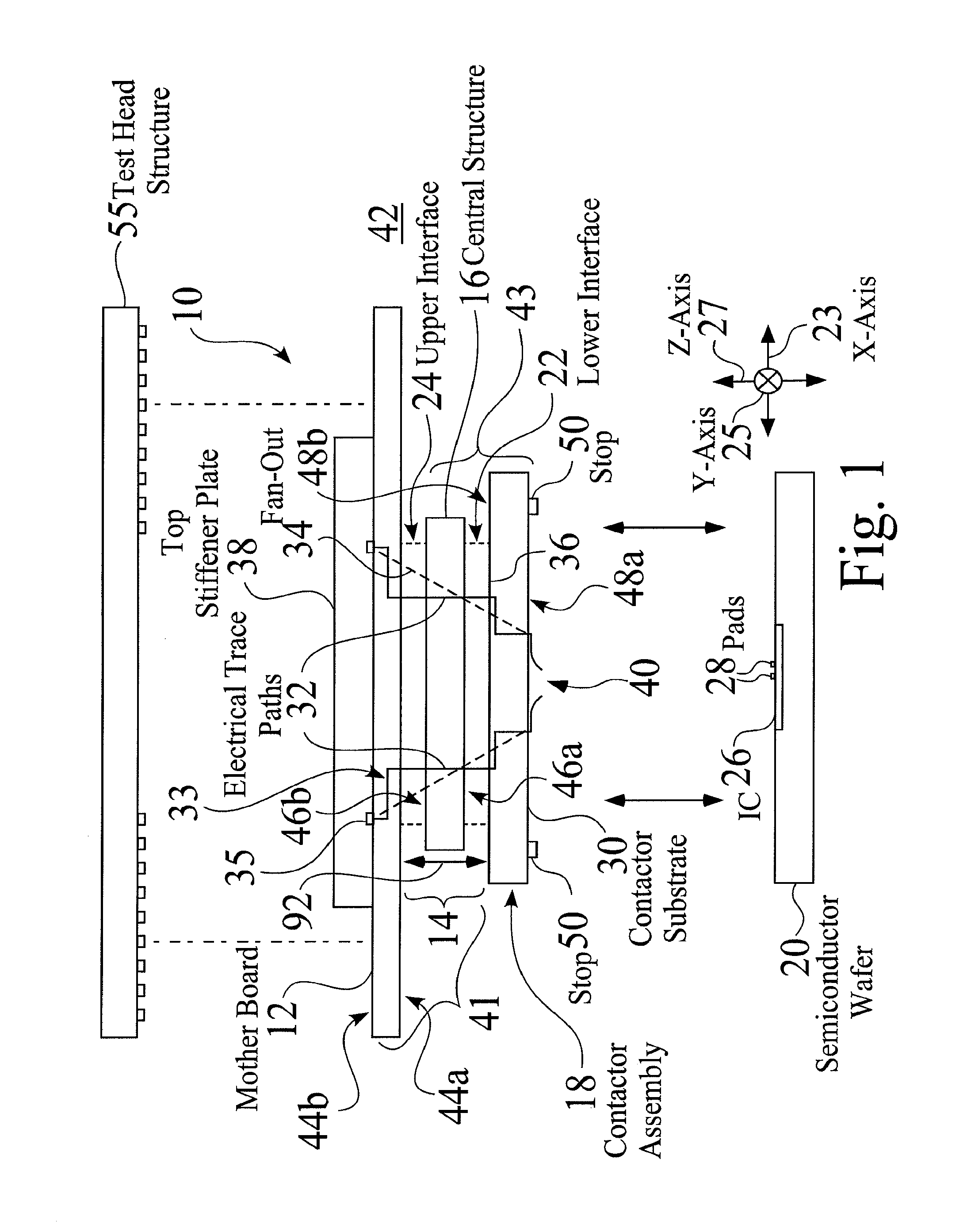

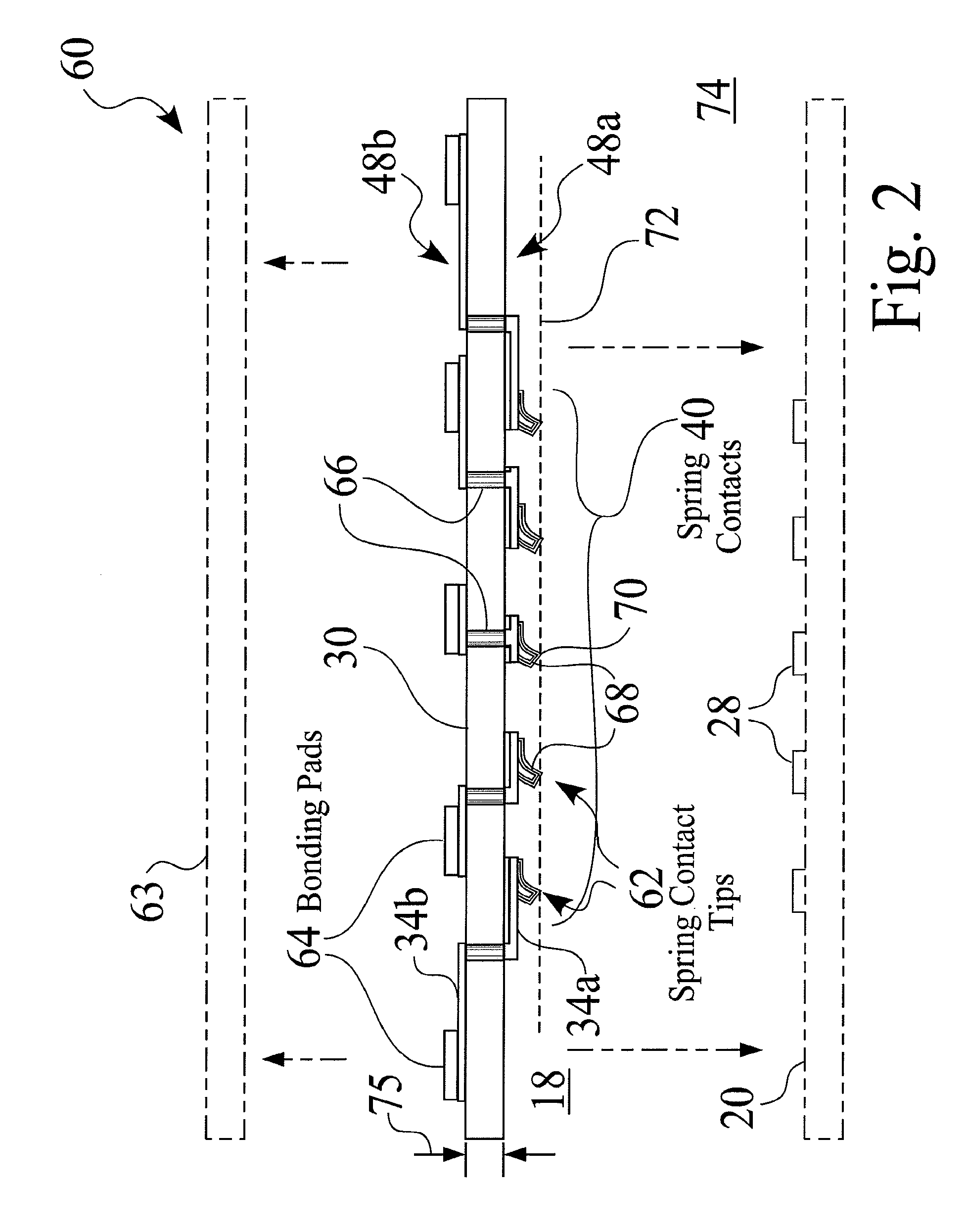

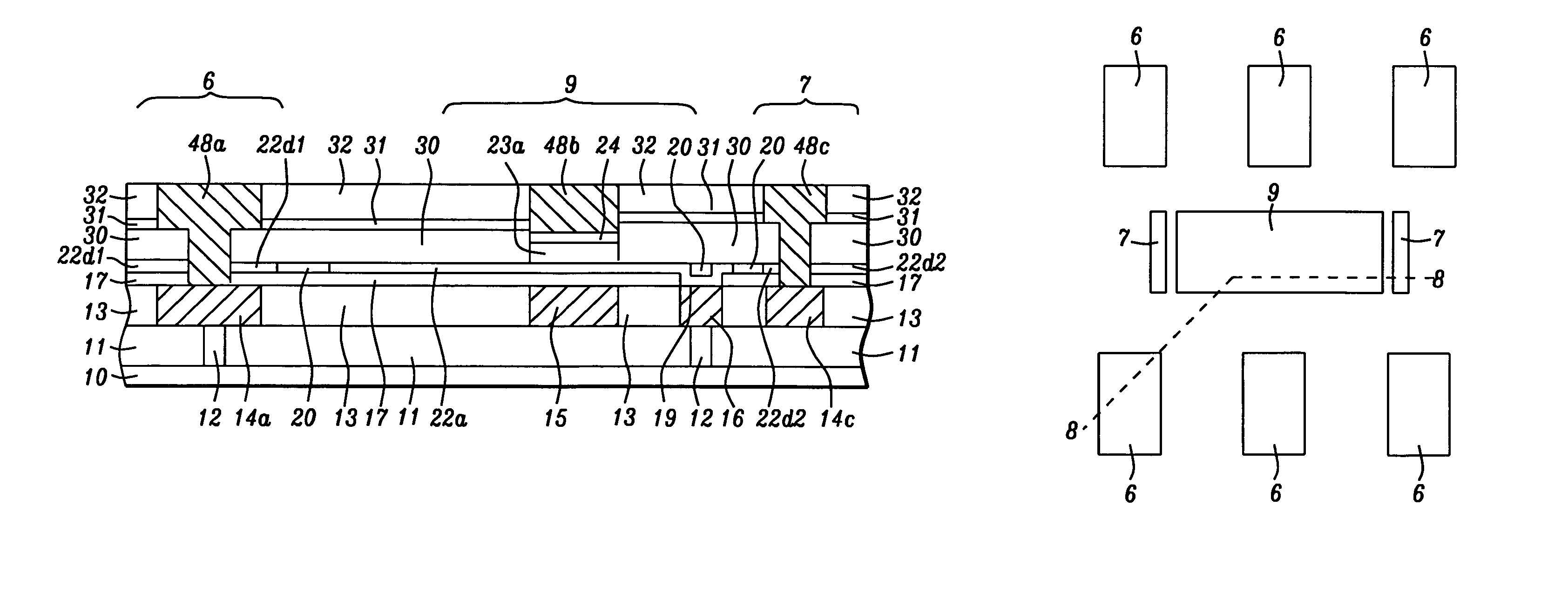

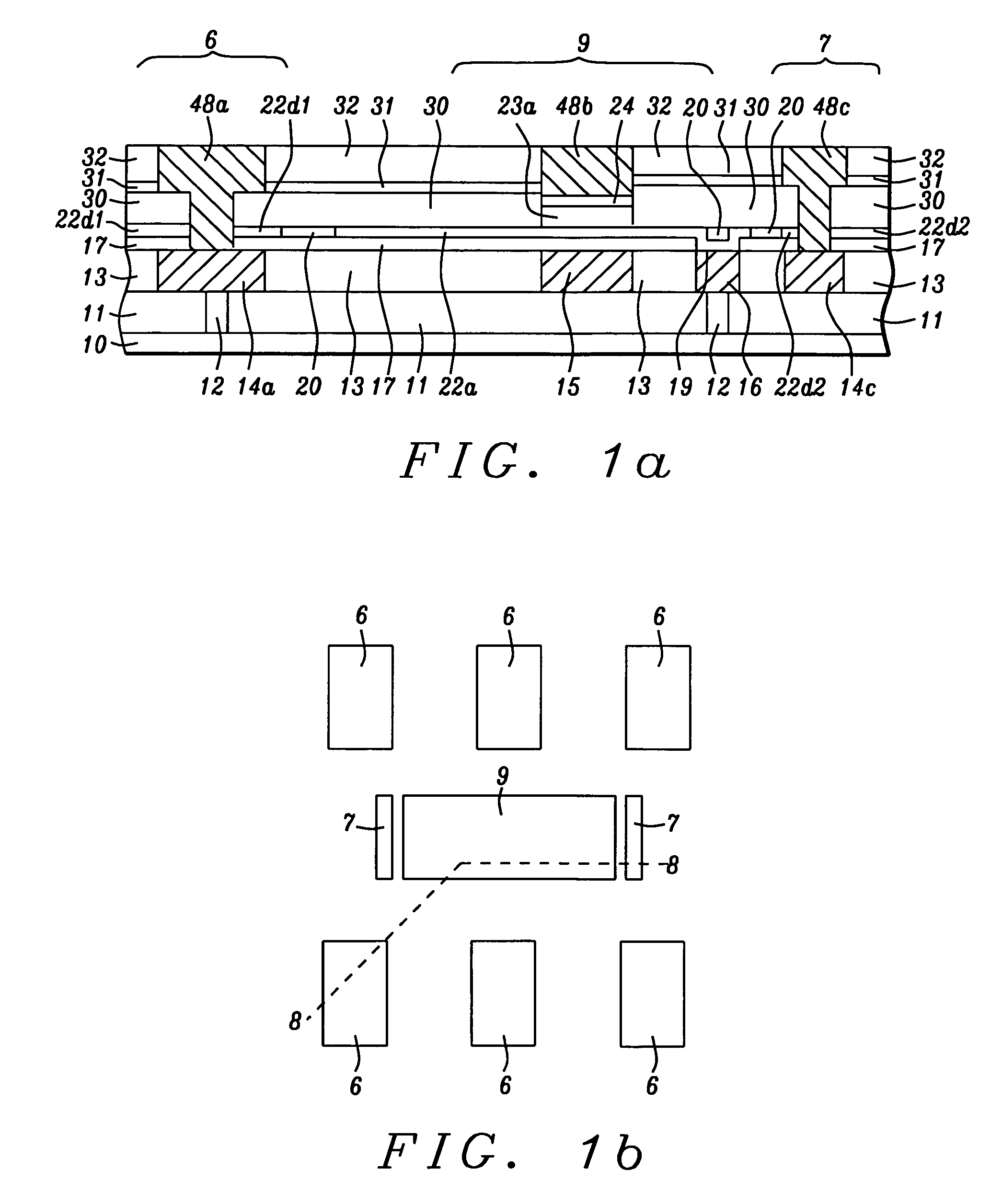

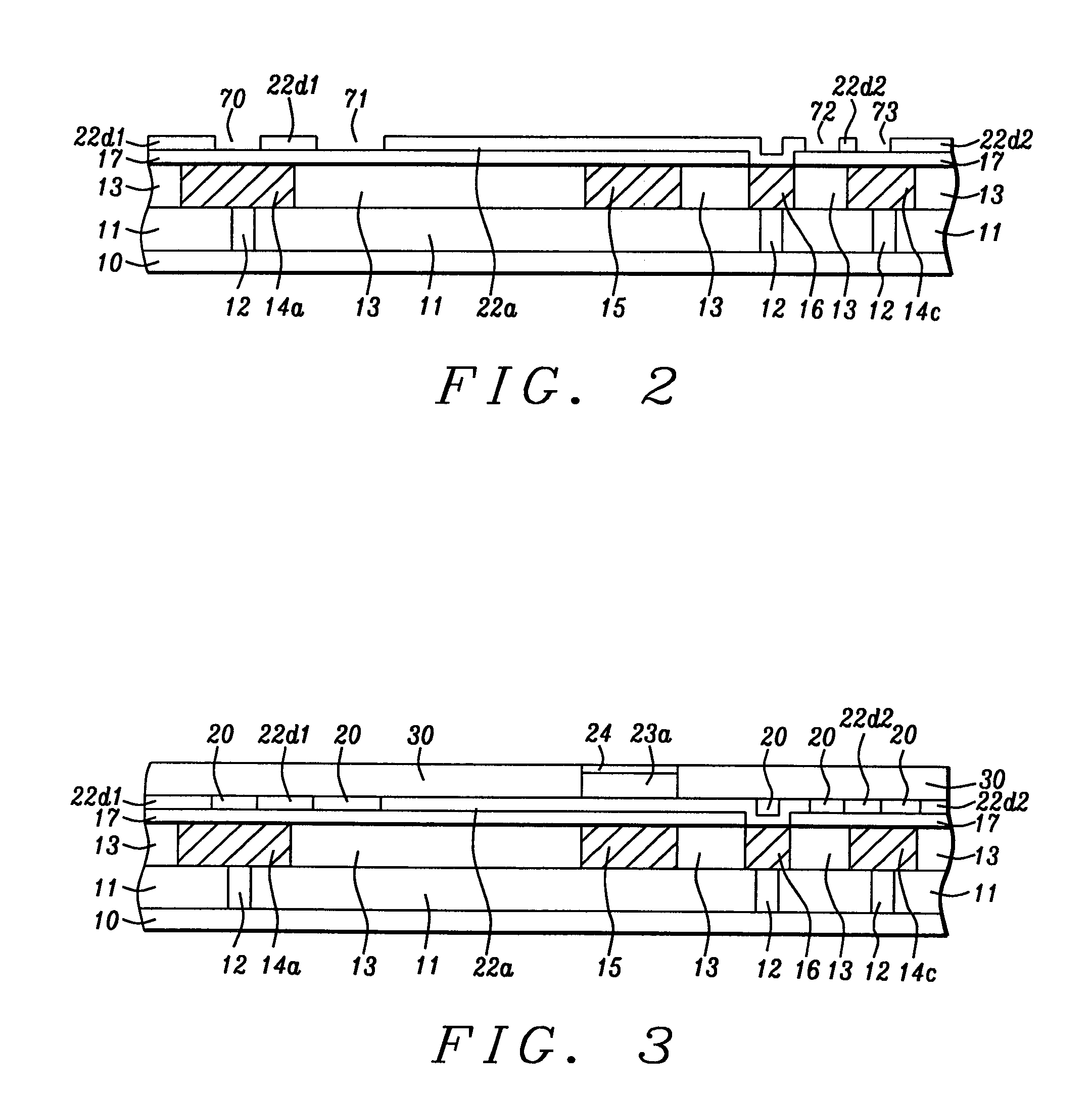

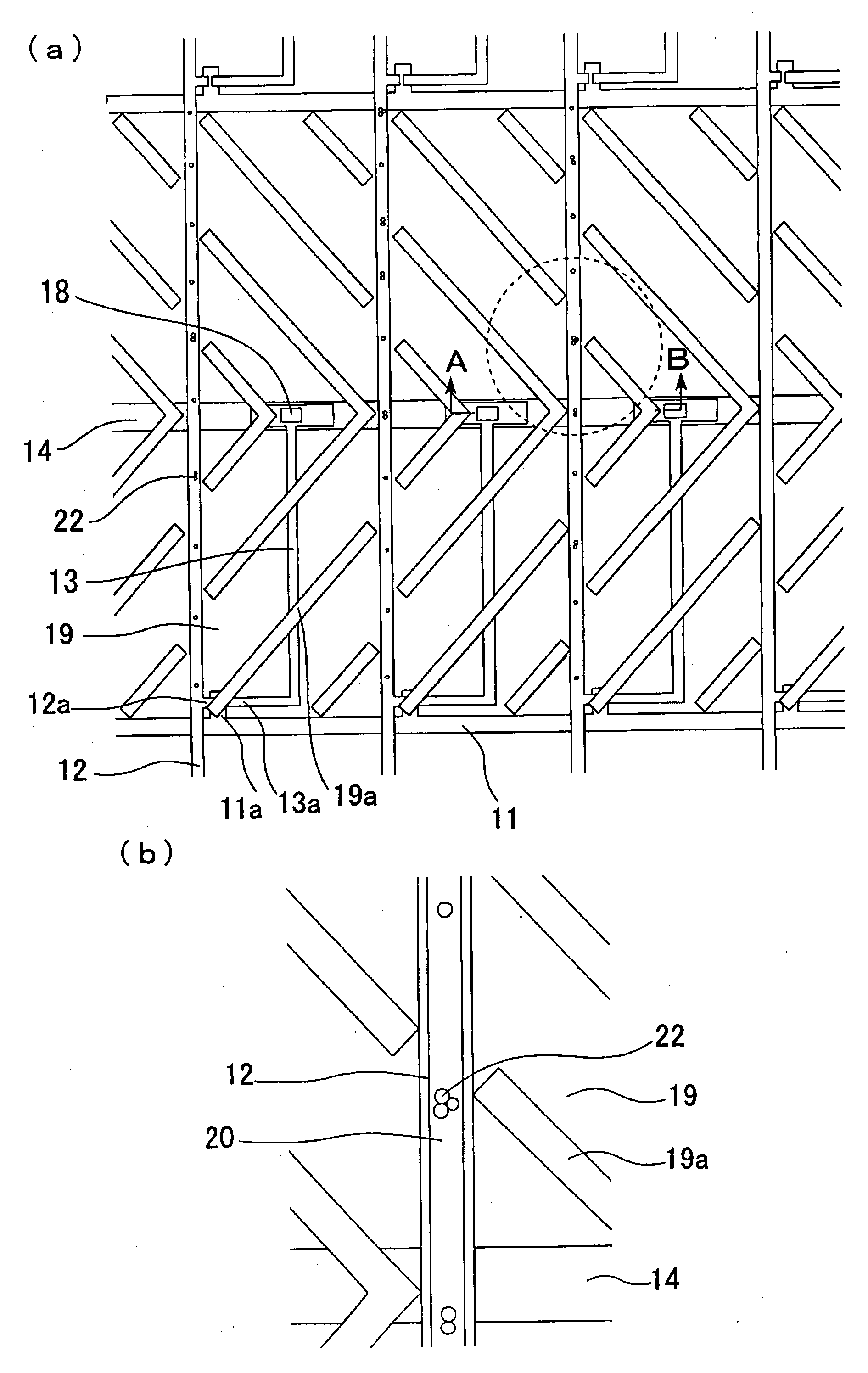

Construction structures and manufacturing processes for integrated circuit wafer probe card assemblies

InactiveUS20120023730A1Improve methodSimple structureElectrical measurement instrument detailsManufacture of electrical instrumentsProbe cardManufacturing technology

Enhanced microfabricated spring contact structures and associated methods, e.g. such as for electrical contactors and interposers, comprise improvements to spring structures that extend from the substrate surface, and / or improvements to structures on or within the support substrate. Improved spring structures and processes comprise embodiments having selectively formed and etched, coated and / or plated regions, which are optionally further processed through planarization and / or annealment. Enhanced solder connections and associated processes provide a gap between substrates for componentry, and or improved manufacturing techniques using distributed spacers. Enhanced probe card assembly structures and processes provide improved planarization adjustment and thermal stability.

Owner:CHONG FU CHIUNG +6

Bottom electrode mask design for ultra-thin interlayer dielectric approach in MRAM device fabrication

ActiveUS7804706B2Minimize delaminationImprove thickness uniformityNanotechSolid-state devicesElectricityEngineering

A bottom electrode (BE) layout is disclosed that has four distinct sections repeated in a plurality of device blocks and is used to pattern a BE layer in a MRAM. A device section includes BE shapes and dummy BE shapes with essentially the same shape and size and covering a substantial portion of substrate. There is a via in a plurality of dummy BE shapes where each via will be aligned over a WL pad. A second bonding pad section comprises an opaque region having a plurality of vias. The remaining two sections relate to open field regions in the MRAM. The third section has a plurality of dummy BE shapes with a first area size. The fourth section has a plurality of dummy BE shapes with a second area size greater than the first area size to provide more complete BE coverage of an underlying etch stop ILD layer.

Owner:TAIWAN SEMICON MFG CO LTD

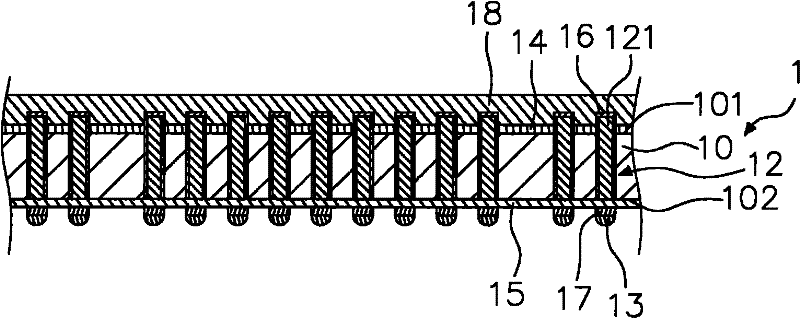

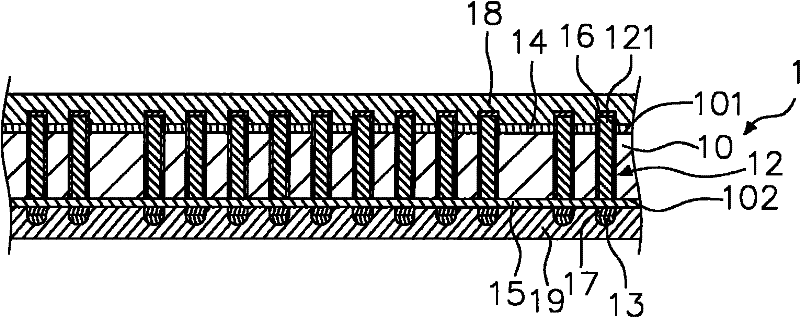

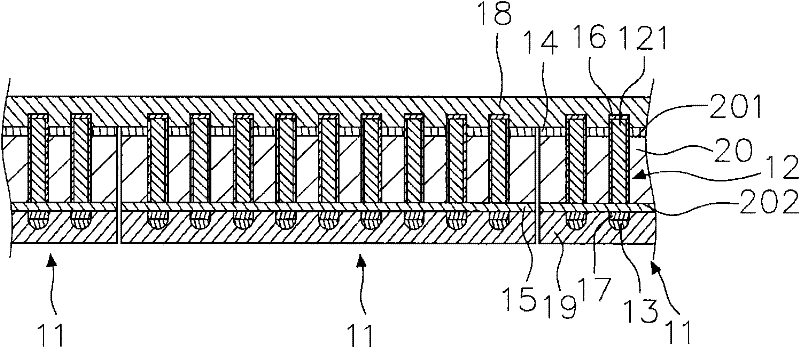

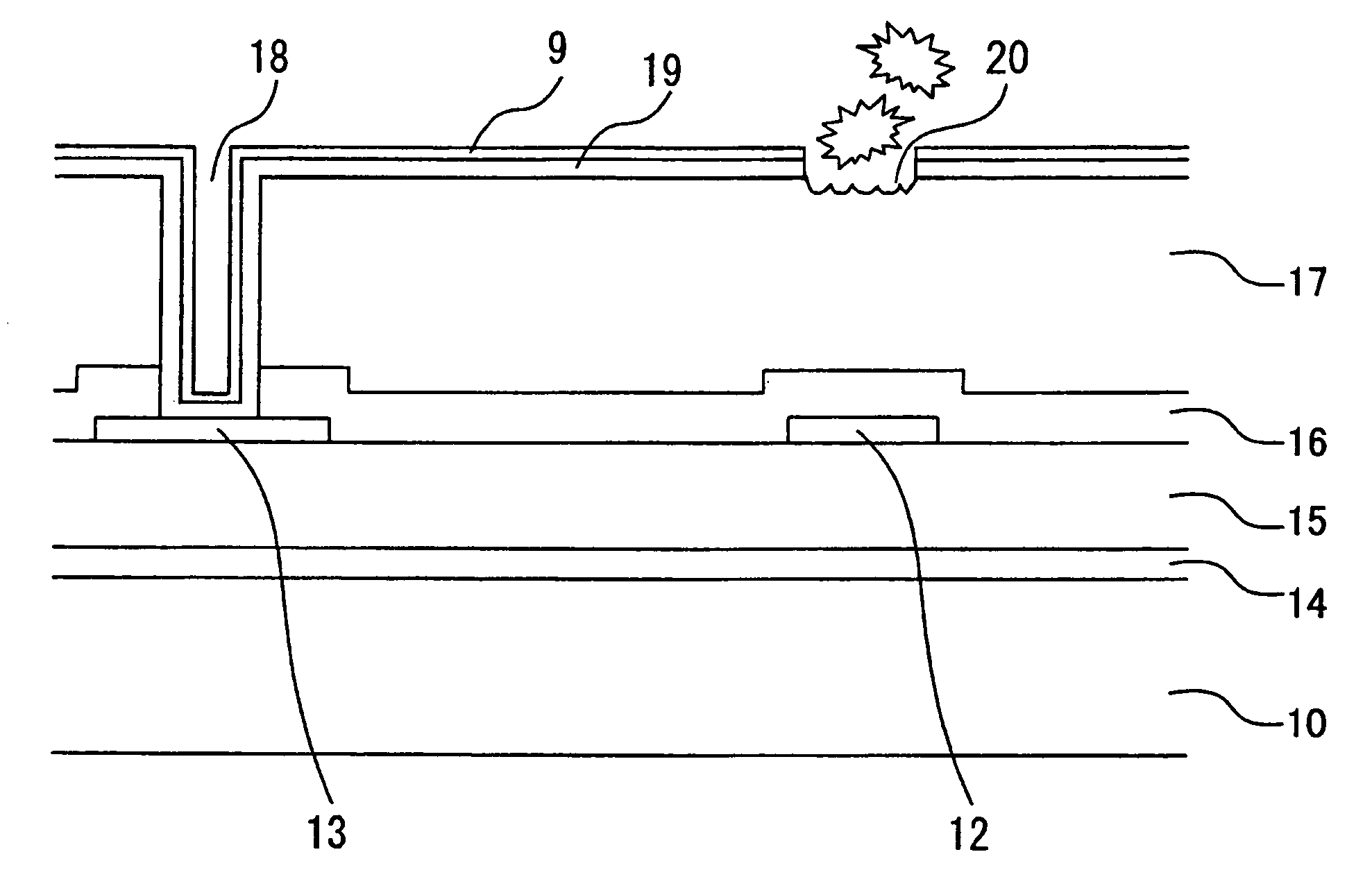

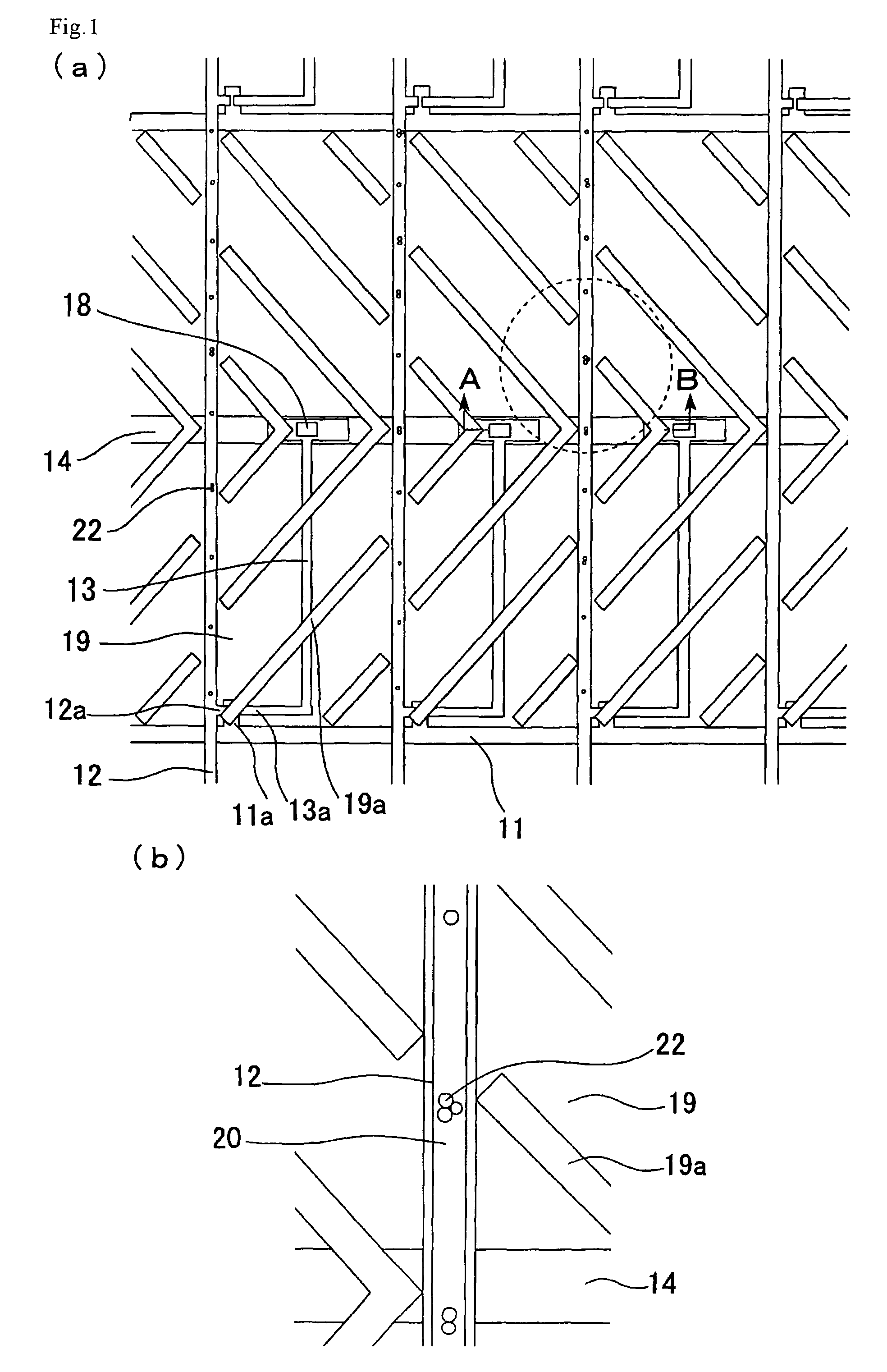

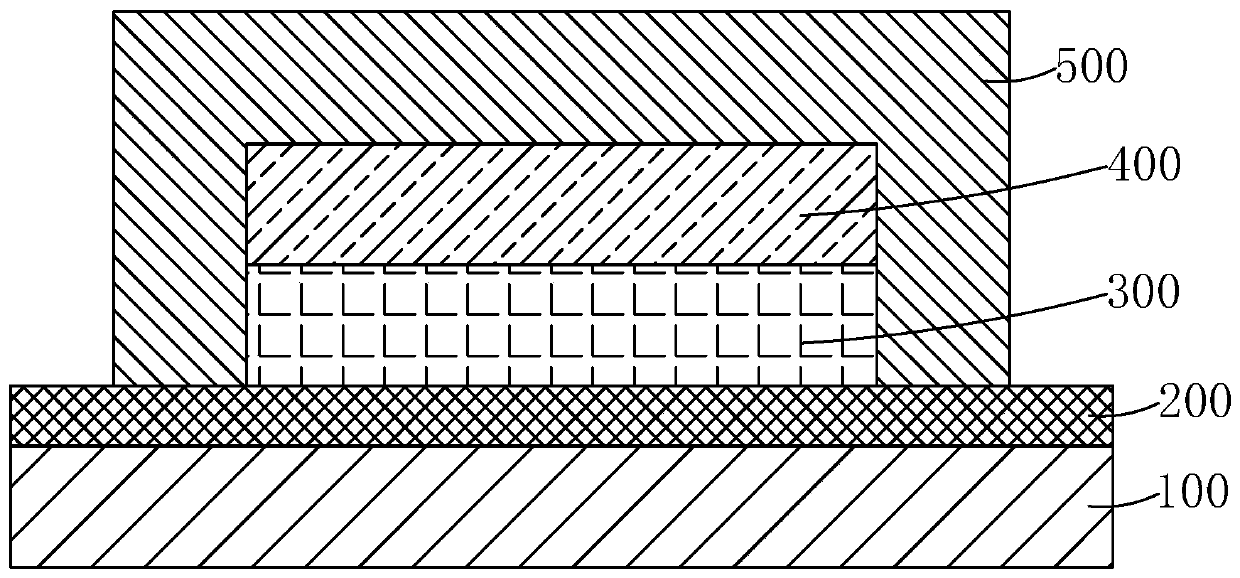

Multilayer Substrate

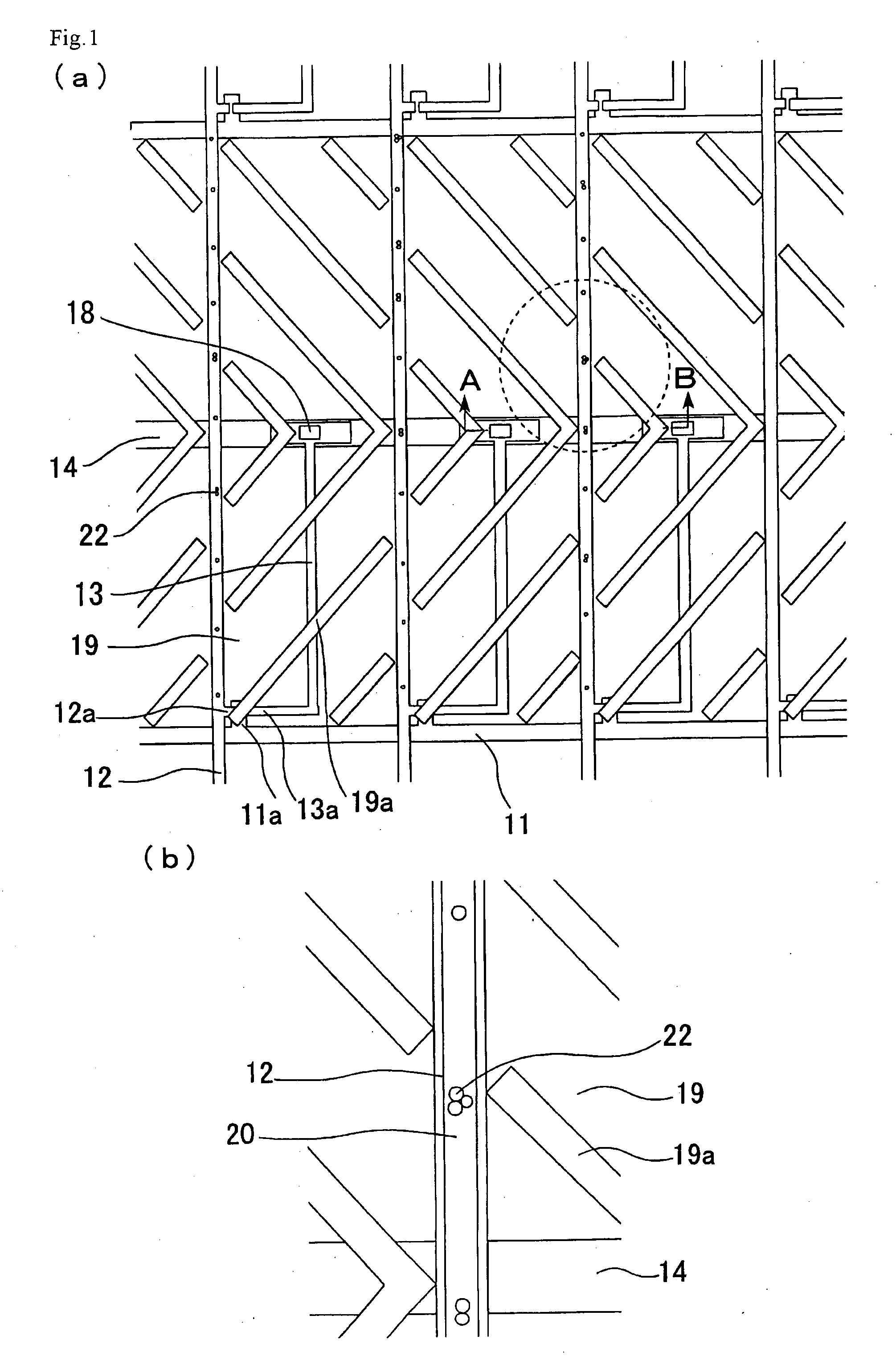

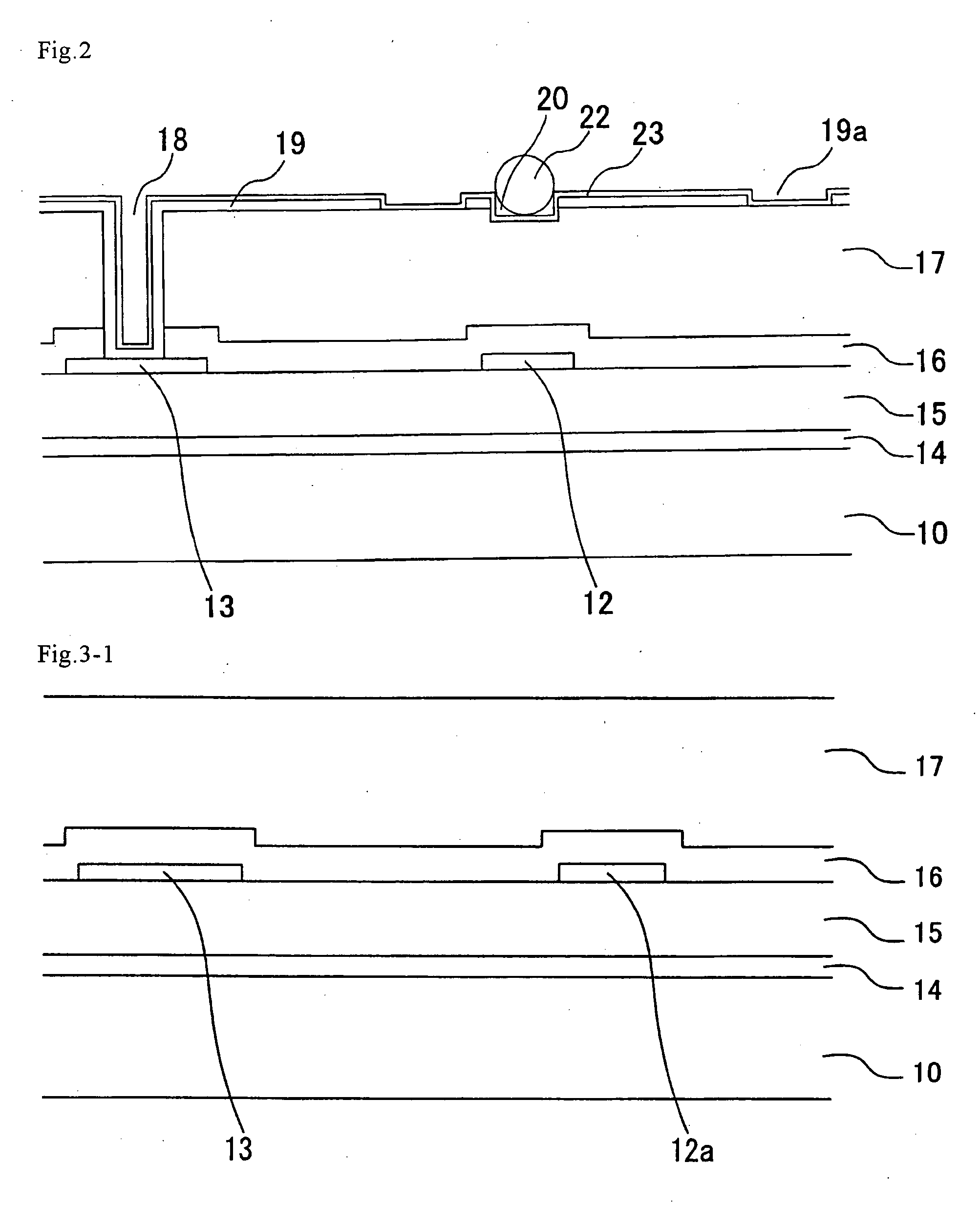

InactiveUS20080137015A1Increase opening ratioImprove planarizationSemiconductor/solid-state device manufacturingNon-linear opticsProduction rateLiquid-crystal display

The present invention provides: a multilayer substrate in which a spacer is selectively disposed in a non-display region without reduction in display quality or productivity of a liquid crystal display device; a production method thereof; and a liquid crystal display panel and a liquid crystal display device each using the multilayer substrate or the production method thereof. The multilayer substrate of the present invention is a multilayer substrate comprising a resin interlayer film and an electrode on a substrate in this order, wherein the multilayer substrate has a depression structure including the resin interlayer film in a surface layer, or a depression structure having a rough bottom surface on the resin interlayer film.

Owner:SHARP KK

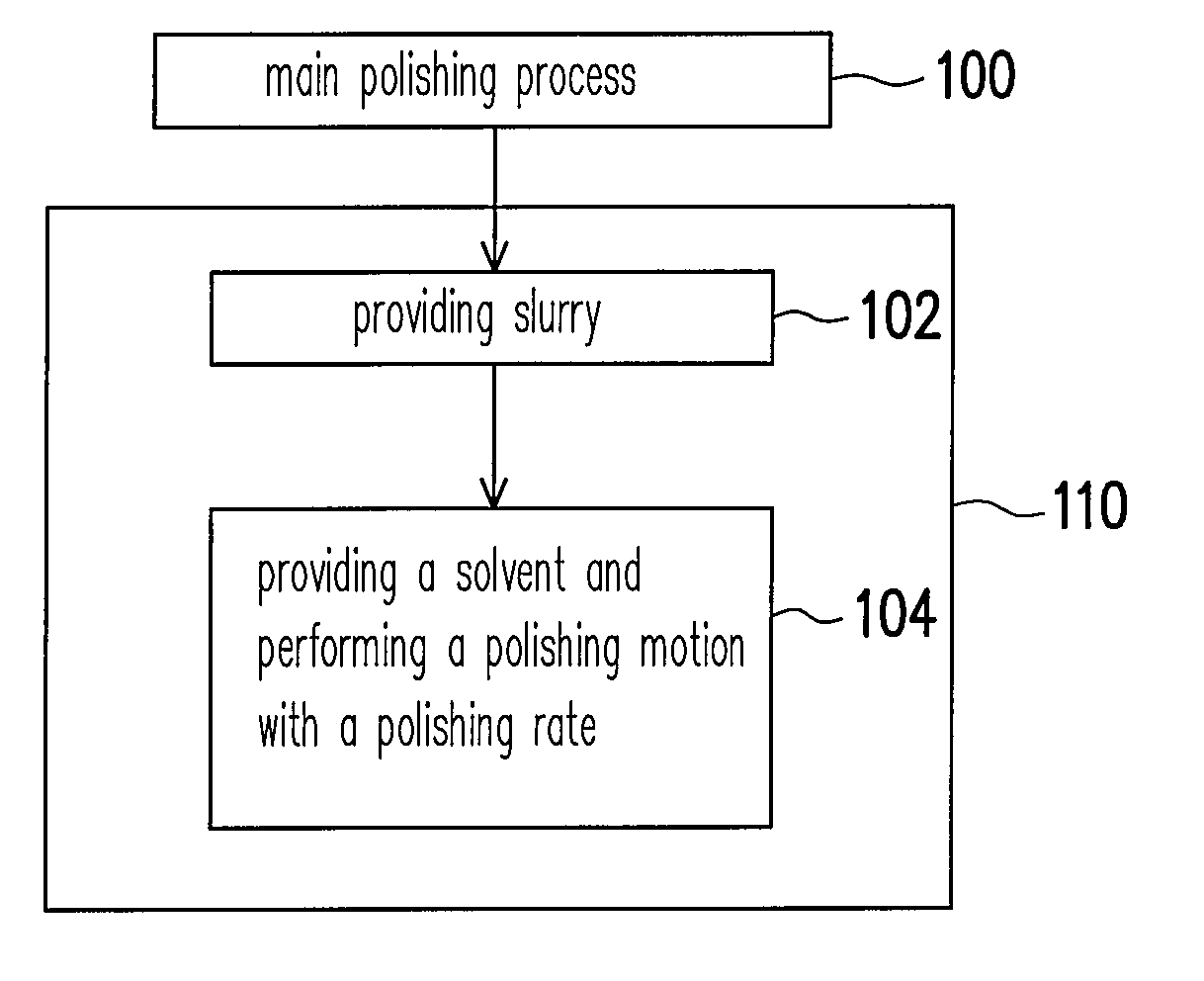

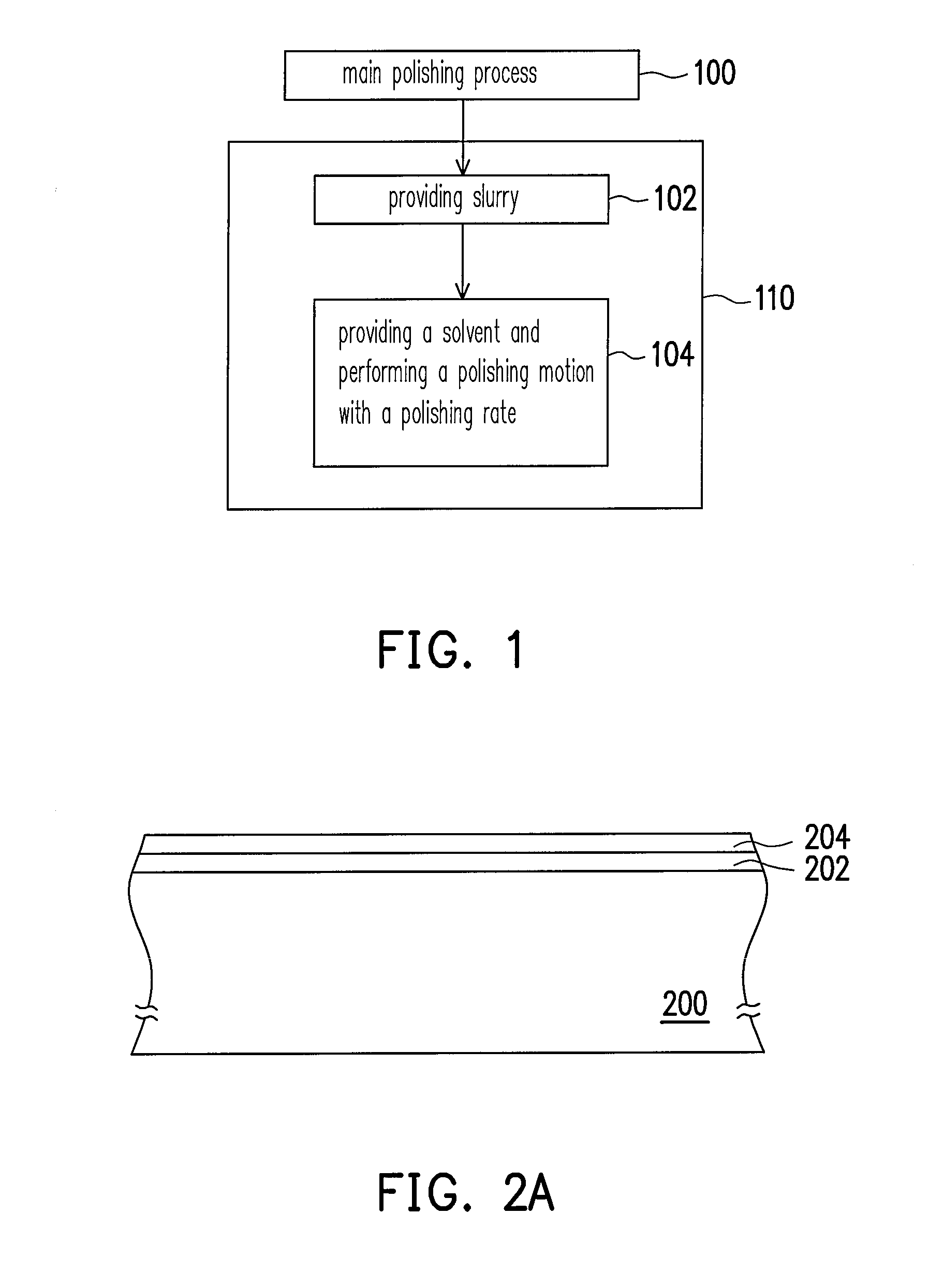

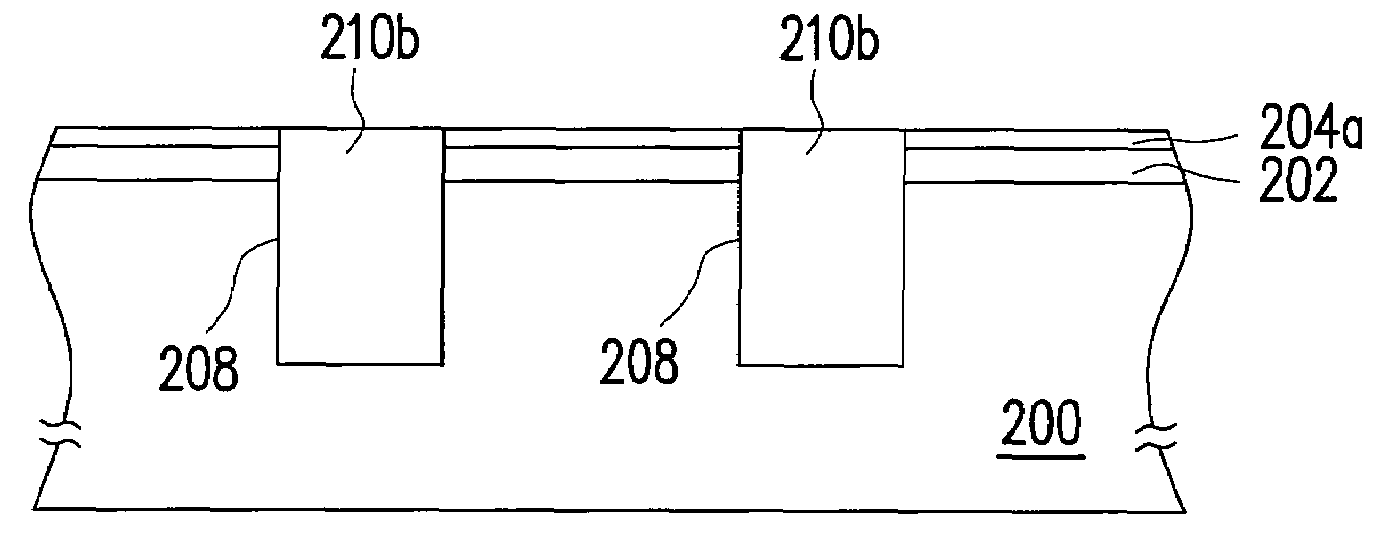

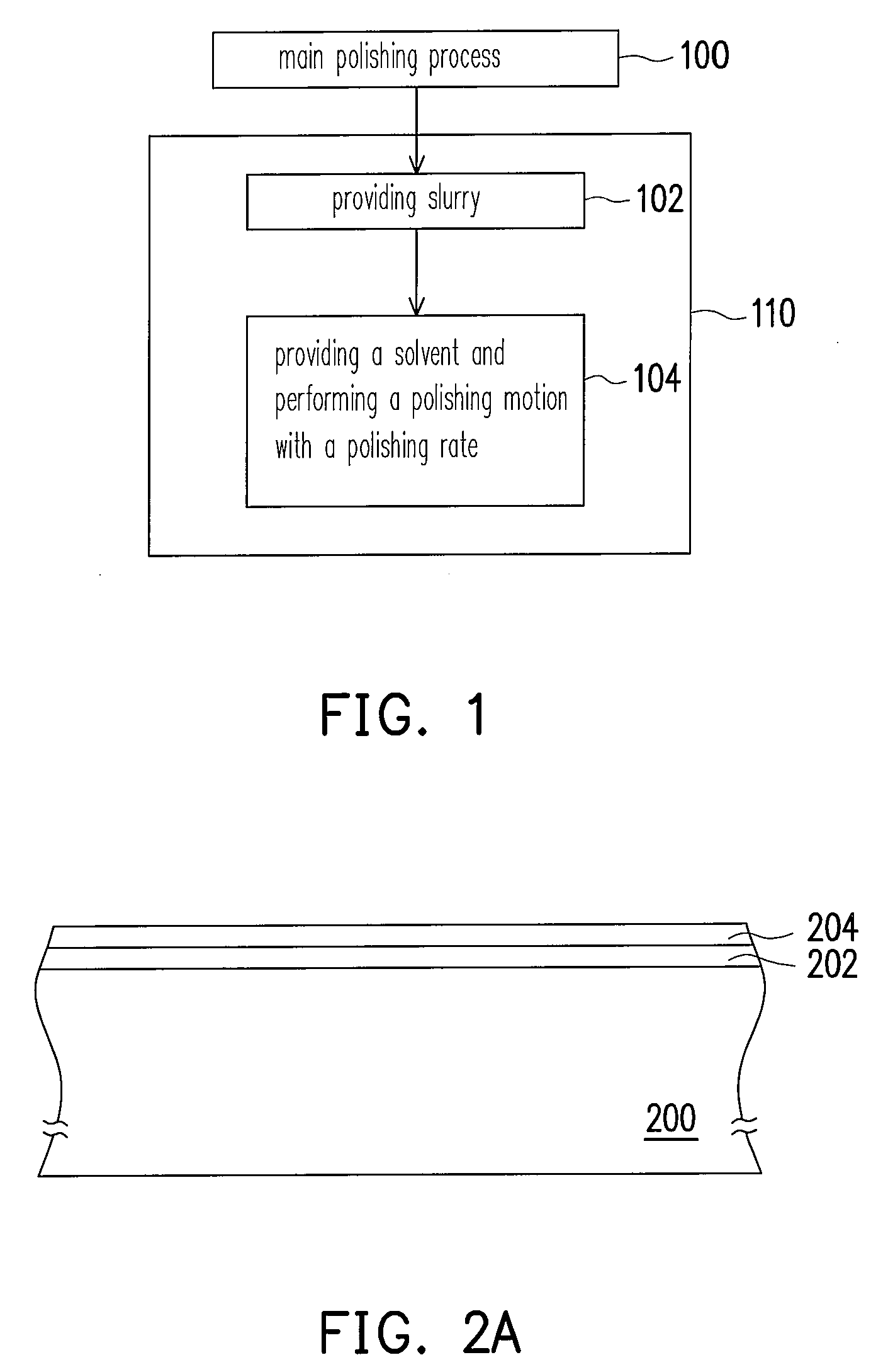

Complex chemical mechanical polishing and method for manufacturing shallow trench isolation structure

InactiveUS20080045014A1Uniform surfaceReliable manufacturingSemiconductor/solid-state device manufacturingSlurryProcess engineering

A complex chemical mechanical polishing process for planarizing a structure. The process comprises steps of performing a main polishing process with a first polishing rate, wherein a slurry is provided. An assisted polishing process is then performed to planarizing the structure. The assisted polishing process comprises steps of providing the slurry in a first period of time and then providing a solvent and performing a polishing motion of a second polishing rate in a second period of time. The second polishing rate is slower than the first polishing rate.

Owner:UNITED MICROELECTRONICS CORP

Forming method of dual-damascene structure

InactiveCN102097361AImprove planarizationImprove filling efficiencySemiconductor/solid-state device manufacturingInter layerOptoelectronics

The invention relates to a forming method of a dual-damascene structure, comprising the following steps of: providing a substrate, wherein the surface of the substrate is provided with conductive areas, an inter-layer dielectric layer is formed on the substrate, through holes are formed in the inter-layer dielectric layer, and the positions of the through holes correspond to the positions of the conductive areas; forming a first anti-reflection layer on the inter-layer dielectric layer and in the through holes, and filling the contact through holes; forming a second anti-reflection layer on the first anti-reflection layer, wherein the viscosity of the second anti-reflection layer is larger than that of the first anti-reflection layer; carrying out groove imaging on the second anti-reflection layer, the first anti-reflection layer and the inter-layer dielectric layer, etching the second anti-reflection layer, the first anti-reflection and partial inter-layer dielectric layer to form a groove, wherein the bottom of the groove is communicated with at least one through hole; filling a conducting material in the groove and the through holes; and flattening the conducting material to form the dual-damascene structure.

Owner:SEMICON MFG INT (SHANGHAI) CORP +1

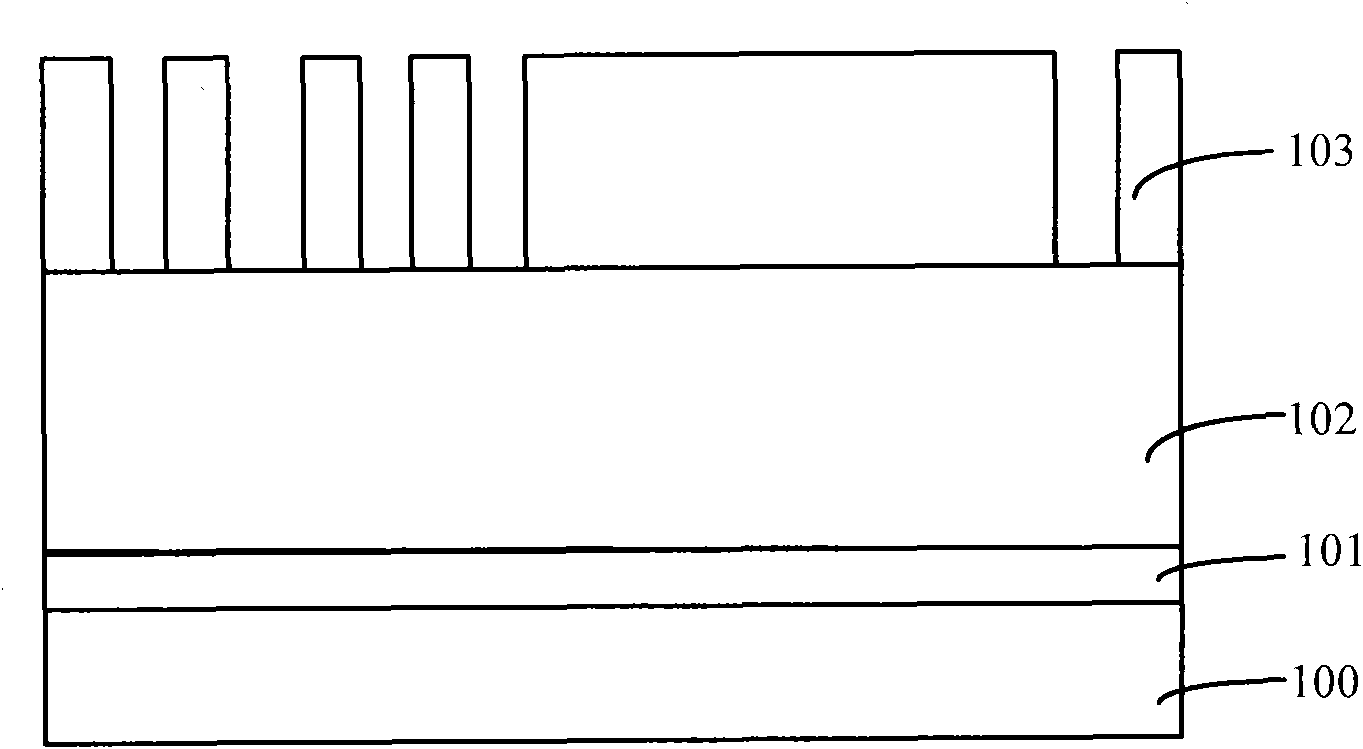

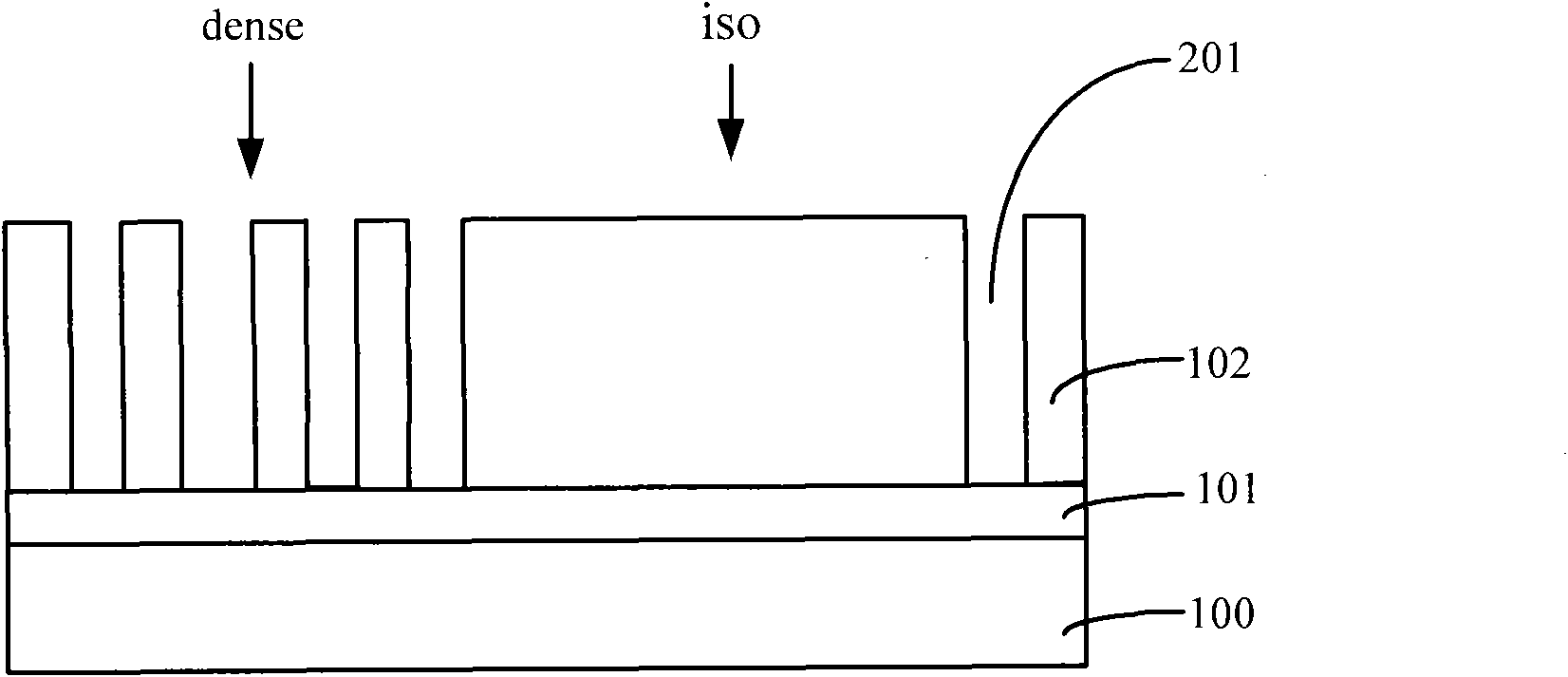

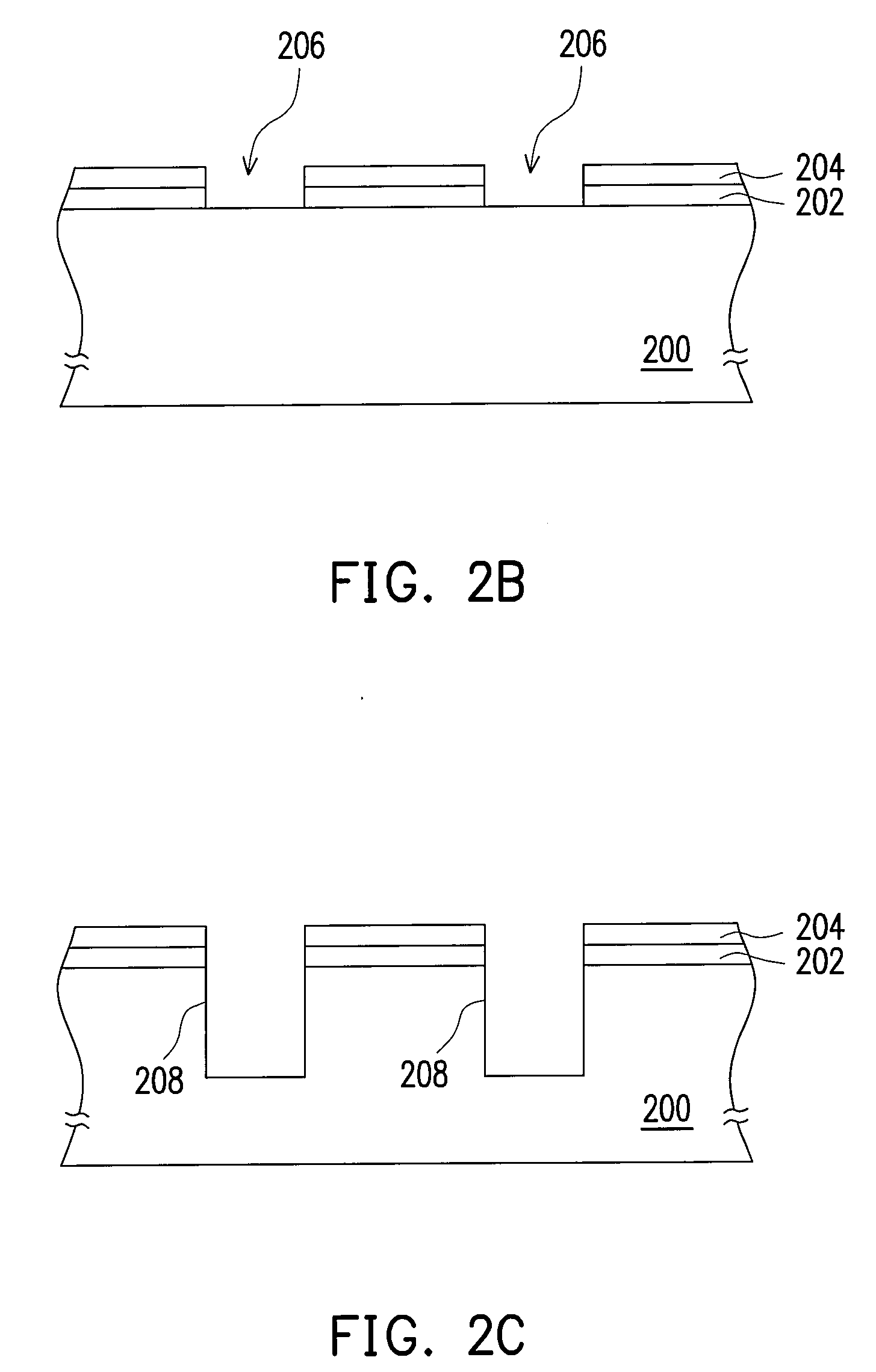

Method for manufacturing shallow trench isolation structure

InactiveUS20080305610A1Avoid problemsUniform surfaceSemiconductor/solid-state device manufacturingEngineeringSlurry

A method of forming a shallow trench isolation structure includes steps of providing a substrate having a patterned mask layer formed thereon, wherein a trench is located in the substrate and the patterned mask layer exposes the trench. Thereafter, a dielectric layer is formed over the substrate to fill the trench. Then, a main polishing process with a first polishing rate is performed to remove a portion of the dielectric layer. An assisted polishing process is performed to remove the dielectric layer and a portion of the mask layer. The assisted polishing process includes steps of providing a slurry in a first period of time and then providing a solvent and performing a polishing motion of a second polishing rate in a second period of time. The second polishing rate is slower than the first polishing rate. Further, the mask layer is removed.

Owner:UNITED MICROELECTRONICS CORP

Array substrate and preparation method therefor and display apparatus

InactiveCN107195640AIncrease opening ratioIncrease brightnessSolid-state devicesSemiconductor/solid-state device manufacturingOptoelectronicsAperture ratio

The invention provides an array substrate and a preparation method therefor and a display apparatus. The array substrate comprises an insulating layer; the insulating layer comprises a transparent part and a light shielding part; and the projection of the light shielding part on the substrate of the array substrate covers the projections of a gate line, a source, a drain and a data line on the substrate of the array substrate. Therefore, the light shielding part can replace a conventional black matrix, so that product structure can be simplified and the product thickness can be reduced; and in addition, the dimension of the light shielding part can be smaller than that of the conventional black matrix, so that aperture ratio can be improved.

Owner:BOE TECH GRP CO LTD +1

Stack type package structure and manufacture method thereof

ActiveCN102054787AIncreasing the thicknessImprove planarizationSemiconductor/solid-state device detailsSolid-state devicesEngineeringCrystal

The invention relates to a stack type package structure and a manufacture method thereof. The method comprises the steps of: forming and curing a first protective layer for covering a first convex block of a first wafer; cutting the first wafer to form a plurality of first crystal particles; forming a second protective layer for covering a second convex block of a second wafer; absorbing the first crystal particles by using a joint through the first protective layer, jointing the first crystal particles on the second wafer; removing the joint, removing part of the first protective layer; cutting the second wafer to form a plurality of second crystals; forming a third protective layer on a base plate; and jointing the first crystal particles and the second crystal particles on the base plate. Therefore, the first protective layer can protect the first convex block, and the first protective layer has the function of increasing the thickness and flattening so as to be beneficial to the absorption of the first crystal particles.

Owner:ADVANCED SEMICON ENG INC

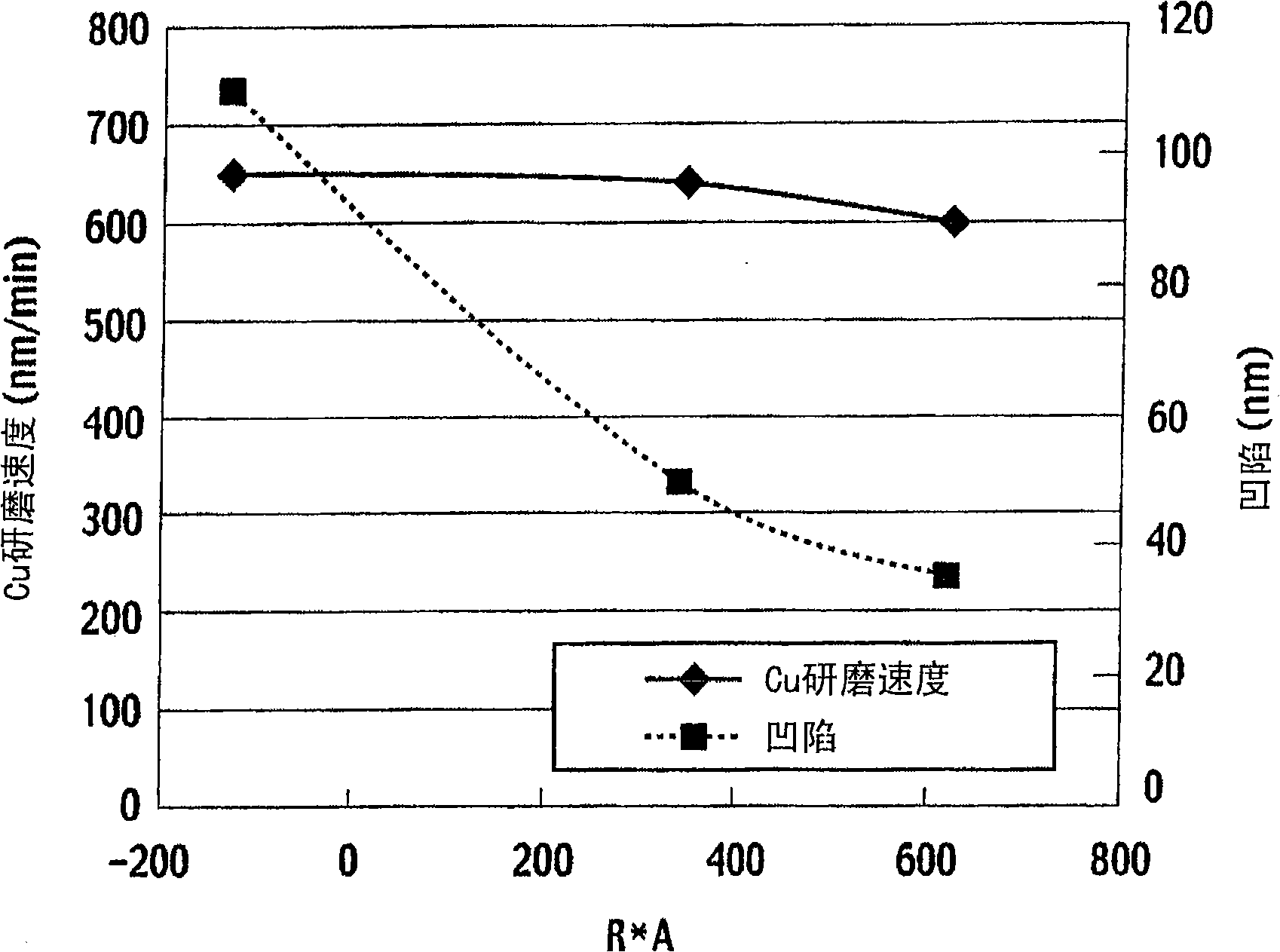

Metal polishing liquid and polishing method using it

ActiveCN101343510AImprove planarizationSemiconductor/solid-state device manufacturingLapping machinesReaction layerChemical composition

The present invention provides a metal-polishing liquid, comprising polishing particles and a chemical component, wherein the polishing particles have charges of surface potential of the same polarity as the charges of surface potential on the reaction layer, adsorption layer or the mixed layer thereof formed by the chemical component on a metal to be polished with the metal-polishing liquid, and a polishing method using the same, that enable to give highly flattened surface at high Cu-polishing speed and enable reduction of the number of the polishing particles remaining on the polished face after polishing.

Owner:RESONAC CORP

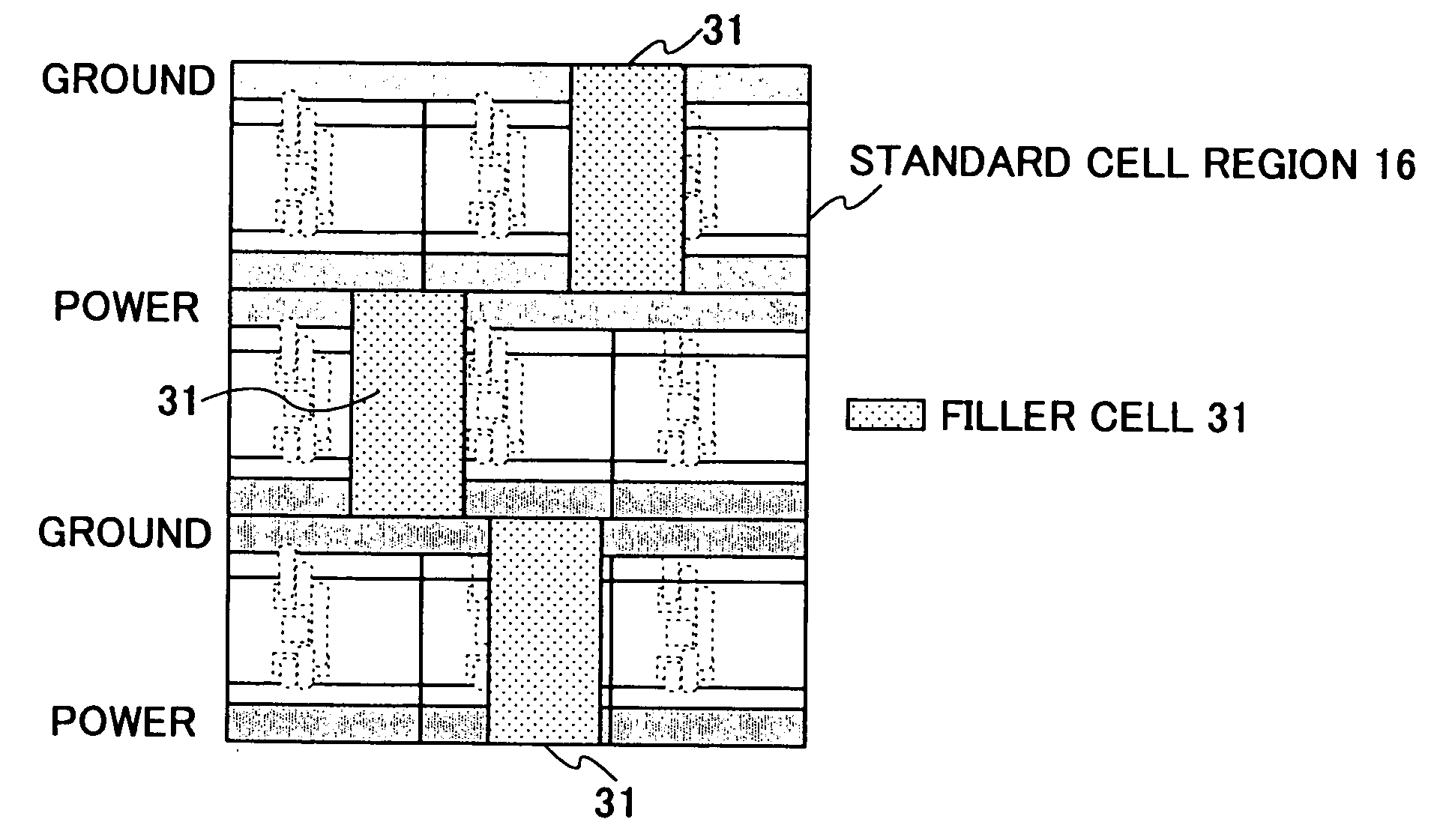

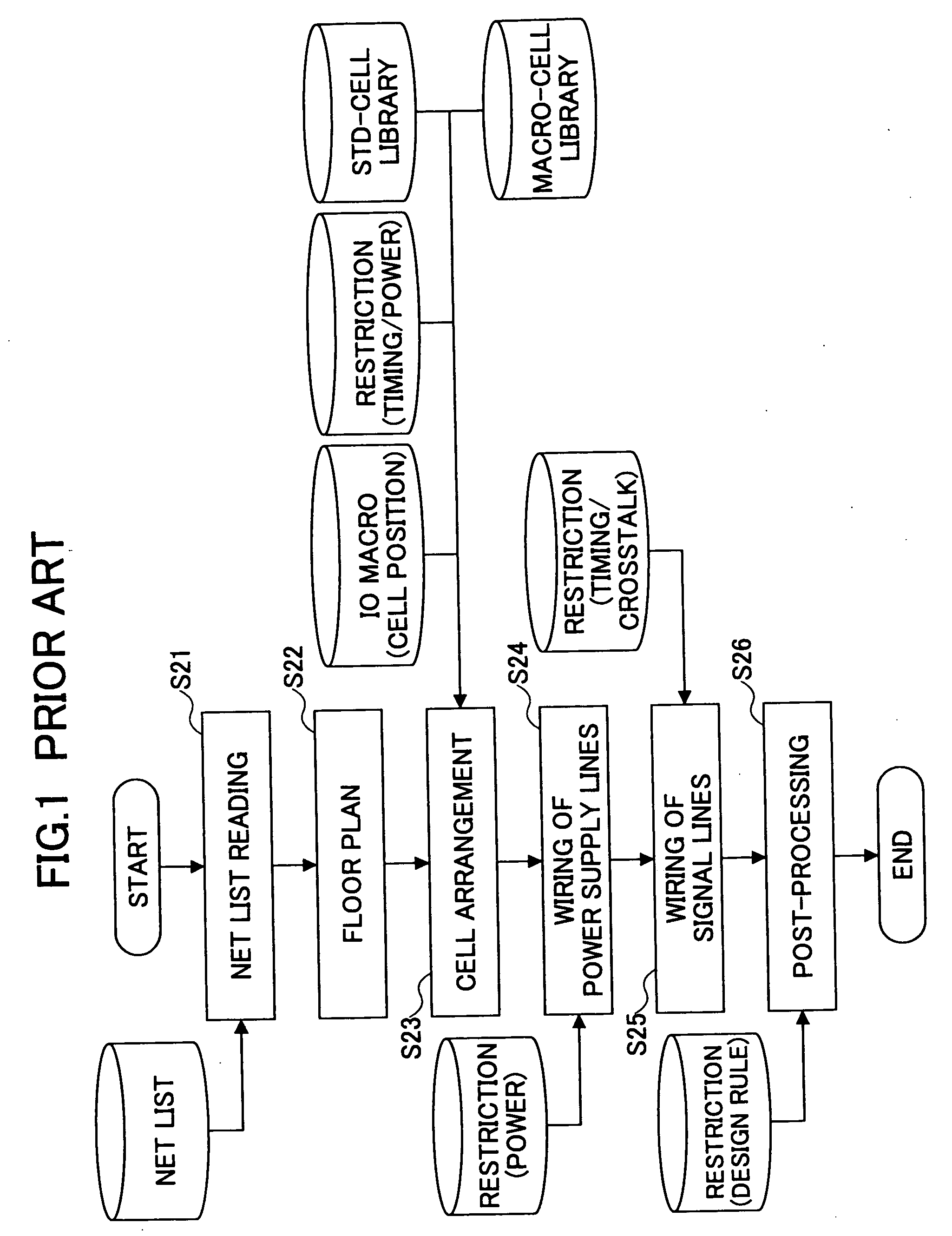

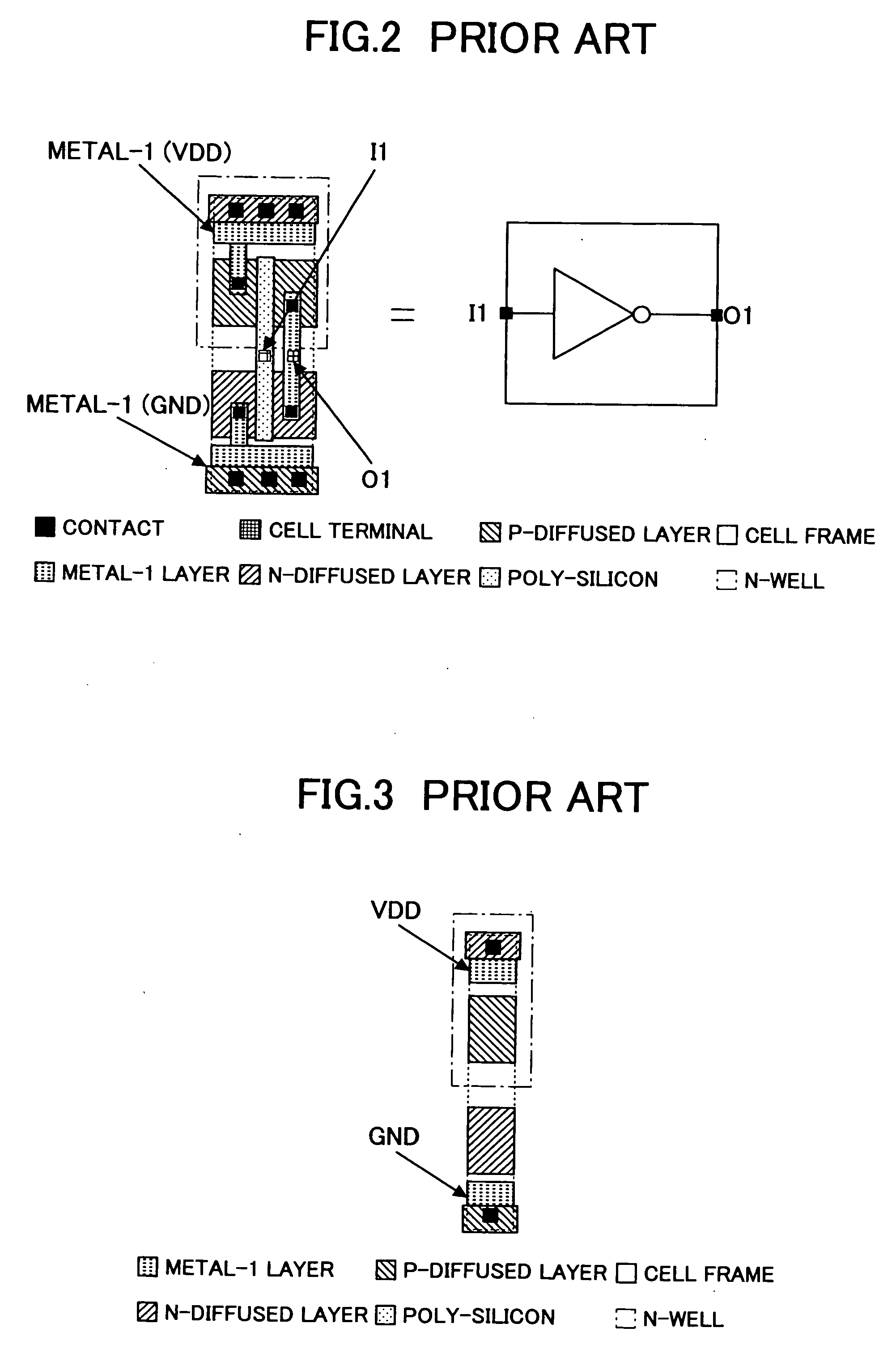

Layout design method for semiconductor integrated circuit, and semiconductor integrated circuit

InactiveUS20060218519A1Reduce impactReduce noiseSolid-state devicesSemiconductor/solid-state device manufacturingEngineeringSemiconductor

In a layout design method for a semiconductor integrated circuit, a cell layout library is provided which stores structure information of functional cells and a plurality of groups of filler cells, each filler cell acting to fill space between the functional cells. The functional cells are arranged on a layout based on the structural information from the layout library. The filler cells of any of the plurality of groups are arranged selectively based on the structural information from the layout library so that the filler cells are arranged in channel regions where the functional cells are not located on the layout, each channel region being located at a predetermined distance from signal lines on the layout.

Owner:RICOH KK

Semiconductor silicon wafer, flattening method therefor, preparation method therefor, and semiconductor device

ActiveCN105405754AImprove planarizationAvoid the problem of not completely corroding awaySemiconductor/solid-state device manufacturingSemiconductor devicesPhosphoric acidSilicon chip

The invention discloses a semiconductor silicon wafer, a flattening method therefor, a preparation method therefor, and a semiconductor device. The flattening method comprises the steps: corroding silicon oxynitride on silicon nitride of an active region in the semiconductor silicon wafer provided with a field oxidation layer through employing hydrofluoric acid solution or the mixed solution of hydrofluoric acid and ammonium fluoride; grinding the surface of the semiconductor silicon wafer through employing the CMP technology, wherein the silicon oxynitride of the semiconductor silicon wafer is corroded; corroding the residual silicon oxynitride on the surface of the ground semiconductor silicon wafer through employing hot phosphoric acid, and obtaining semiconductor silicon chip. Therefore, the method enables all silicon oxynitride in the active region to be corroded before the CMP technology, prevents the incomplete grinding of the silicon oxynitride in the active region of the semiconductor silicon wafer in a smaller area from causing the incomplete corrosion of silicon nitride in a region where there is the residual silicon oxynitride, guarantees that the surface of the active region in the finally obtained semiconductor silicon wafer is completely exposed, and improves the flattening degree of the semiconductor silicon wafer.

Owner:FOUNDER MICROELECTRONICS INT

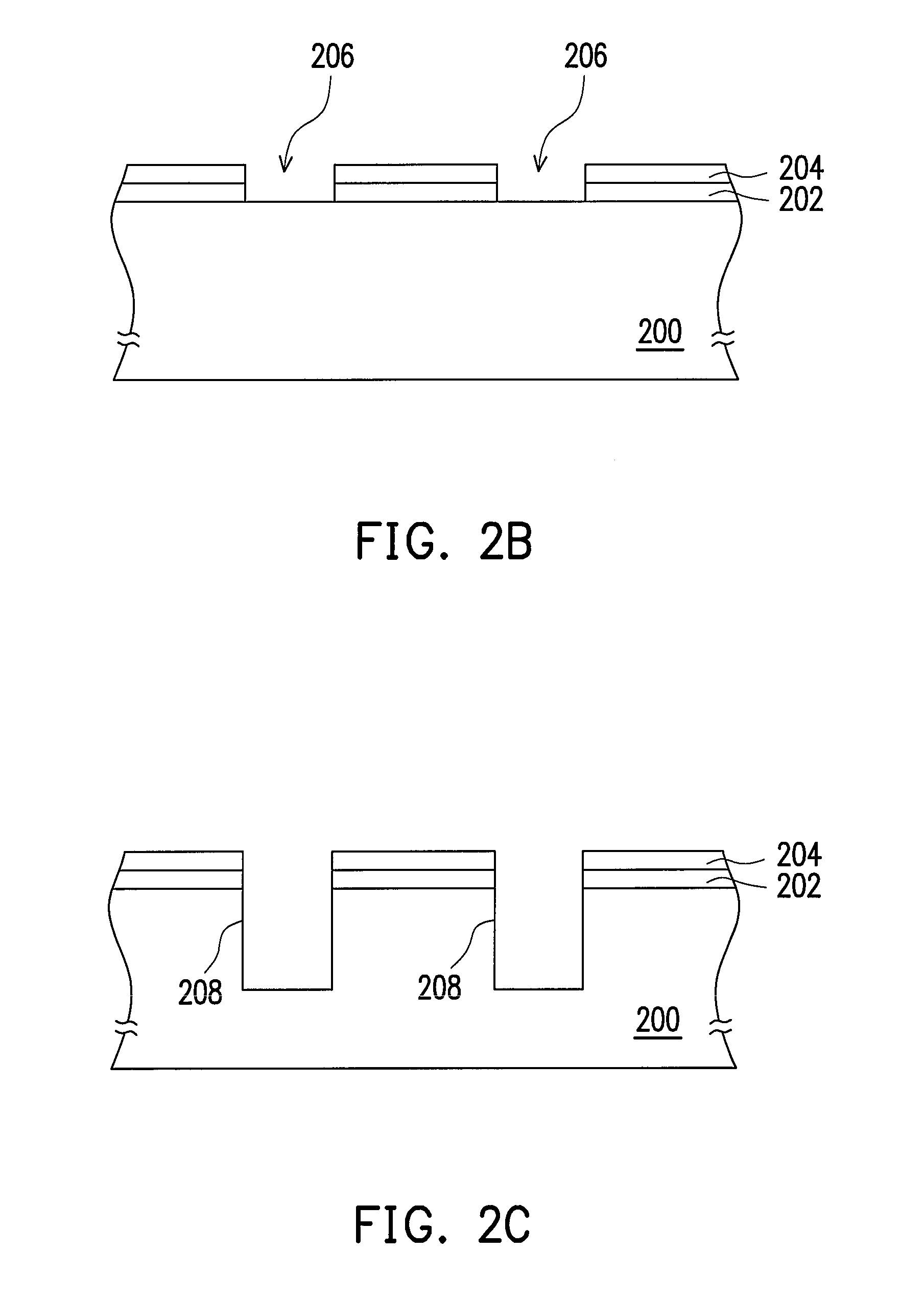

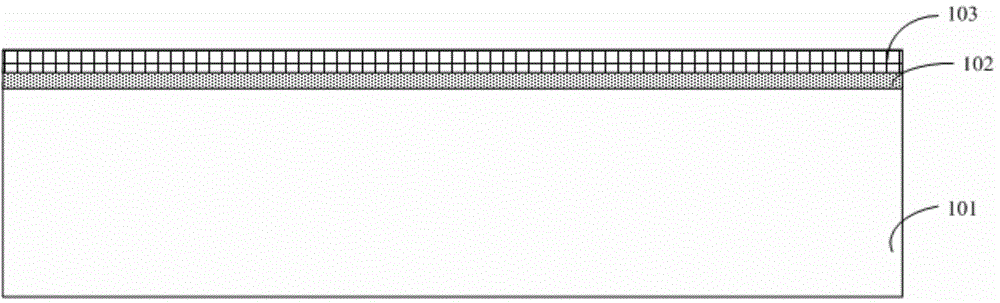

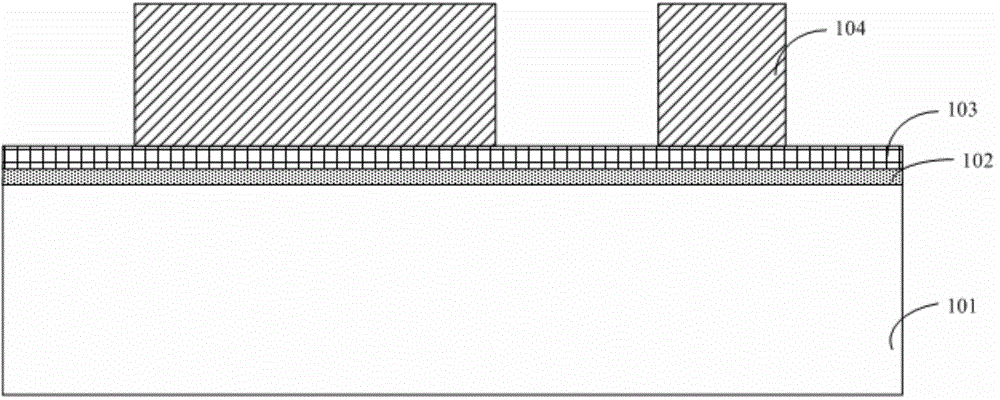

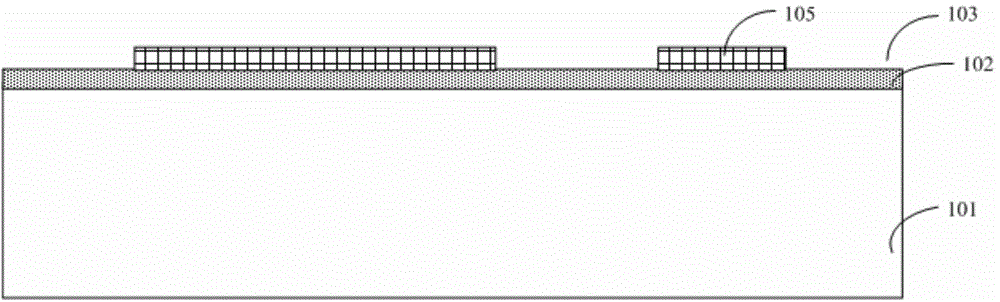

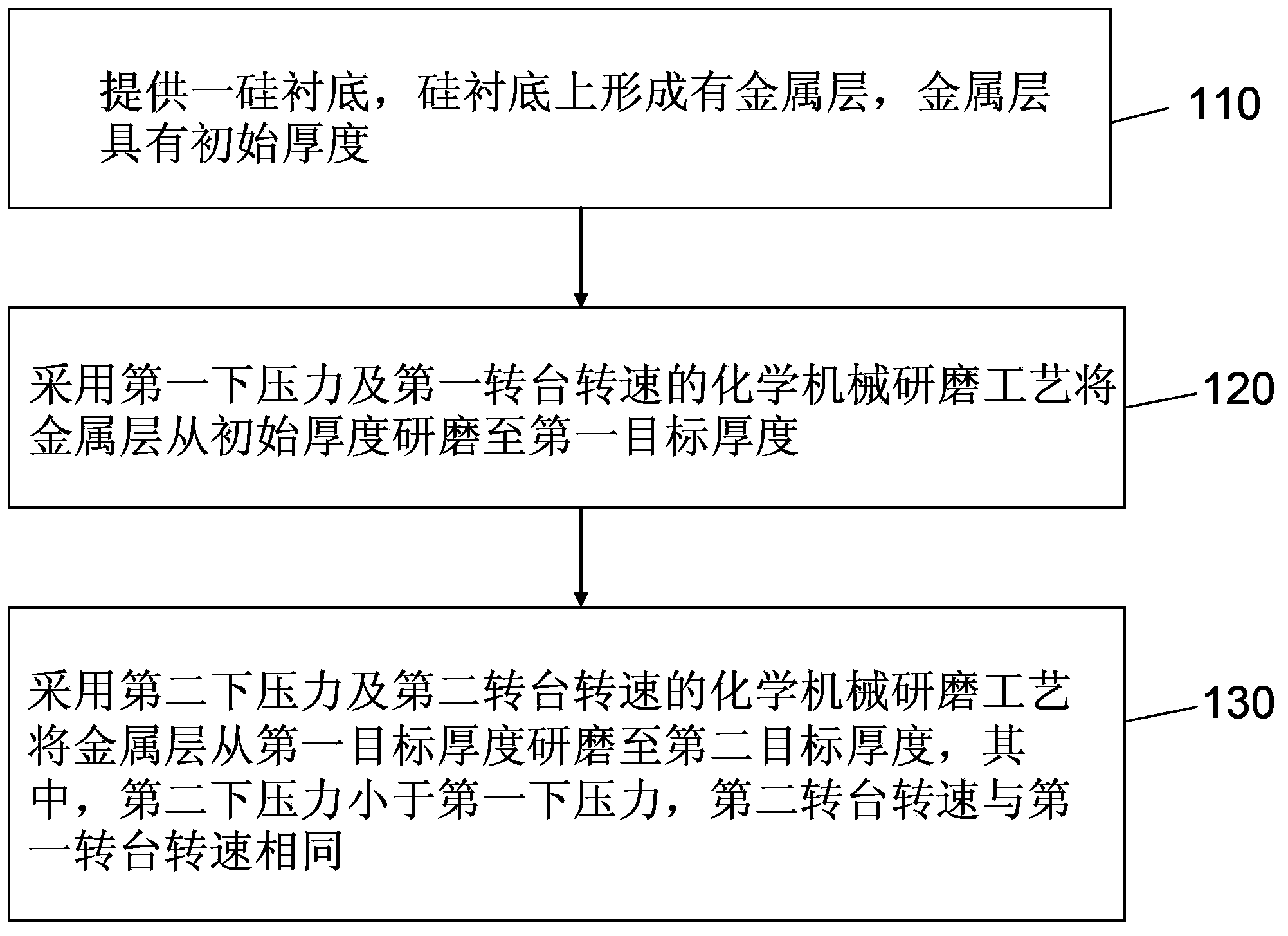

Chip flattening method

InactiveCN104139331AImprove global flatteningImprove chip surface planarizationSemiconductor/solid-state device manufacturingLapping machinesSemiconductorSemiconductor device

The invention discloses a chip flattening method. The chip flattening method includes: providing a silicon substrate and forming a metal layer with an initial thickness on the silicon substrate; grinding the metal layer by a chemical mechanical grinding technology with first pressing force and a first rotary table rotation speed so as to enable the metal layer to be changed from the initial thickness to a first target thickness; grinding the metal layer by the chemical mechanical grinding technology with second pressing force and a second rotary table rotation speed so as to enable the metal layer to be changed from the first target thickness to a second target thickness, wherein the second pressing force is smaller than the first pressing force, and the second rotary table rotation speed is identical to the first rotary table rotation speed. The chip flattening method has the advantages that the metal layer is grinded at the high speed with the larger pressing force and then grinded at the high speed with the smaller pressing force, overall flattening of the surface of the silicon substrate can be improved, flattening of the surface of a chip can be improved, and thereby yield of a semiconductor device can be increased. According to the chip flattening method, the metal layer can be grinded at the high speed with the smaller pressing force and then grinded at the same speed with the larger pressing force.

Owner:ACM RES SHANGHAI

Wafer surface planarization method

InactiveCN100561677CImprove planarizationAfter-treatment detailsSemiconductor/solid-state device manufacturingDielectric surfaceOptoelectronics

The invention discloses a method for flattening the surface of a wafer, comprising: providing a wafer with a dielectric layer on the surface, including a central region and an edge region surrounding the central region; removing a partial thickness of the dielectric layer in the edge region; for the entire wafer surface The medium layer is chemically mechanically polished, wherein the edge area is the area of the medium layer where the thickness of the medium layer is greater than the depth of the etched through hole after the test piece is ground, and the thickness of the medium layer in the edge area is greater than or equal to that measured by the test piece after chemical mechanical grinding. The average thickness difference between the dielectric layer in the center area of the wafer and the dielectric layer in the edge area of the wafer. The method for flattening the wafer surface of the present invention makes the dielectric layer on the wafer surface undergo chemical mechanical grinding, and the gap between the thickness of the dielectric layer in the edge region of the wafer and the thickness of the dielectric layer in the central region of the wafer is reduced, thereby improving the flatness of the wafer surface. degree of transformation.

Owner:SEMICON MFG INT (SHANGHAI) CORP +1

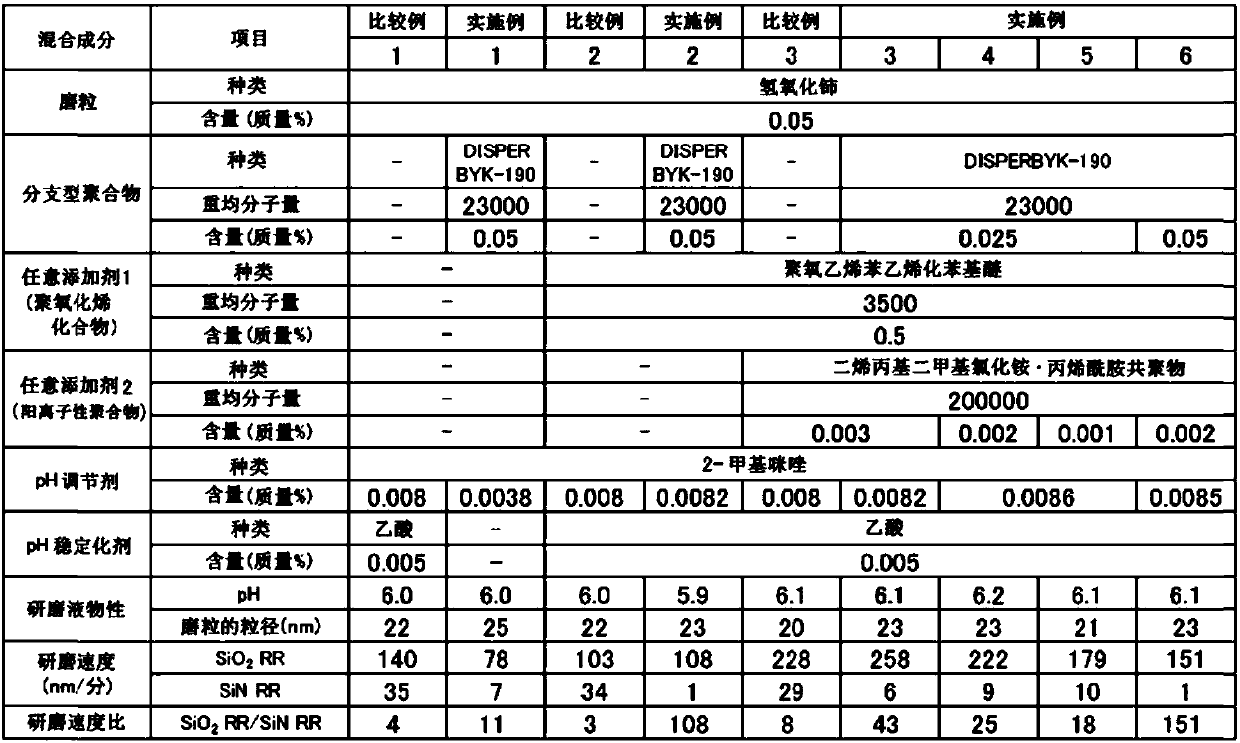

Polishing liquid, polishing liquid set, and substrate polishing method

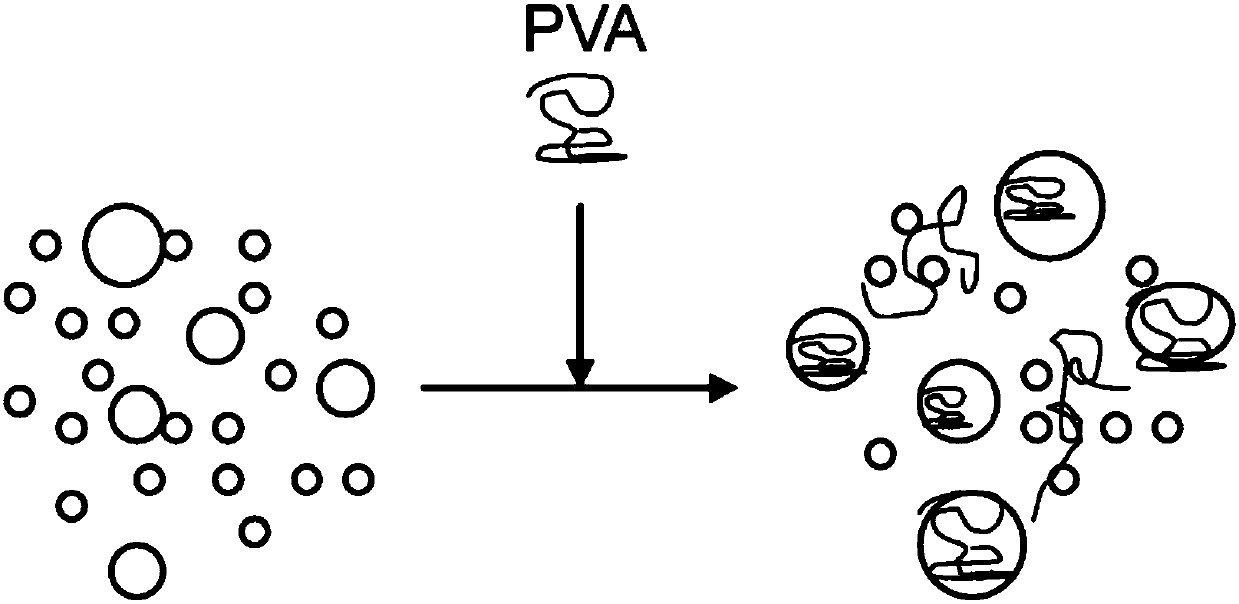

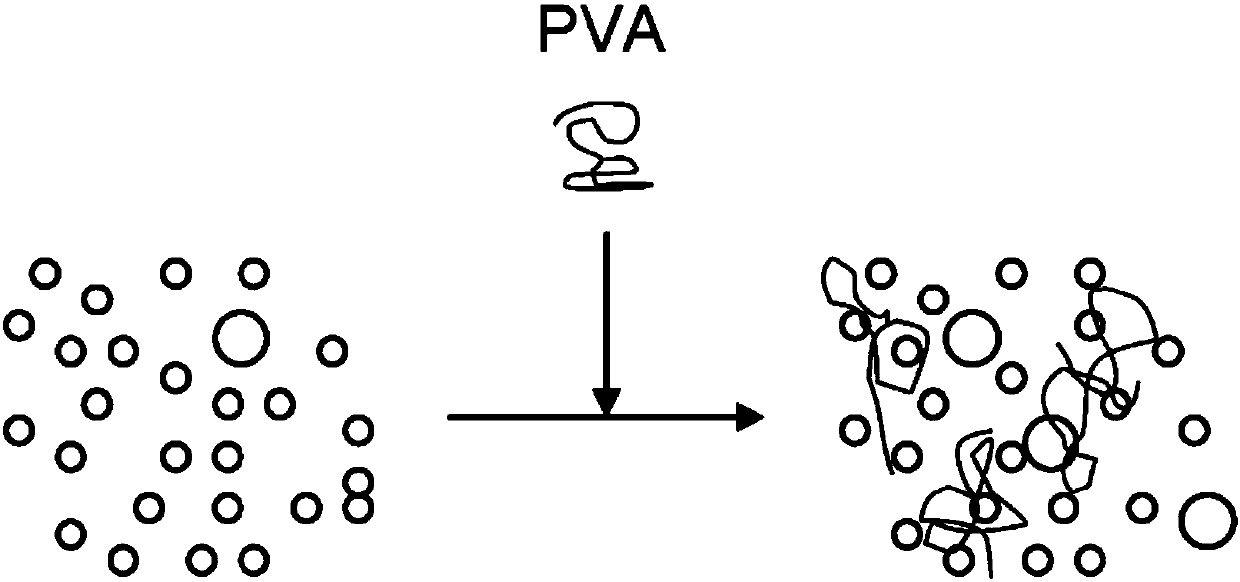

ActiveCN107949615AImprove grinding selectivityGrinding inhibitionOther chemical processesSemiconductor/solid-state device manufacturingChemical physicsPolymer

Provided is a polishing liquid comprising a liquid vehicle, abrasive grains, and a polymer. The polymer has a first molecular chain where functional groups are directly bonded and a second molecular chain branched from the first molecular chain. The functional groups are at least one selected from the group consisting of carboxyl, carboxylate, hydroxyl, sulfo, and sulfonate groups.

Owner:RESONAC CORP

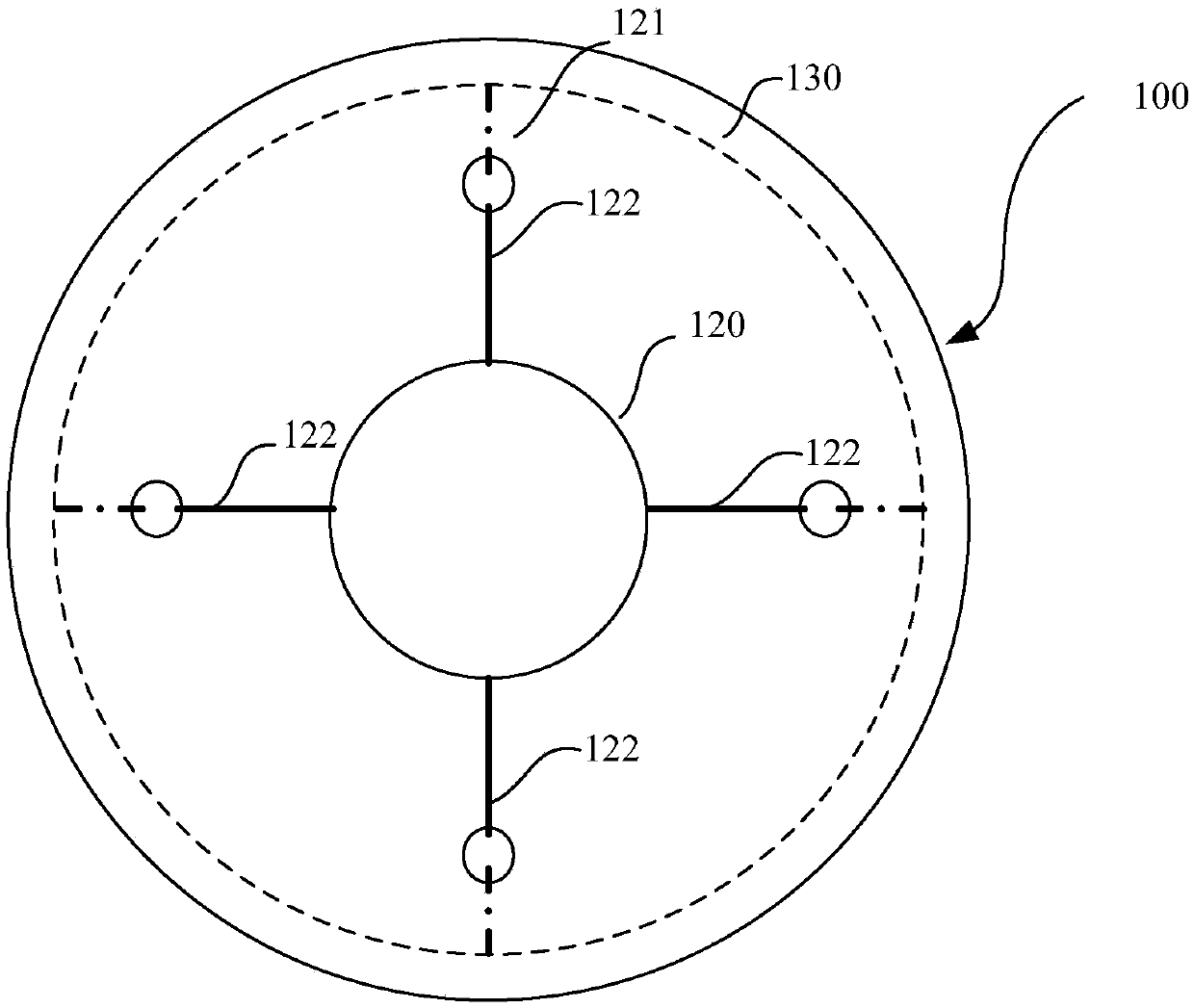

Grinding head and chemical mechanical grinding equipment

InactiveCN109605210AAvoid Planarization DefectsImprove planarizationLapping machinesWork carriersElectrical connectionMetallic materials

The invention provides a grinding head and chemical mechanical grinding equipment. The grinding head comprises a main body component for bearing wafers, a connecting component, a metal clamping ring and a ground lead, wherein the connecting component is fixed to the main body component; the connecting component comprises a conductive material; the clamping ring is arranged on the outer circumference of the main body component; the clamping ring is made of a conductive material; and a metal material of the connecting component is electrically connected with the clamping ring through the electrical connection line. Through the electrical connection line, charges unevenly distributed on the wafers caused by by-products generated by reaction during grinding can be conducted to the ground end,therefore, the planarization defect caused by uneven charges is avoided, and the planarization degree is increased.

Owner:YANGTZE MEMORY TECH CO LTD

Multilayer substrate

InactiveUS8174664B2Reduction in productivityReduction in qualitySemiconductor/solid-state device manufacturingNon-linear opticsProduction rateSurface layer

The present invention provides: a multilayer substrate in which a spacer is selectively disposed in a non-display region without reduction in display quality or productivity of a liquid crystal display device; a production method thereof; and a liquid crystal display panel and a liquid crystal display device each using the multilayer substrate or the production method thereof. The multilayer substrate of the present invention is a multilayer substrate comprising a resin interlayer film and an electrode on a substrate in this order, wherein the multilayer substrate has a depression structure including the resin interlayer film in a surface layer, or a depression structure having a rough bottom surface on the resin interlayer film.

Owner:SHARP KK

Polishing layer, polishing pad and a preparation method of polishing layer

ActiveCN109693176AReduce wear rateHigh removal rateGrinding devicesLapping toolsPrepolymerIsocyanate

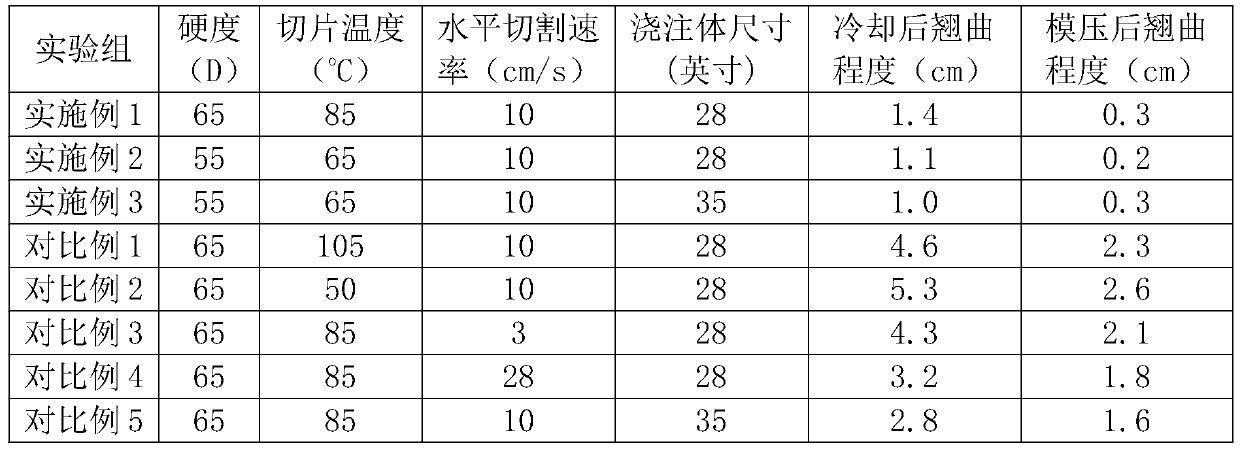

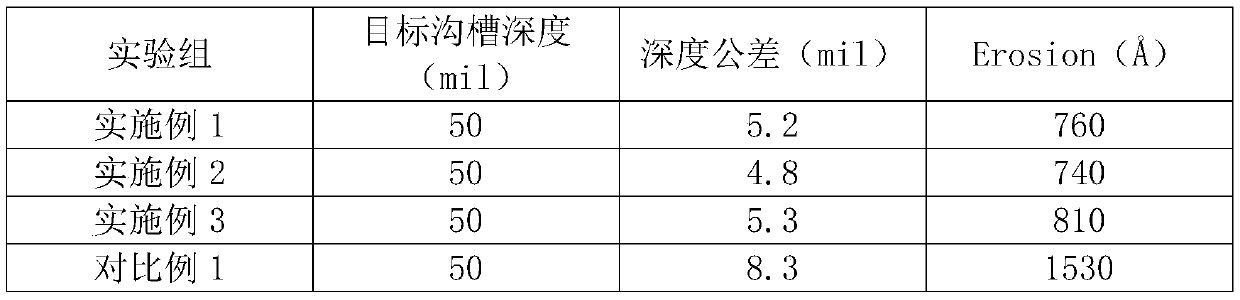

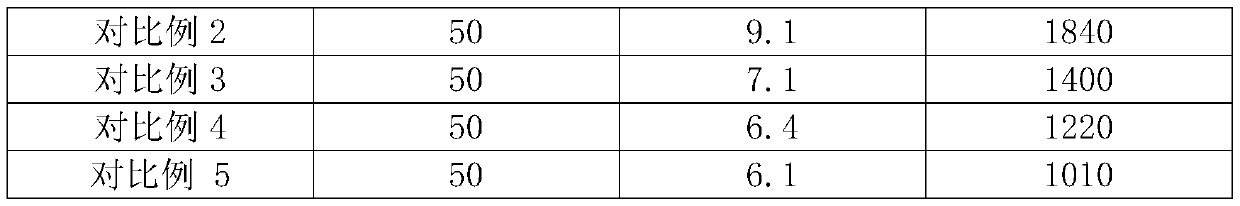

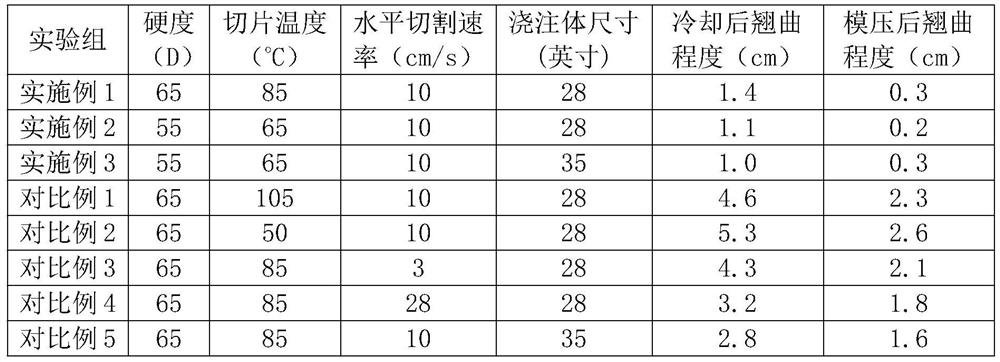

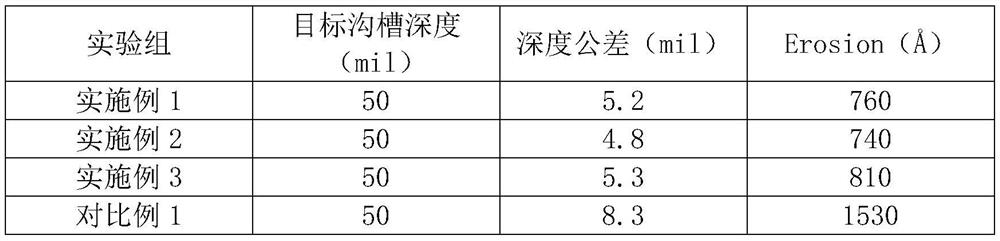

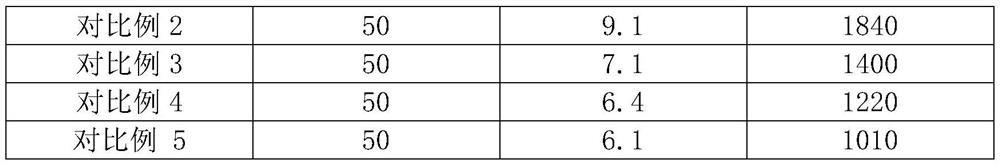

The invention provides a polishing layer, a polishing pad with the polishing layer and a preparation method of the polishing layer, and relates to the technical field of polishing of chemical mechanical planarization treatment. The preparation method comprises the following steps that prepolymer of bifunctional or polyfunctional isocyanate in component A and a multi-component mixture of a hollow microsphere in component B and a curing agent in component C are prepared; forming by pouring is carried out, specifically, the multi-component mixture is poured into a mould cavity and subjected to leveling gelation; heating and solidifying are carried out, specifically, a mould loading a gelatinous ternary mixture is heated and solidified, to obtain a pouring body; and when the temperature is lowered to a predetermined temperature T, the heat preservation and slice cutting are performed, and the horizontal cutting rate V of a cutter relative to the pouring body during slice cutting meets: 8cm / s <= V<= 20 cm / s.

Owner:HUBEI DINGHUI MICROELECTRONICS MATERIALS CO LTD +1

a polishing pad

The invention discloses a polishing pad for solving the problems of nonuniform distribution of polishing liquid and need of further improvement of the polishing speed and the leveling degree in a traditional polishing pad. The polishing pad at least comprises a circular polishing layer; a groove for flowing the polishing liquid is formed in the upper surface of the polishing layer; the groove consists of a peripheral groove and a radial groove; the peripheral groove is a peripheral geometric center symmetry pattern with the circle center of the polishing layer as center; the edges m of the pattern are not fewer than 3; and the radial groove is a straight line or / and a curve scattered from the peripheral direction along the circle center, and has an intersecting point with the peripheral groove. The polishing pad is simple in structure, can enable the polishing liquid to uniformly distribute and flow in a polishing area, keeps uniform concentration of reactants and products in the polishing liquid in the polishing area to the greatest extent, accelerates the polishing speed, and improves the wafer planar degree.

Owner:HUBEI DINGLONG CO LTD

Polishing composition using polishing particles containing basic substance and having high water affinity

PendingUS20220228031A1Improve polishing rateDefects generated on a polished surface can be reducedOther chemical processesSemiconductor/solid-state device manufacturingPulse nuclear magnetic resonanceSilica particle

A polishing composition that is for use in CMP polishing and that makes it possible to minimize the occurrence of defects. A polishing composition comprising silica particles, a basic nitrogen-containing organic compound, and water serving as a solvent, wherein the composition exhibits an Rsp value of the following Formula (1) of more than 0.7 and 6 or less as calculated from values measured by pulse NMR: Rsp=(Rav−Rb) / (Rb) . . . (1) (wherein Rsp is an index of water affinity; Rav is the reciprocal of the relaxation time of the polishing composition; and Rb is the reciprocal of the relaxation time of the water serving as a solvent of the polishing composition).

Owner:NISSAN CHEM IND LTD

A way to add redundant graphics

ActiveCN103855044BReduce density distribution varianceUniform density distributionSemiconductor/solid-state device manufacturingGraphicsDensity distribution

The invention provides a method for adding redundant graphics. The method comprises the following steps: dividing a domain into a plurality of subdomains in the same size and calculating an original density value of each subdomain; dividing the subdomains into a plurality of groups and taking the subdomains with the same or similar original density values as one group; selecting the groups in which the redundant graphics need to be added; calculating the sizes of the redundant graphics needing to be added in the subdomains of each group according to the density values; setting a scaling value and scaling each of the redundant graphics in the subdomains of the same group according to the scaling value; calculating the scaled density values of the subdomains; calculating a density difference of the original density values and the scaled density values of the subdomains; and adjusting the sizes of the redundant graphics according to an absolute value of the density difference, wherein the sizes of the redundant graphics are decreased along with the increasing of the absolute value of the density difference. According to the method, the homogeneous density distribution of wafers is ensured; the density distribution difference of the domain and the wafers is reduced, so that the flatness degree is improved.

Owner:SHANGHAI HUALI MICROELECTRONICS CORP

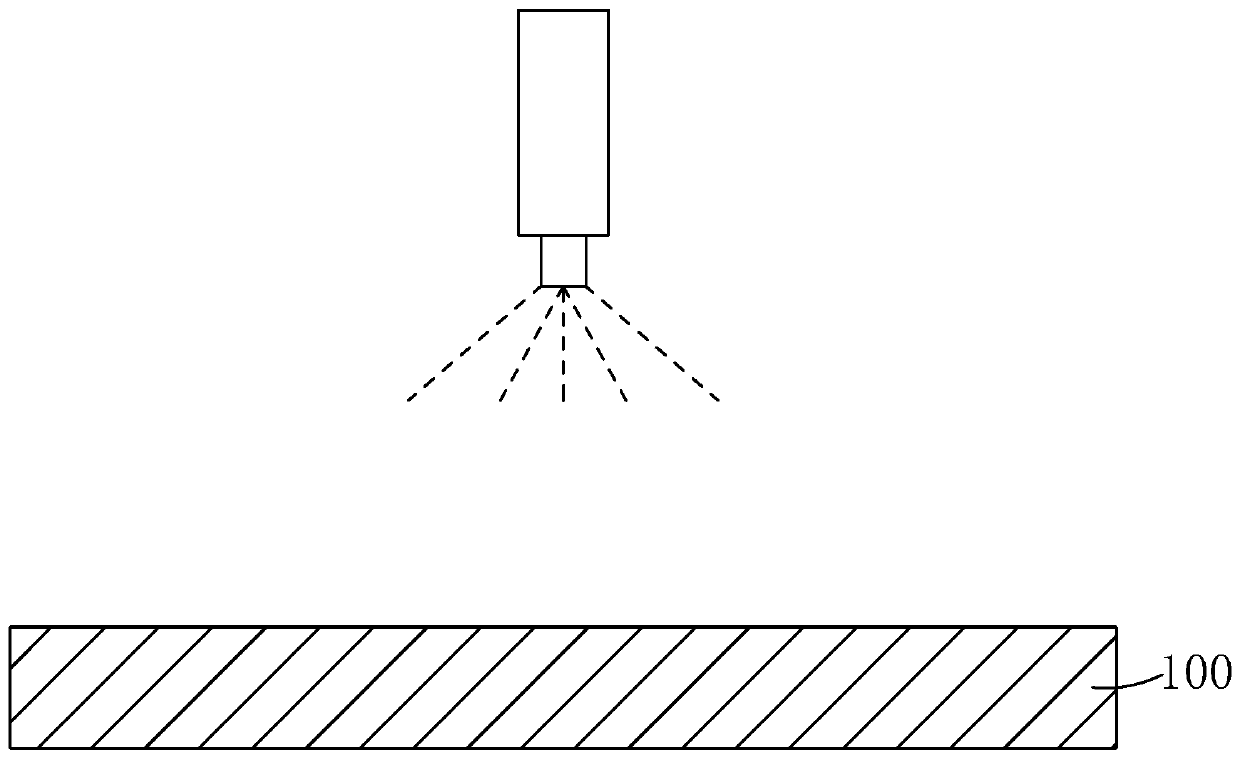

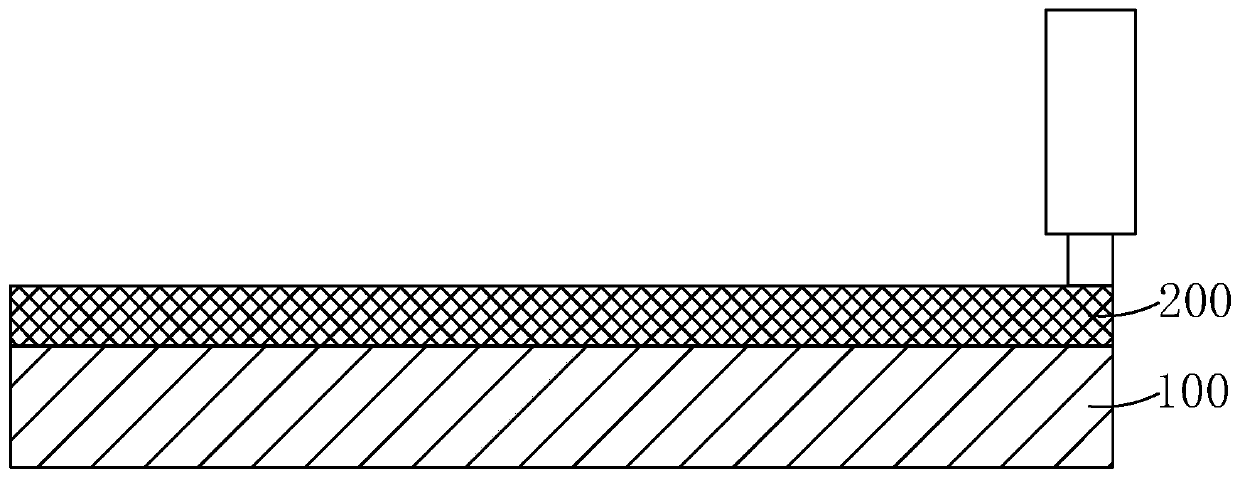

Manufacturing method of flexible amoled display

ActiveCN106449711BGuaranteed Optical PerformanceAvoid dentsSolid-state devicesSemiconductor/solid-state device manufacturingOptical propertyDisplay device

The invention provides a method for manufacturing a flexible AMOLED display. Before making a flexible substrate on a rigid substrate, firstly, an inorganic film layer with a flat surface is formed on the rigid substrate, and then a polymeric film is coated on the inorganic film layer. material to form a flexible substrate, which can not only avoid the problem of sag and protrusion of the flexible substrate caused by impurity particles remaining on the surface of the rigid substrate due to poor cleaning, but also make the flexible substrate and the rigid substrate peel off. The substrate is easily separated from the rigid substrate to protect the flexible substrate from damage, so that the flexible substrate of the flexible AMOLED display has a higher degree of planarization, improves the water and oxygen barrier performance of the flexible substrate, and ensures flexibility. Optical properties of AMOLED displays.

Owner:WUHAN CHINA STAR OPTOELECTRONICS TECH CO LTD

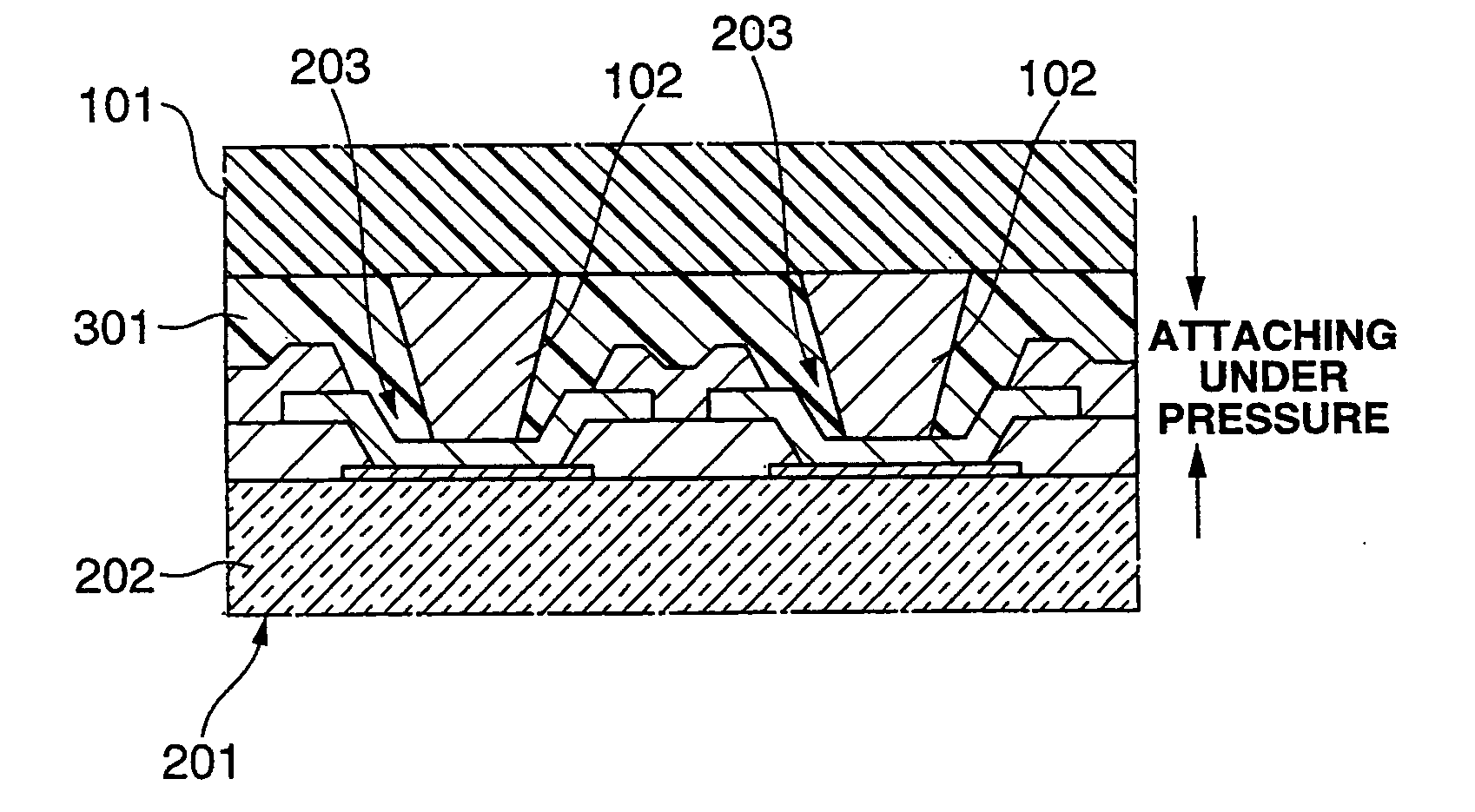

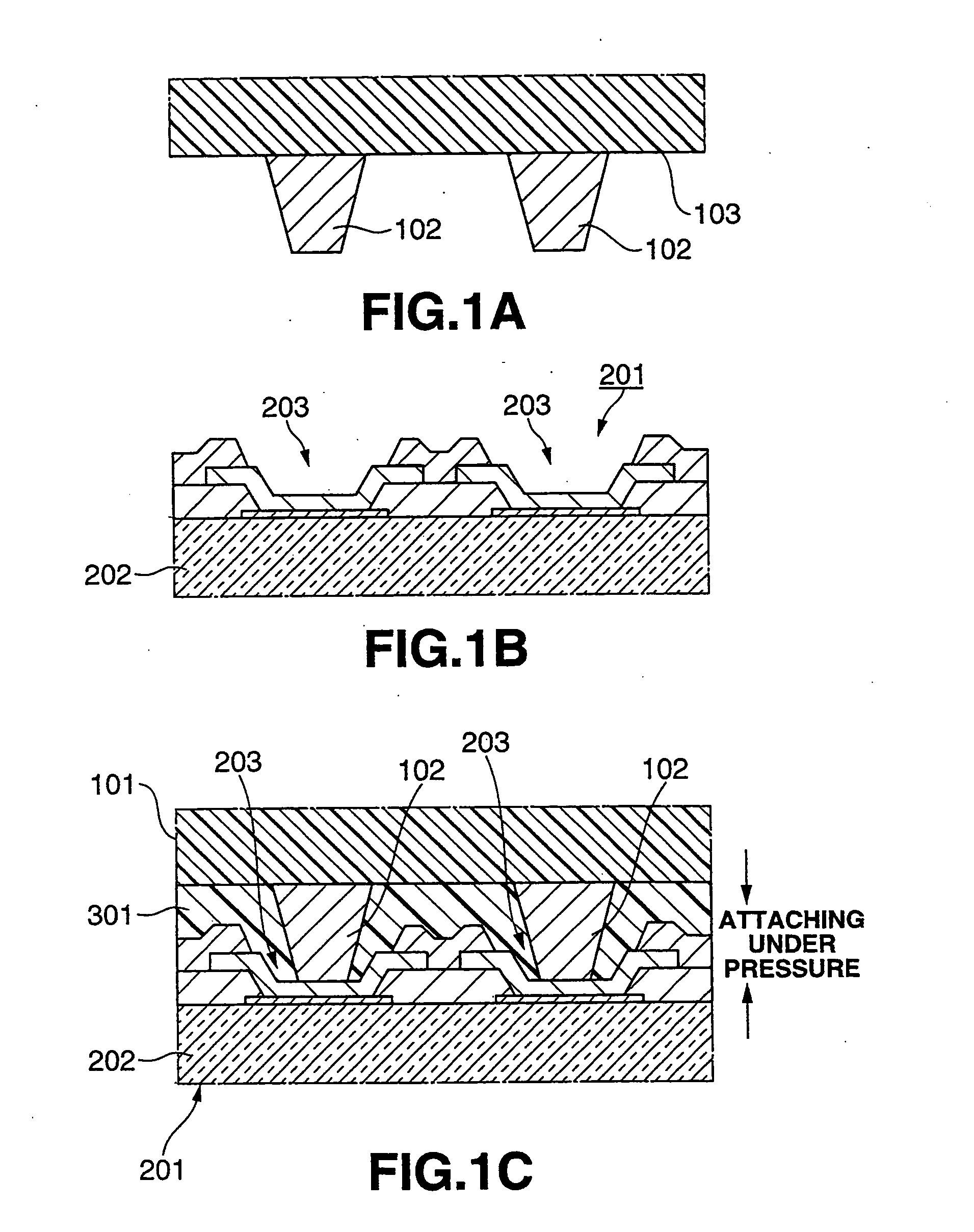

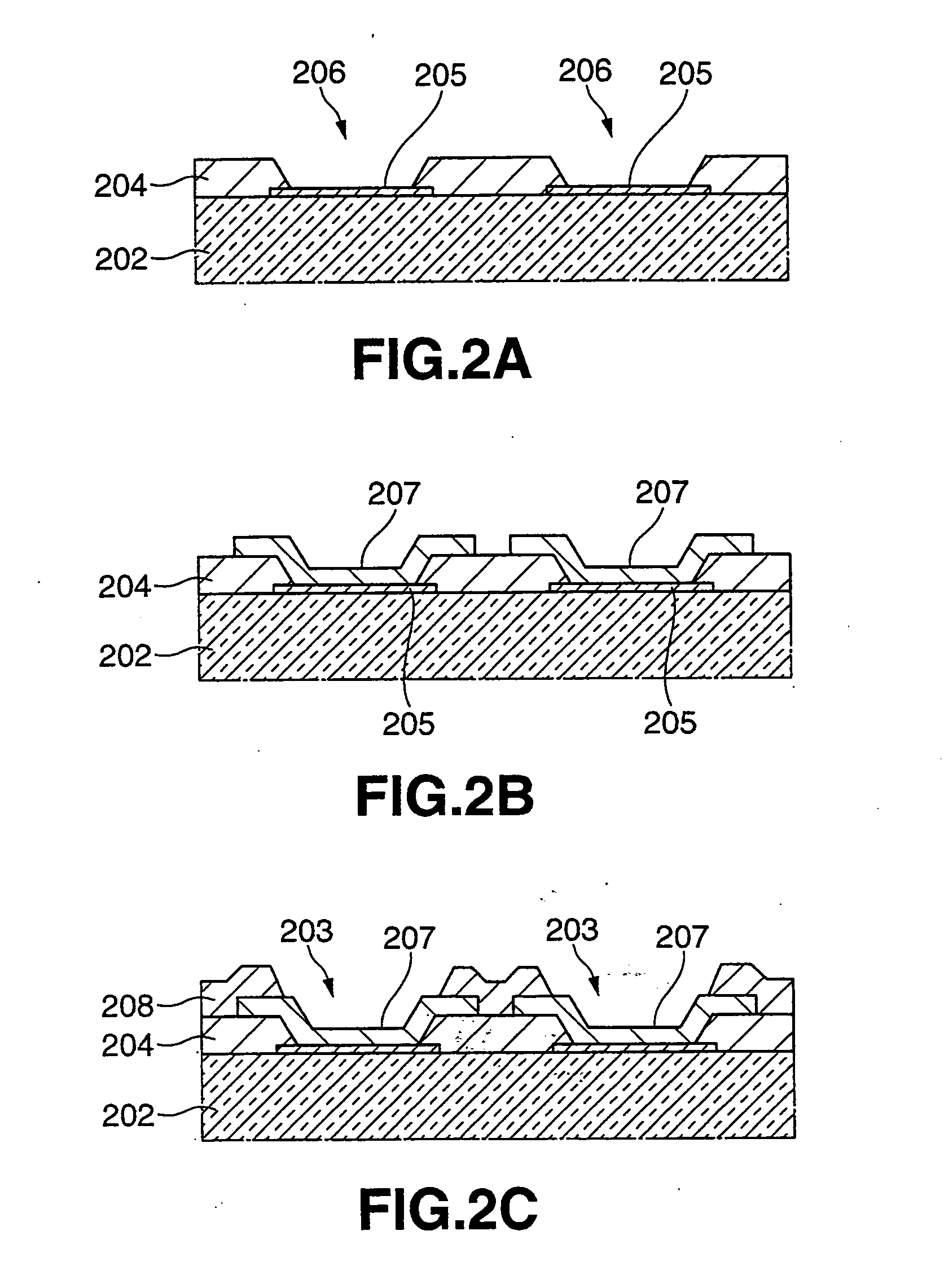

Electric circuit substrate

InactiveUS20050040544A1High reliabilityImprove planarizationSemiconductor/solid-state device detailsPrinted circuit aspectsLiquid-crystal displayIntegrated circuit

On a glass substrate of a liquid crystal display device, electrode parts to which metallic electrodes (bumps) of an IC circuit are connected from an upper part are formed. The electrode parts are formed by opening an interlayer dielectric film at parts corresponding to metal wiring and forming land shaped electrode pads in the opening parts. In this invention, the planar forms of the electrode pads are smaller than the opening parts of the interlayer dielectric film. Thus, the planarization of the peripheral surfaces around the electrode parts is improved. Accordingly, integrated circuit devices (IC) or semiconductor chips can be connected with high reliability.

Owner:SONY CORP

Polishing layer, polishing pad and preparation method

ActiveCN109693176BReduce wear rateHigh removal rateGrinding devicesLapping toolsPolymer scienceMicrosphere

The invention provides a polishing layer, a polishing pad with the polishing layer and a preparation method of the polishing layer, and relates to the technical field of polishing of chemical mechanical planarization treatment. The preparation method comprises the following steps that prepolymer of bifunctional or polyfunctional isocyanate in component A and a multi-component mixture of a hollow microsphere in component B and a curing agent in component C are prepared; forming by pouring is carried out, specifically, the multi-component mixture is poured into a mould cavity and subjected to leveling gelation; heating and solidifying are carried out, specifically, a mould loading a gelatinous ternary mixture is heated and solidified, to obtain a pouring body; and when the temperature is lowered to a predetermined temperature T, the heat preservation and slice cutting are performed, and the horizontal cutting rate V of a cutter relative to the pouring body during slice cutting meets: 8cm / s <= V<= 20 cm / s.

Owner:HUBEI DINGHUI MICROELECTRONICS MATERIALS CO LTD +1