Forming method of dual-damascene structure

A dual damascene structure and patterning technology, which is applied in the manufacture of electrical components, semiconductor/solid-state devices, circuits, etc., can solve the problems affecting the margin of the manufacturing process, the dual damascene structure, the difficulty of filling the anti-reflection layer through holes, etc., and achieve the goal of optimizing the gap Groove etching effect, improved critical dimension accuracy, easy to form and etch effect

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment Construction

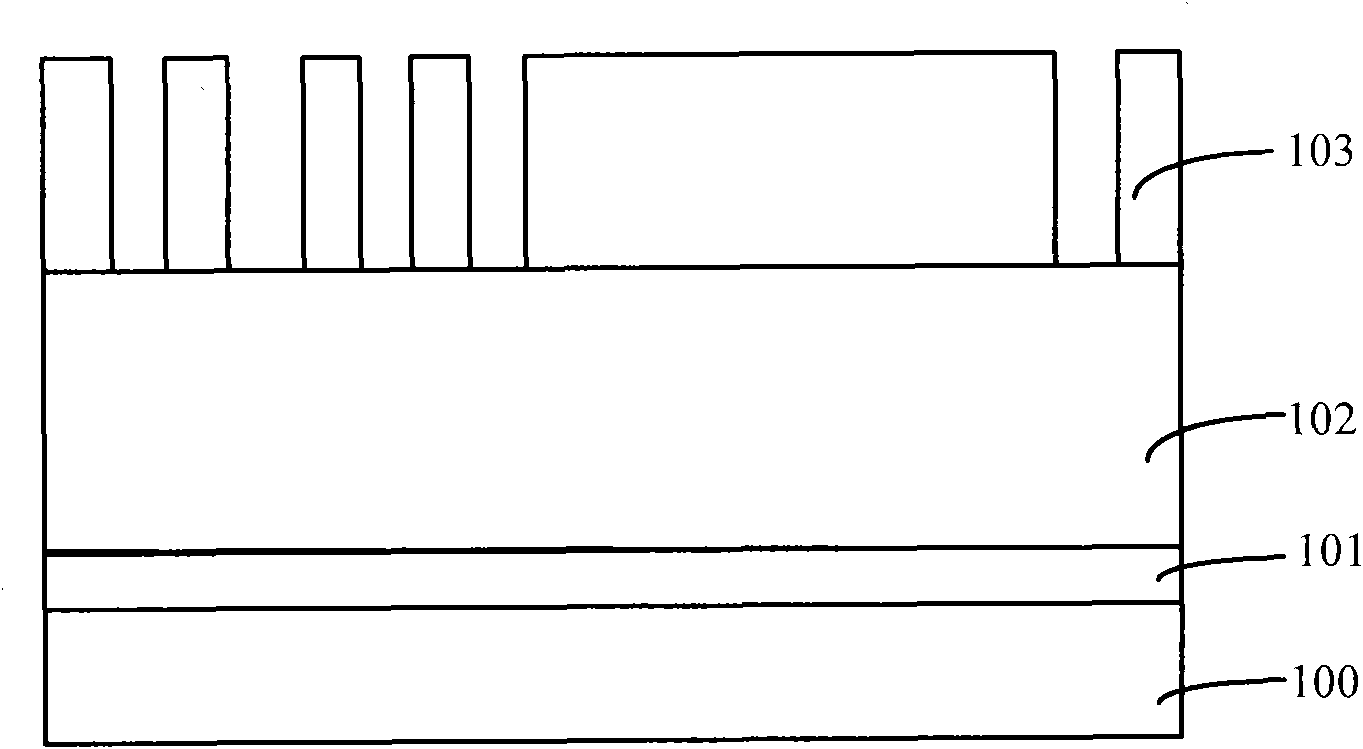

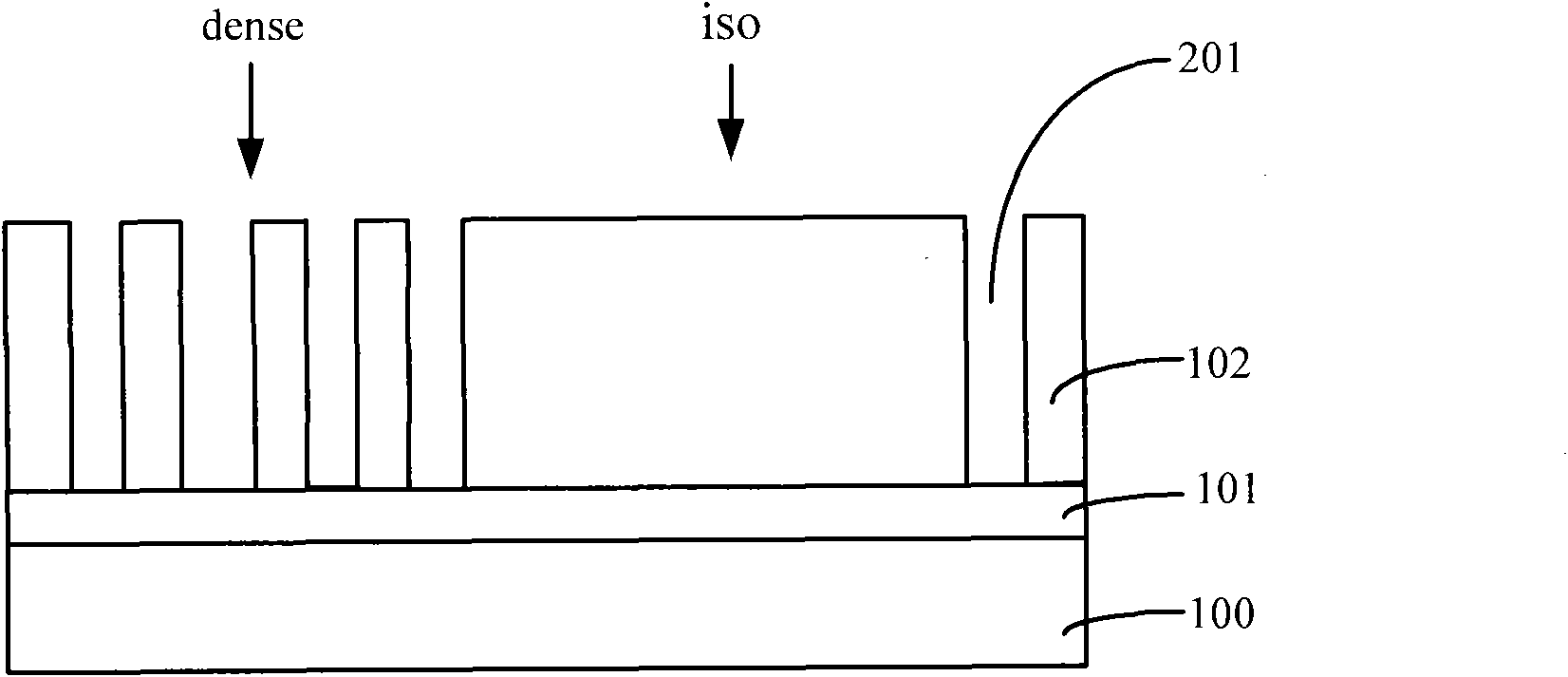

[0031] In the actual manufacture of the dual damascene structure, the prior art method will cause uneven distribution of the line width of the exposure pattern during the trench photolithography process, resulting in inaccurate critical dimensions of the dual damascene structure. After research, it was found that the problem was caused by photolithography defocus and shallow depth of focus.

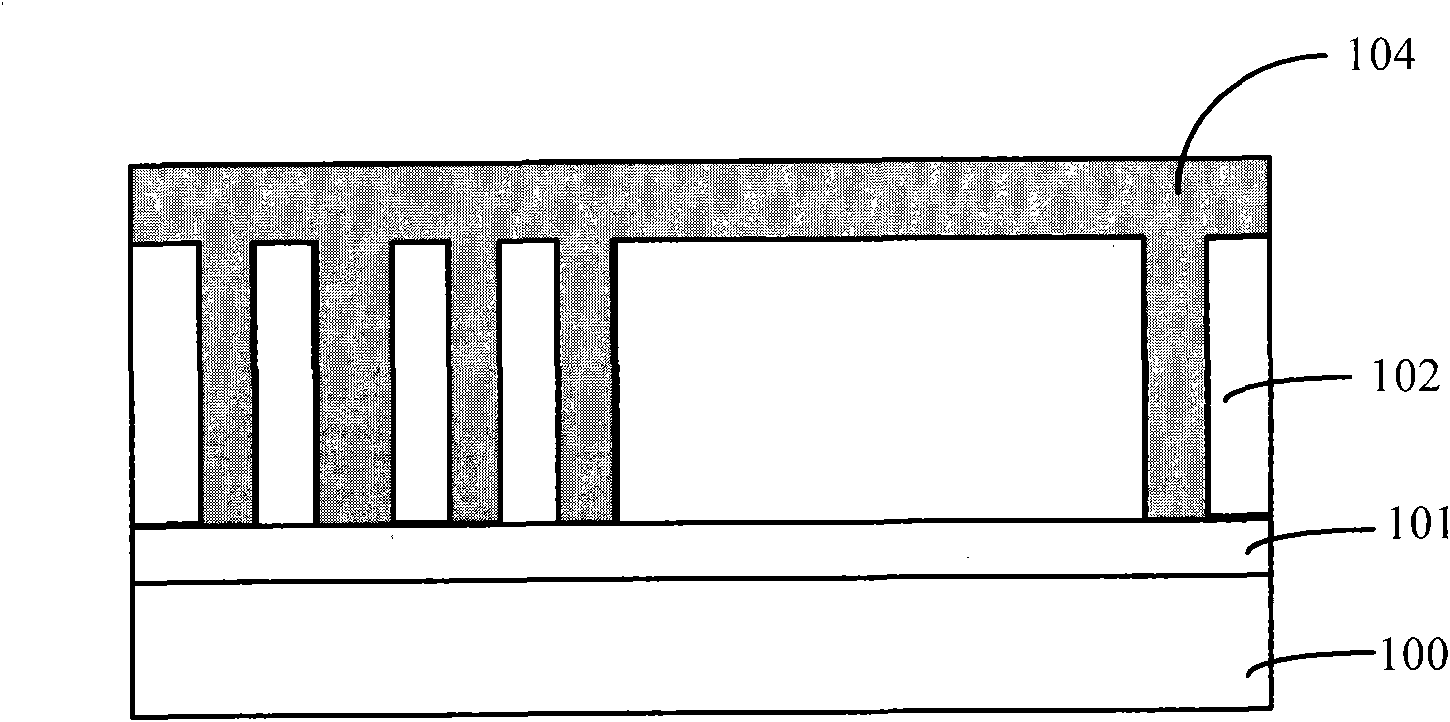

[0032] Further, the inventors found that because there are more through holes in the dense area, in the third step, that is, in the through hole filling process, voids occur after filling the through holes, such as Figure 7 As shown, the height a of dense area dense after filling is smaller than the height b of isolated area iso. The maximum difference dense / iso bias between the dense area and the isolated area is defined as the maximum height b of the isolated area minus the minimum height a of the dense area, the formula is as follows:

[0033] dense / iso bias=Max(iso)-Min(dense)=b-a ...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More