Semiconductor silicon wafer, flattening method therefor, preparation method therefor, and semiconductor device

A planarization method and semiconductor technology, applied in semiconductor devices, semiconductor/solid-state device manufacturing, electrical components, etc., can solve the problems of semiconductor device leakage, incomplete grinding, and silicon nitride can not be completely corroded, so as to improve planarization degree of effect

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment 1

[0060] Such as figure 2 As shown, it is a schematic flowchart of a semiconductor silicon wafer planarization method provided in Embodiment 1 of the present invention, which mainly includes the following steps:

[0061] Step 201: Using hydrofluoric acid solution or a mixed solution of hydrofluoric acid and ammonium fluoride, etch the silicon oxynitride located on the silicon nitride in the active region of the semiconductor silicon wafer. Wherein, the semiconductor silicon wafer is a silicon wafer formed with a field oxide layer.

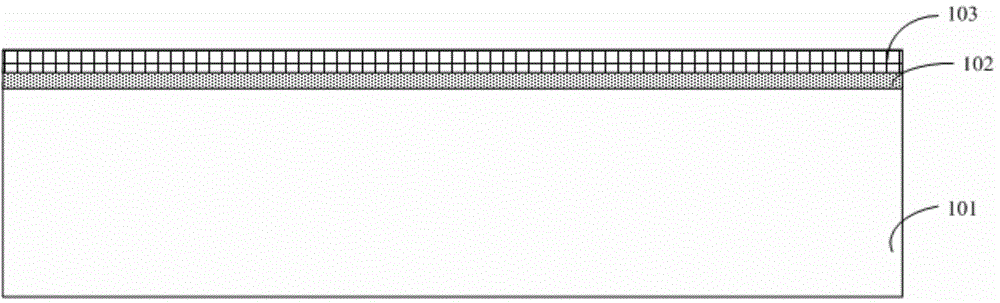

[0062] In the embodiment of the present invention, a semiconductor silicon wafer with a field oxide layer formed as shown in FIG. The semiconductor silicon wafer as shown in FIG. 3(a) is obtained in other ways, and the present invention does not limit its specific implementation, as long as the semiconductor silicon wafer as shown in FIG. 3(a) is obtained.

[0063] Since silicon oxynitride and hydrofluoric acid can react chemically, the nitrogen p...

Embodiment 2

[0078] like Figure 4 As shown, it is a schematic flow chart of a method for preparing a semiconductor silicon wafer provided by Embodiment 2 of the present invention, which specifically includes the following steps:

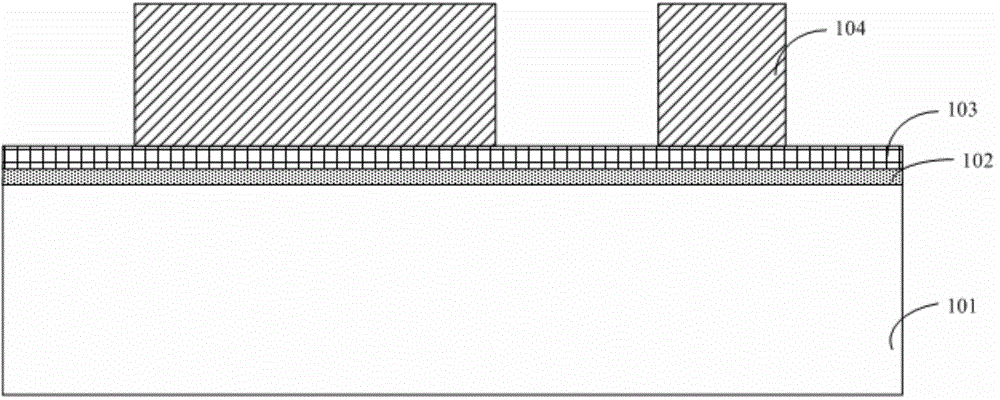

[0079] Step 301 : forming a pad oxide layer and silicon nitride on the substrate silicon wafer.

[0080] Step 302: Etching the silicon nitride to form a semiconductor silicon wafer including an active region and a field region.

[0081] Step 303: forming a field oxide layer on the field region of the semiconductor silicon wafer including the active region and the field region.

[0082] Step 304: Using hydrofluoric acid solution or a mixed solution of hydrofluoric acid and ammonium fluoride, etch the silicon oxynitride located on the silicon nitride in the active region of the semiconductor silicon wafer.

[0083] Specifically, in this step, the semiconductor silicon wafer is placed in an etching tank, and after the etching time t, the semiconductor silicon waf...

Embodiment 3

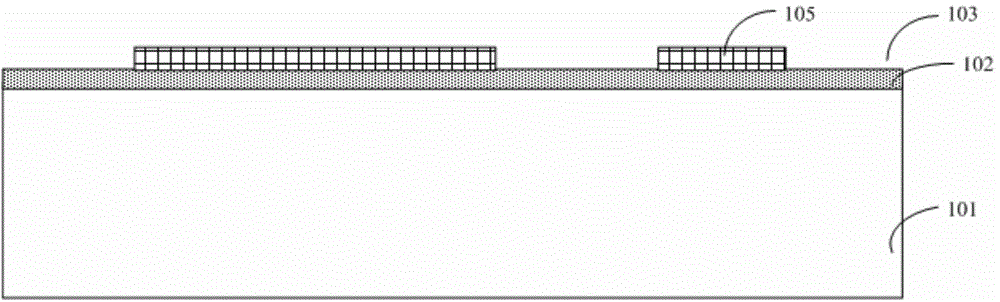

[0089] like Figure 5 As shown, it is a schematic structural diagram of a semiconductor silicon wafer provided by Embodiment 3 of the present invention. In the semiconductor silicon wafer, silicon nitride and silicon oxynitride in the active area are respectively etched away, and the oxide layer in the active area One surface of 501 is fully exposed.

[0090] Wherein, the silicon oxynitride in the active region is corroded by any of the following solutions: a hydrofluoric acid solution with a concentration of 49% hydrofluoric acid and water mixed in a volume ratio of 1:10 to 1:100; A mixed solution of hydrofluoric acid and ammonium fluoride formed by mixing hydrofluoric acid with a concentration of 49% and ammonium fluoride at a volume ratio of 5:1 to 500:1.

[0091] Preferably, the temperature required for the silicon oxynitride in the active region to be etched is 23°C±2°C.

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More