A method for removing interweaving and speed match

A rate matching and deinterleaving technology, applied in digital transmission systems, electrical components, error prevention, etc., can solve the problems of increasing circuit area and power consumption, reducing the capacity of the first interleaving RAM, and achieving low power consumption and saving The effect of capacity, simple algorithm

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

no. 1 Embodiment approach

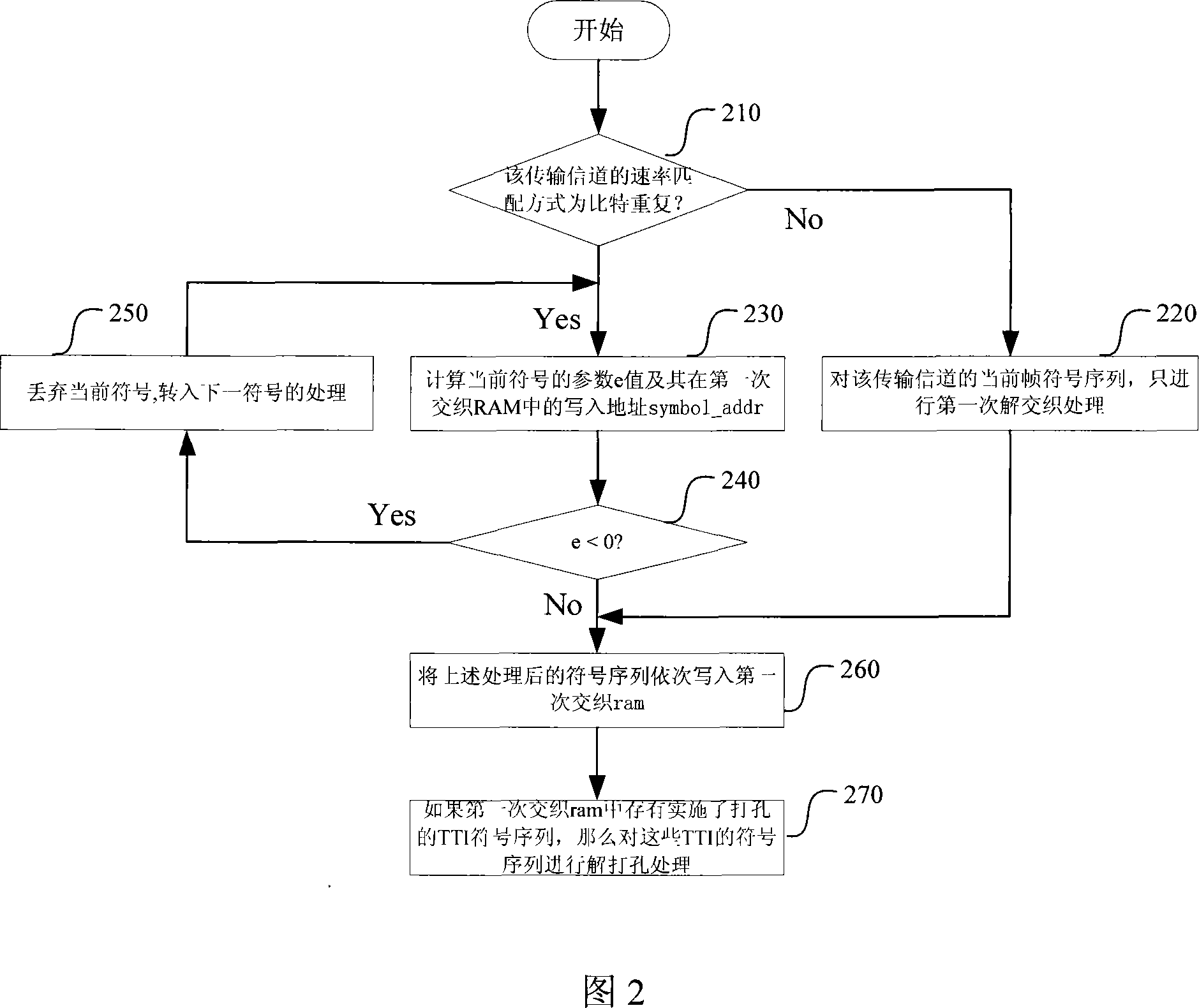

[0149] The first specific embodiment, as shown in Figure 2, comprises the following steps:

[0150] Step 210, judging the rate matching mode of the transmission channel, if it is the punching mode, then perform step 220; otherwise, perform step 230;

[0151] Step 220, perform the first deinterleaving process on the symbol sequence of the current frame of the transmission channel; execute step 260;

[0152] Step 230, calculate the parameter e value corresponding to the current symbol, and its write address symbol_addr in the first interleaving RAM;

[0153] Step 240, judging whether the e value corresponding to the current symbol is less than 0, if less than 0, then perform step 250, otherwise perform step 260;

[0154] Step 250, discard this symbol, and turn to the processing of the next symbol;

[0155] Step 260, write the above-mentioned processed symbols into the first interleaving RAM in sequence;

[0156] Step 270, if there are TTI symbol sequences subjected to punctur...

no. 2 Embodiment approach

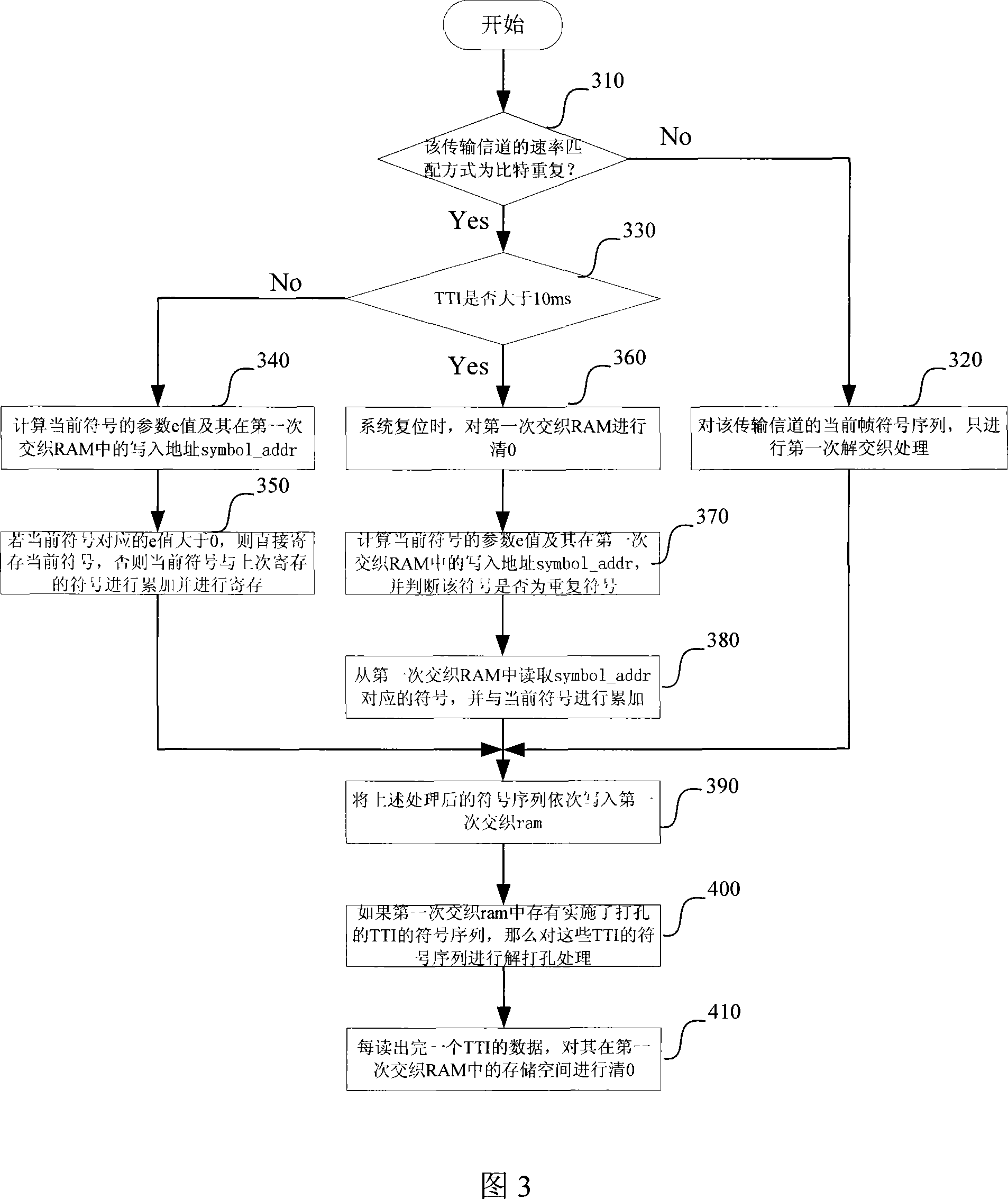

[0158] As shown in Figure 3, it includes the following steps:

[0159] Step 310, judging the rate matching mode of the transmission channel, if it is the punching mode, then perform step 320; otherwise, perform step 330;

[0160] Step 320, perform the first deinterleaving process on the symbol sequence of the current frame of the transmission channel; execute step 390;

[0161] Step 330, judging whether the TTI of the current transmission channel is greater than 10ms, if not greater than 10ms, then execute step 340; otherwise execute step 360;

[0162] Step 340, calculating the parameter e value of the current symbol and its write address symbol_addr in the first interleaving RAM;

[0163] Step 350, if the e value corresponding to the current symbol is greater than 0, then directly register the current symbol, otherwise the current symbol and the last registered symbol are accumulated and registered; perform step 390;

[0164] Step 360, when the system is reset, clear the in...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More - Generate Ideas

- Intellectual Property

- Life Sciences

- Materials

- Tech Scout

- Unparalleled Data Quality

- Higher Quality Content

- 60% Fewer Hallucinations

Browse by: Latest US Patents, China's latest patents, Technical Efficacy Thesaurus, Application Domain, Technology Topic, Popular Technical Reports.

© 2025 PatSnap. All rights reserved.Legal|Privacy policy|Modern Slavery Act Transparency Statement|Sitemap|About US| Contact US: help@patsnap.com