CPIC signal processing board

A signal processing board and processor technology, applied in the field of signal processing boards, can solve the problems of wasting board card PCB space, increasing system cost, increasing data transmission delay, etc.

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment 1

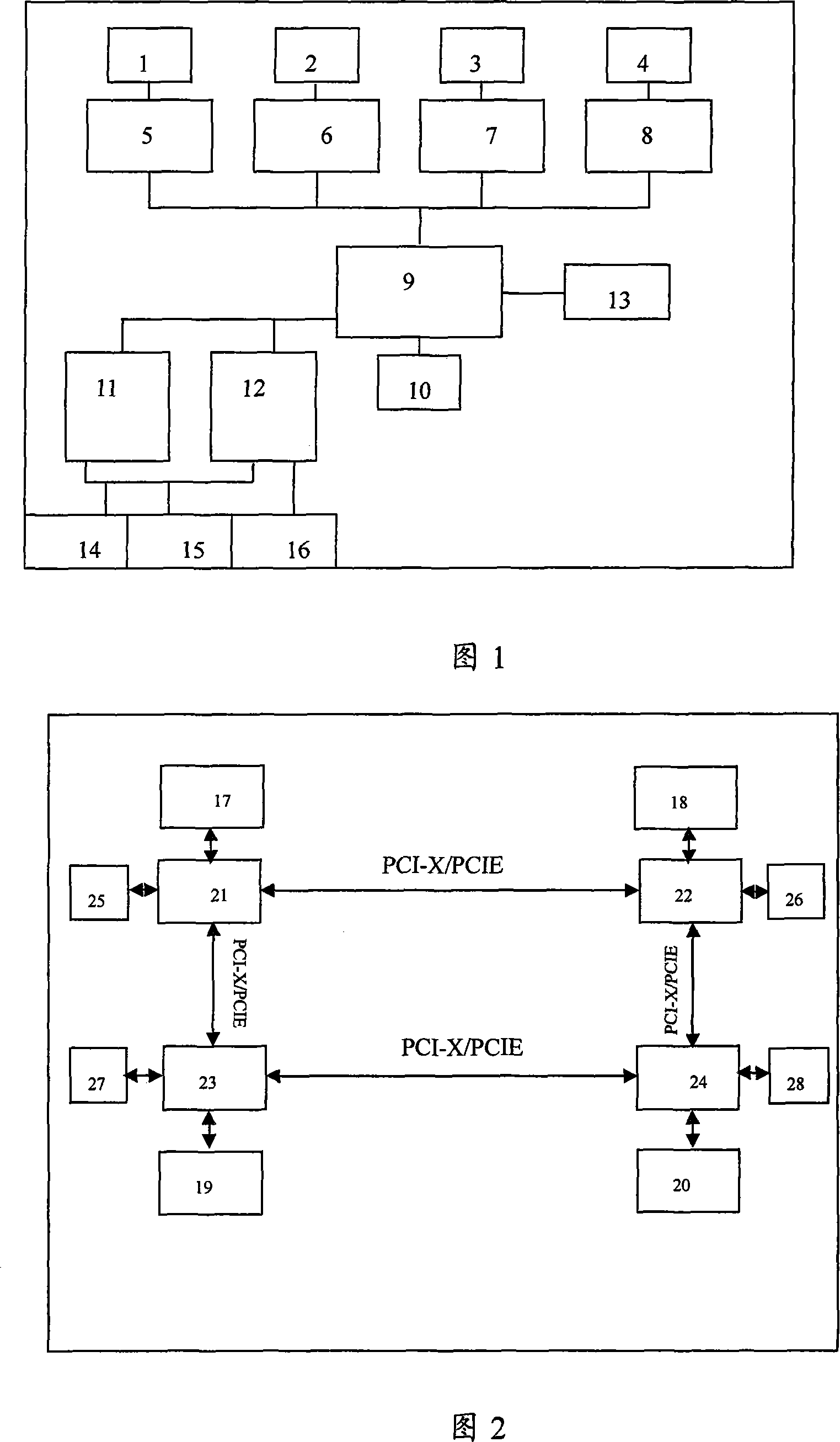

[0059] This embodiment is a 6U CPCI array signal processing board developed based on four Loongson 2E domestic general-purpose processors, and its structure diagram is shown in FIG. 1 . Four processors (i.e. the first processor 5, the second processor 6, the third processor 7, and the fourth processor 8 in Figure 1) are interconnected by sharing the SYSAD front-side bus, and each processor has a 256MB Local memory (i.e. the local memory chip 1 of the first processor in Fig. 1, the local memory chip 2 of the second processor, the local memory chip 3 of the third processor, the local memory chip 4 of the fourth processor), when The processor can use its own local memory to complete tasks assigned by the system. The north bridge chip 9 is connected with four processors through the front side bus, and the north bridge chip has a 128MB shared memory 10 for realizing the communication between the multiprocessors and the communication between the processor and the PCI device; the nor...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More