Thickness reduced multi-chip stacking and packaging construction

A multi-chip, wafer technology, applied in electrical components, electrical solid devices, circuits, etc., can solve the problems of peeling and separation, general products have no structure, poor adhesion of electroplating layers, etc., and achieve the effect of improving support.

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

no. 1 Embodiment

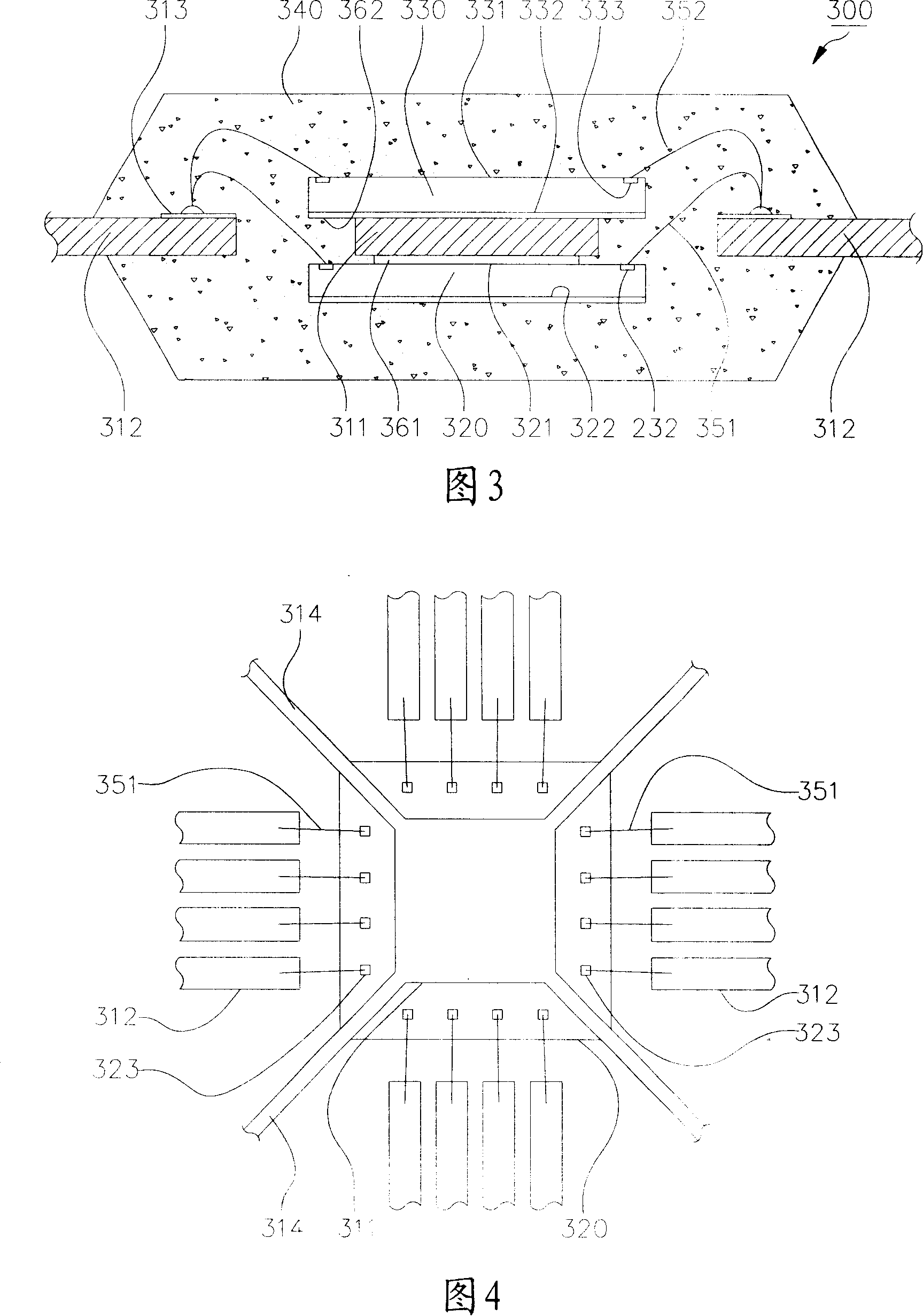

[0067] Please refer to FIG. 3 , which is a schematic cross-sectional view of a multi-chip stack package structure according to the first embodiment of the present invention. In the first embodiment of the present invention, a multi-die stacked package structure 300 mainly includes a spacer pad 311 (spacer pad) of a leadframe, a plurality of pins 312, a first chip 320, a first Two wafers 330 and a package of colloid 340 .

[0068] The spacer seat 311 and the pins 312 are cut from the same lead frame, and are made of metal, such as copper, iron or their alloys. Usually, the shape of the spacing seat 311 is like a traditional die pad or chip paddle, but the size may be slightly smaller.

[0069] The first chip 320 has a first active surface 321 and a first back surface 322 , and a plurality of first electrodes 323 (as shown in FIG. 4 ) are formed on the first active surface 321 . The first electrodes 323 can be electrically connected to some of the pins 312 by a plurality of fi...

no. 2 Embodiment

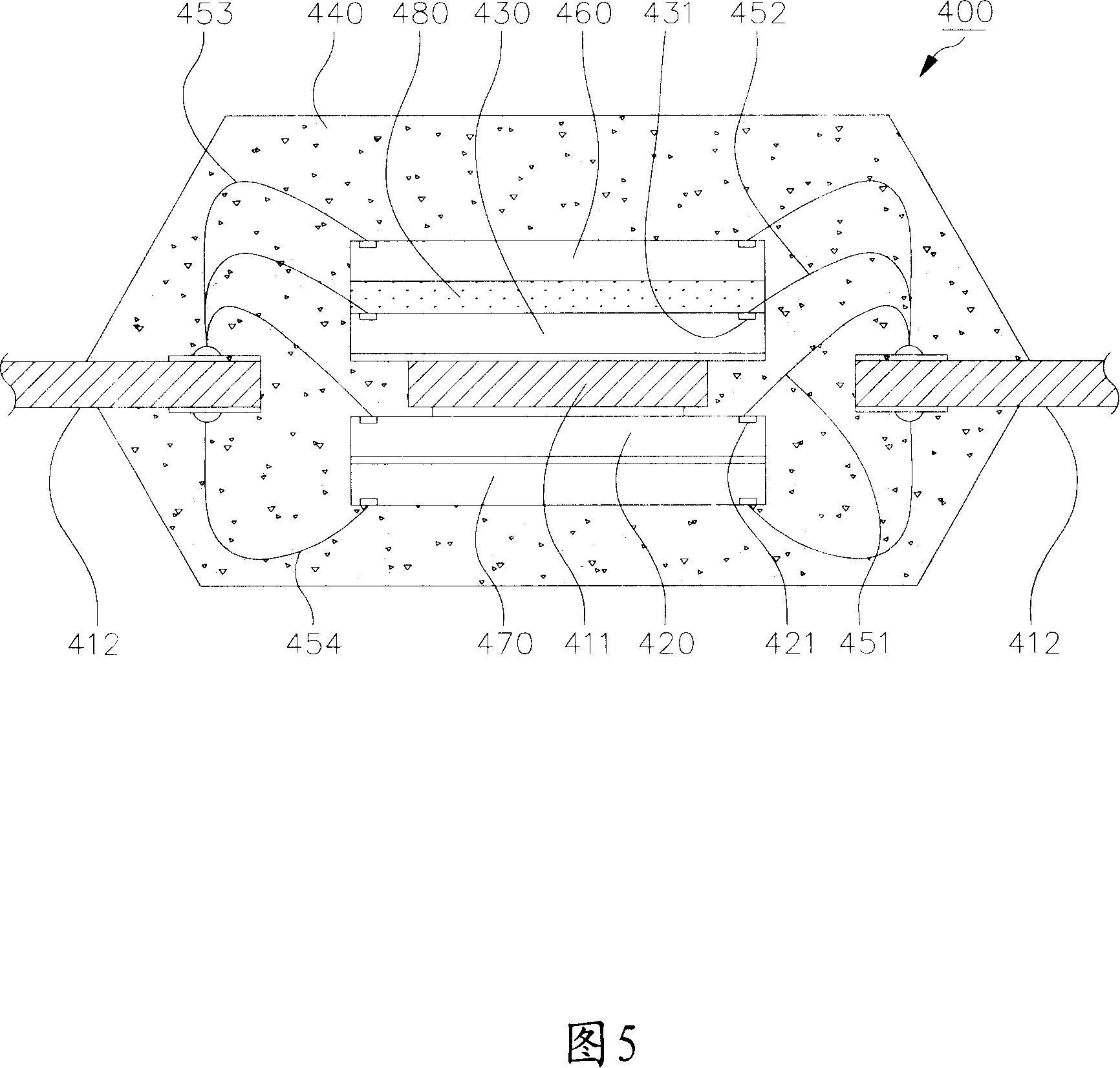

[0079] Please refer to FIG. 5 , which is a schematic cross-sectional view of another multi-chip stack package structure according to the second embodiment of the present invention. The invention is not limited to the number of sealed wafers. Another multi-chip stack package structure 400 disclosed in the second embodiment of the present invention, in addition to including a spacer seat 411 of a lead frame and a plurality of pins 412, a first chip 420, a second chip 430 and The encapsulant 440 has substantially the same components as the first embodiment, and further includes a third chip 460 and / or a fourth chip 470 and so on.

[0080] A plurality of first electrodes 421 are formed on the active surface of the first chip 420 , and are electrically connected to some of the pins 412 by a plurality of first bonding wires 451 .

[0081]A plurality of second electrodes 431 are formed on the active surface of the second chip 430 , and are electrically connected to some of the pins ...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More