Processor system

一种处理器系统、处理器的技术,应用在数据处理电源、电数字数据处理、仪器等方向,能够解决很难处理能力等问题,达到低功耗的效果

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

no. 1 example

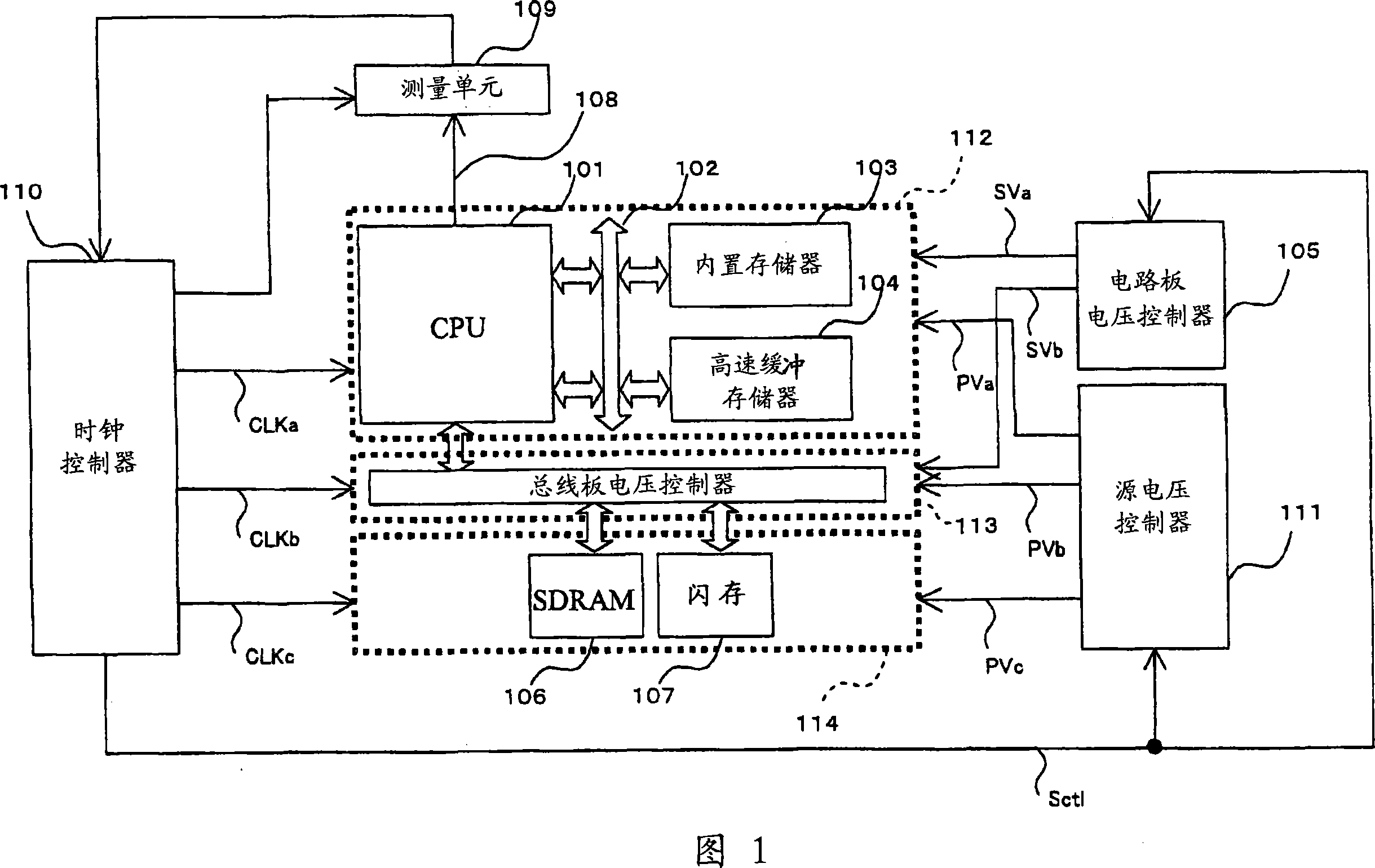

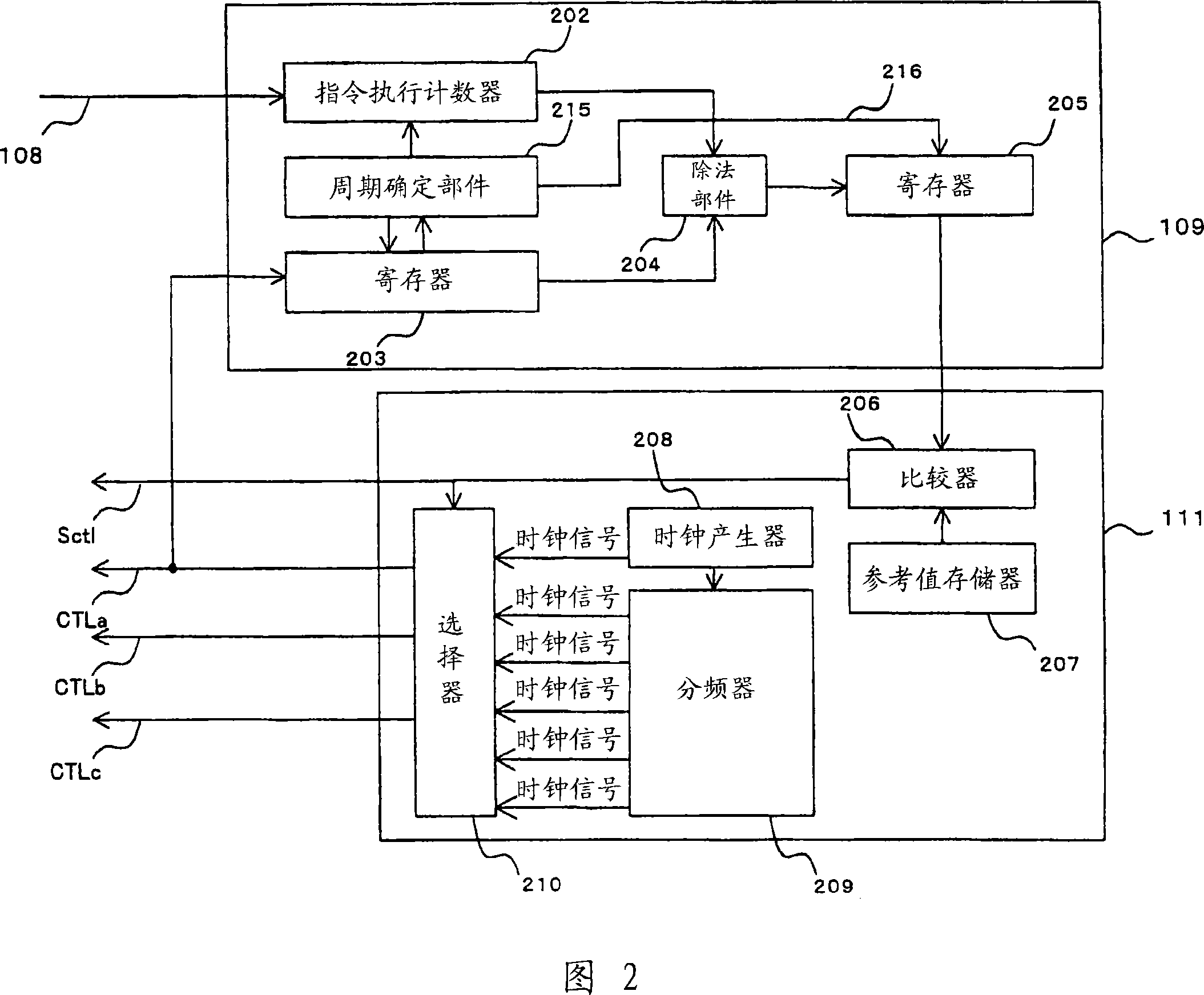

[0019] FIG. 1 is a block diagram illustrating a processor system of a first embodiment. As shown in FIG. 1, the processor system of the first embodiment includes a processor block 112, a bus controller 113, an external device 114, a measurement unit 109, a clock controller 110, a source voltage controller 111, and a board voltage controller 105. . The processor block 112 includes a CPU 101 , a built-in memory 103 , and a cache memory 104 interconnected by an internal bus 102 . The bus controller 113 controls external buses connected to the CPU 101 and external devices 114 . External device 114 includes SDRAM 106 and flash memory 107 .

[0020] The CPU 101 can access the built-in memory 103 or the cache memory 104 through the internal bus 102 by using a small number of processing cycles. Meanwhile, the CPU 101 can access the external device 114 via the external bus, but this access requires a greater number of processing cycles than the number of processing cycles required f...

no. 2 example

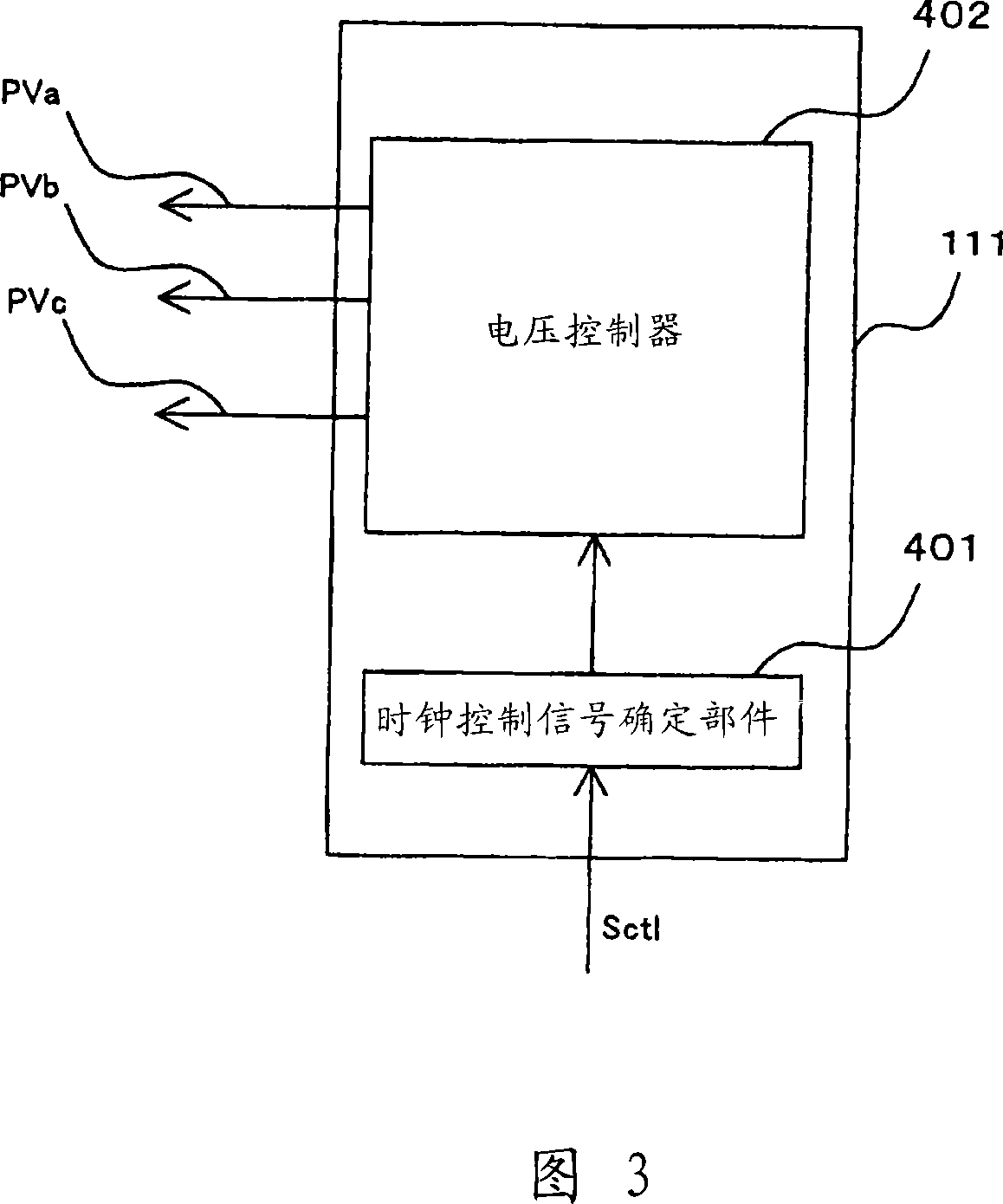

[0045] FIG. 4 is a block diagram illustrating an internal configuration of a measurement unit and a clock controller included in the processor system of the second embodiment. The processor system of the second embodiment differs from that of the first embodiment in the measurement unit. Other than that, the second embodiment is the same as the first embodiment. In FIG. 4 , elements common to those in FIG. 1 are referred to by the same reference numerals.

[0046] The measurement unit 309 of the present embodiment has a task information processing section 301 instead of the cycle determination section 215 included in the measurement unit 109 of the first embodiment. Job information 302 is input from the CPU 101 to the job information processing section 301 . A task is defined as an execution unit executed by an operating system installed in the processor system of the present embodiment, and includes a plurality of program functions. The task information may be an identific...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More