Metal-oxide-semiconductor transistor and manufacturing method thereof

A technology of oxide semiconductors and transistors, applied in semiconductor/solid-state device manufacturing, semiconductor devices, electrical components, etc., can solve the problems of destroying the operation of P-type metal oxide semiconductor transistors and limited improvement effects, so as to improve operating efficiency and high The effect of drive current

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment Construction

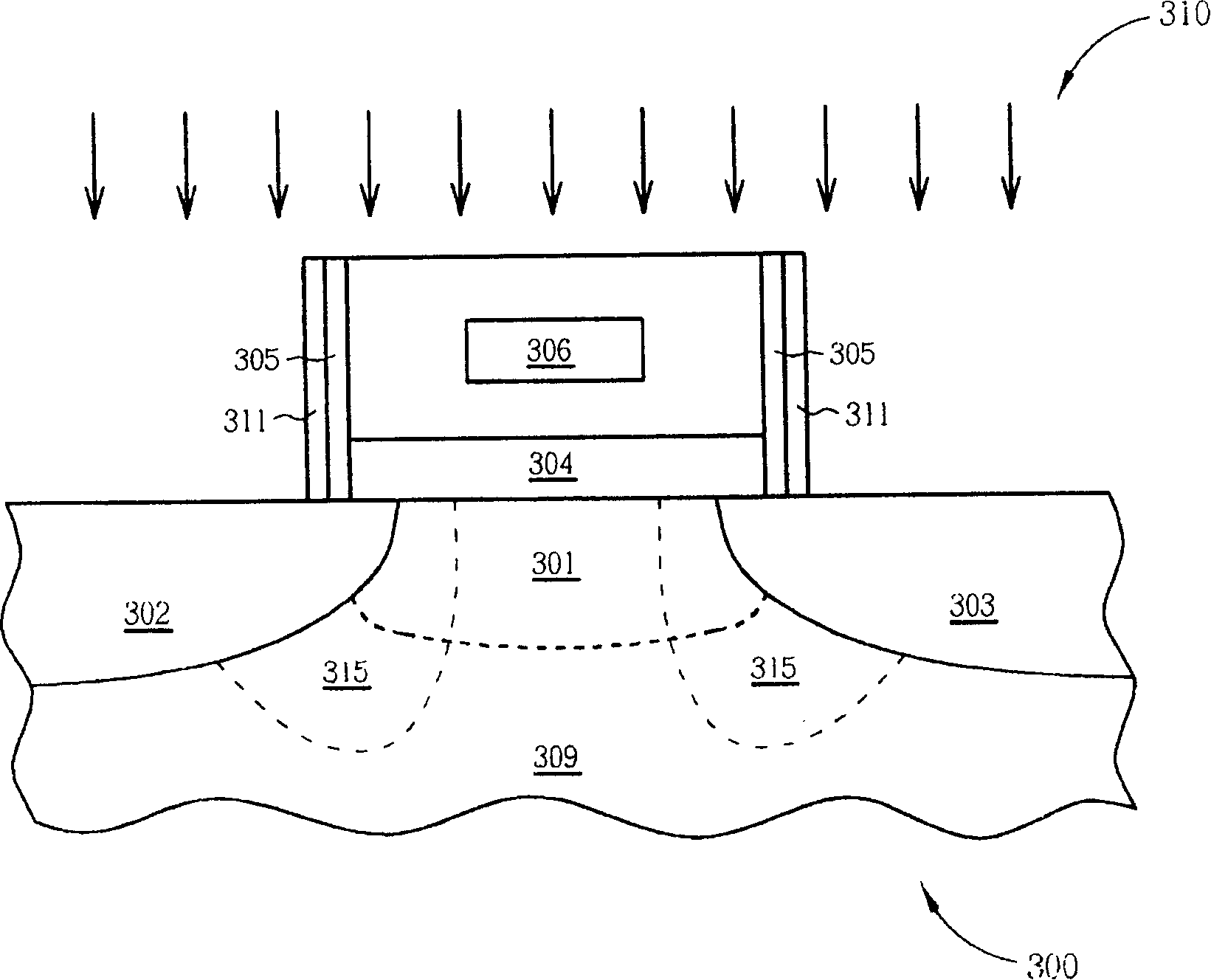

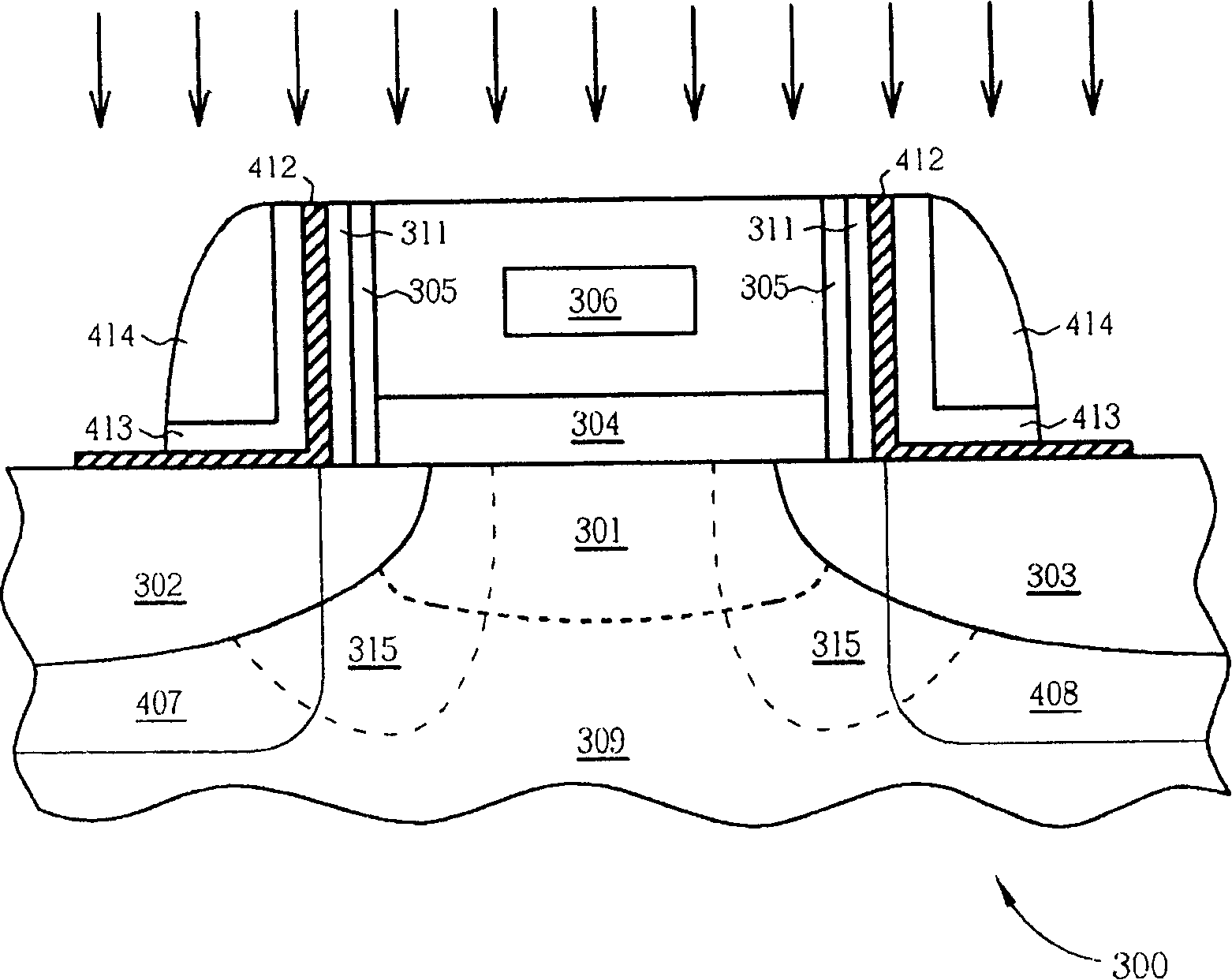

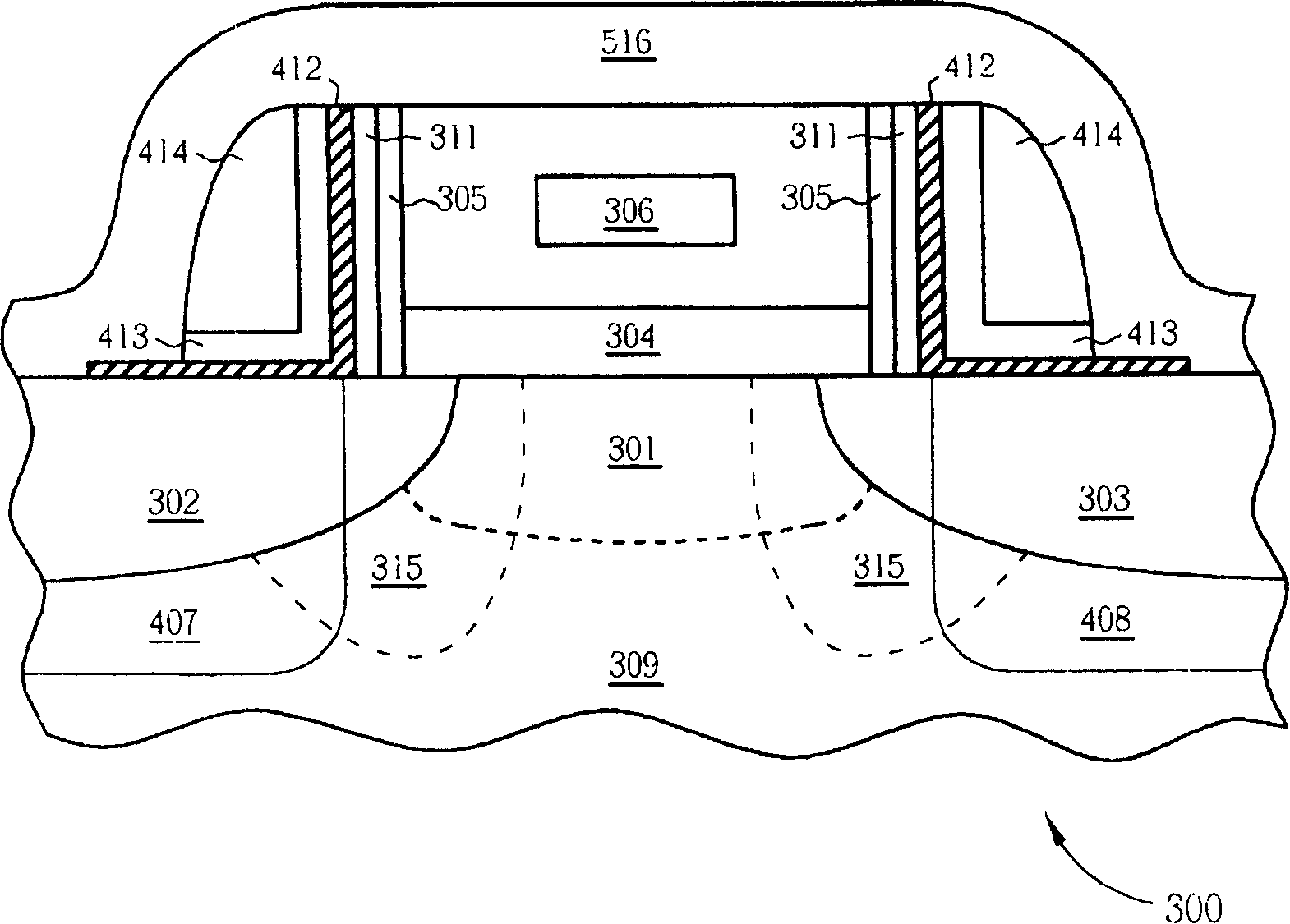

[0043] Please refer to FIG. 7 to FIG. 13 , which are schematic cross-sectional views of the method for manufacturing metal oxide semiconductor transistors according to the first preferred embodiment of the present invention, wherein the same elements or parts are still represented by the same symbols. It should be noted that the drawings are for illustration purposes only and are not drawn to original scale. In addition, in FIGS. 7 to 13 , the photolithography and etching processes for the parts related to the present invention are well known to those skilled in the art, so they are not explicitly shown in the figures.

[0044] The present invention relates to a method for fabricating metal oxide semiconductor transistors in integrated circuits, applicable to N-type metal oxide semiconductor transistors and P-type metal oxide semiconductor transistors. In order to describe in detail, FIGS. 7 to 13 are particularly The metal-oxide-semiconductor transistor process located in dif...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More