Semiconductor package structure and manufacturing method thereof

A technology of packaging structure and manufacturing method, applied in semiconductor/solid-state device manufacturing, semiconductor devices, semiconductor/solid-state device components, etc., can solve the problems of increasing power consumption, unable to ensure stable control of characteristic impedance, and increasing thermal resistance, etc. Effects of reducing parasitic impedance and inductance, improving reliability, and reducing thermal resistance

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment Construction

[0025] The semiconductor package structure of the present invention will be described below with reference to the drawings, and the semiconductor package structure of the present invention and its manufacturing method will be described in detail with reference to the structural schematic diagrams shown in FIGS. 1 to 6 . It should be noted here that "up" and "down" here refer to the directions shown in the relevant drawings, and are mainly tentative directional terms for the description herein, and are not used to limit the present invention.

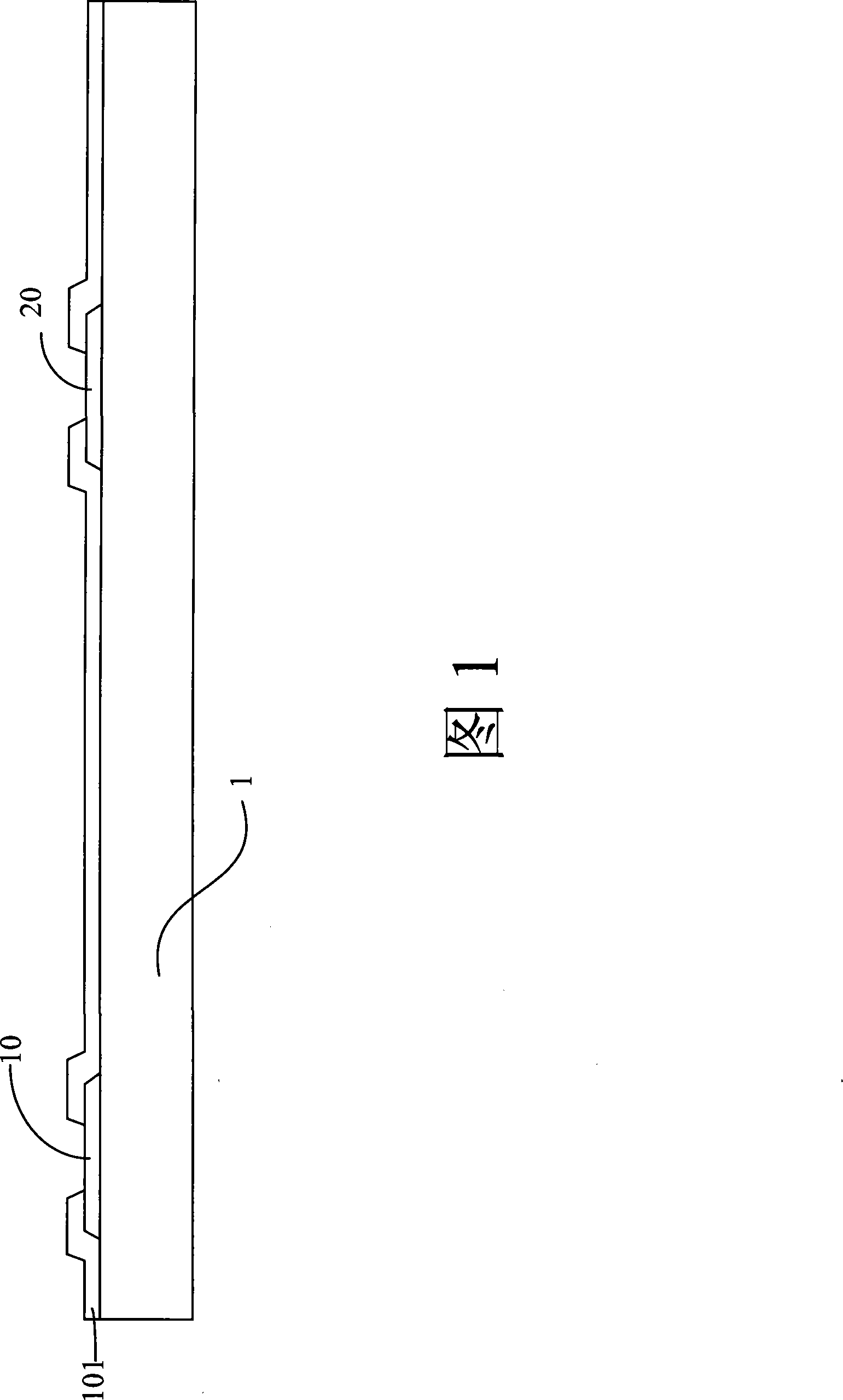

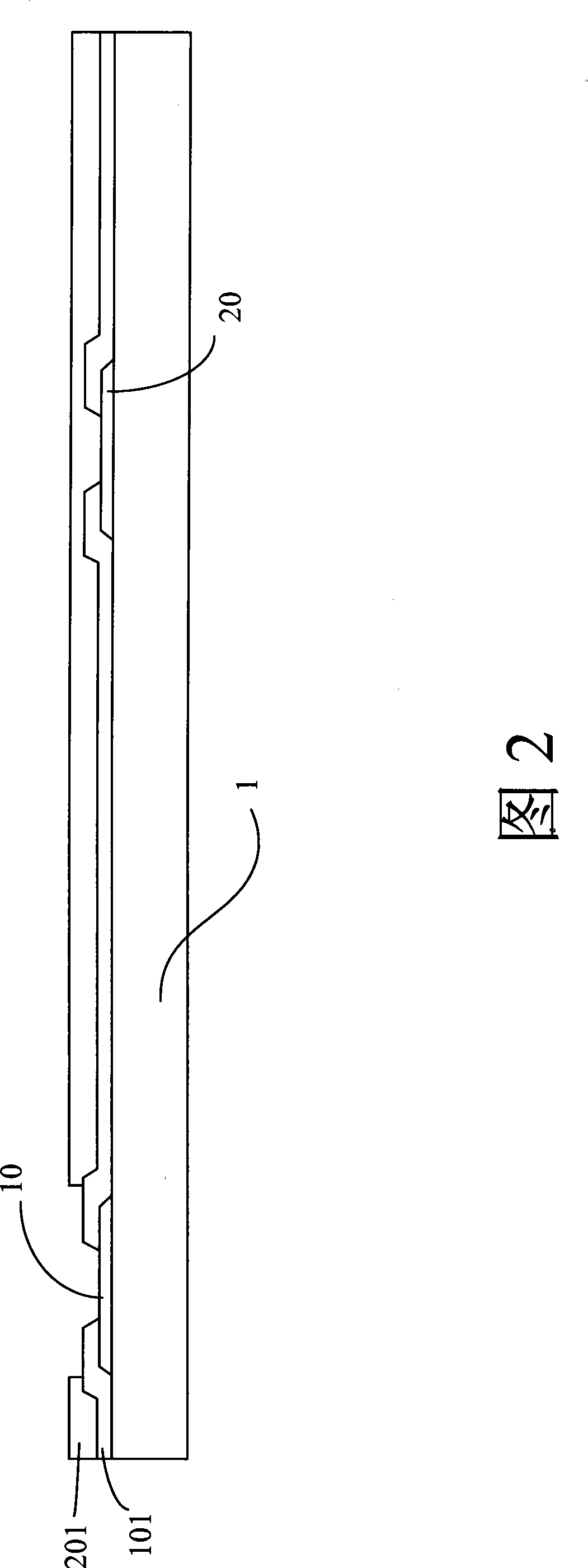

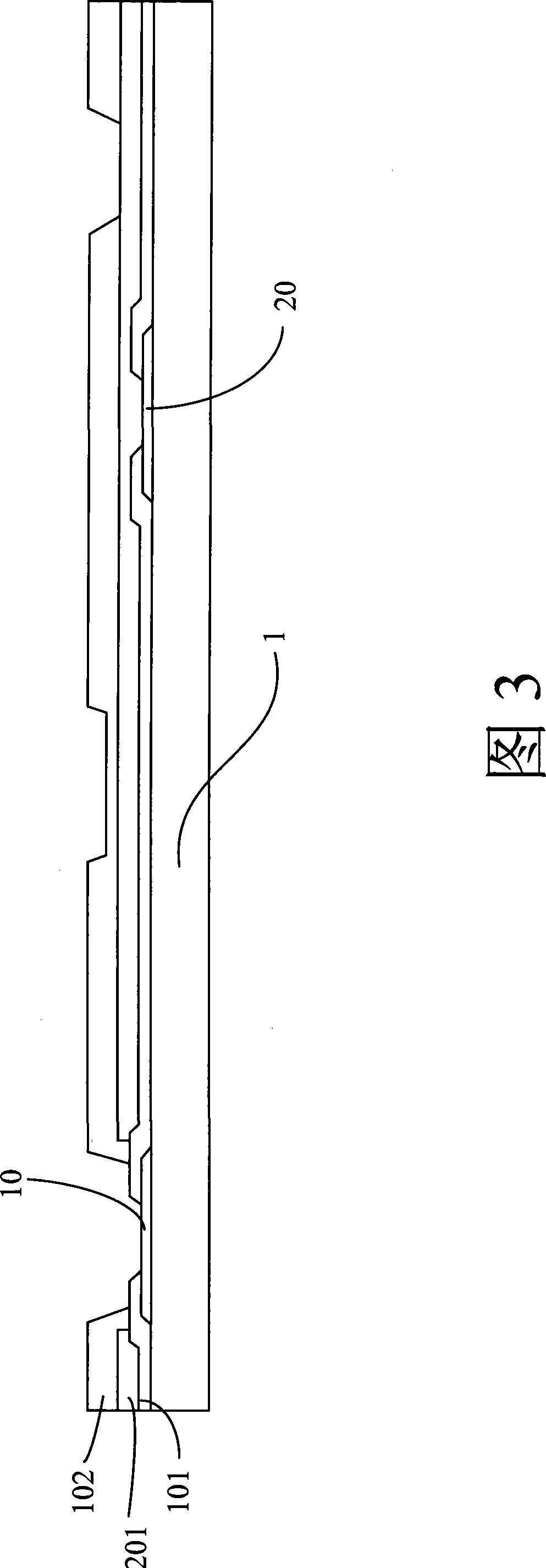

[0026] FIG. 1 schematically shows the structure after the first protective layer is formed according to the manufacturing method of the semiconductor package structure of the present invention. As shown in FIG. 1 , firstly, a semiconductor substrate 1 is provided, such as a wafer, having a surface 100 with at least one first pad 10 and at least one second pad 20 thereon. Then a first protection layer 101 is formed to cover the surface 10...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More