Method for making strain silicon CMOS transistor

An oxide semiconductor, complementary technology, applied in semiconductor/solid-state device manufacturing, electrical components, circuits, etc., can solve problems such as PMOS damage, PMOS transistor damage, PMOS transistor drive current drop, etc., to improve operating performance and ensure reliability Acceleration, the effect of increasing the drift rate

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment Construction

[0024] In order to highlight the advantages and features of the present invention, a number of preferred embodiments of the present invention are listed below, and are described in detail in conjunction with the drawings as follows:

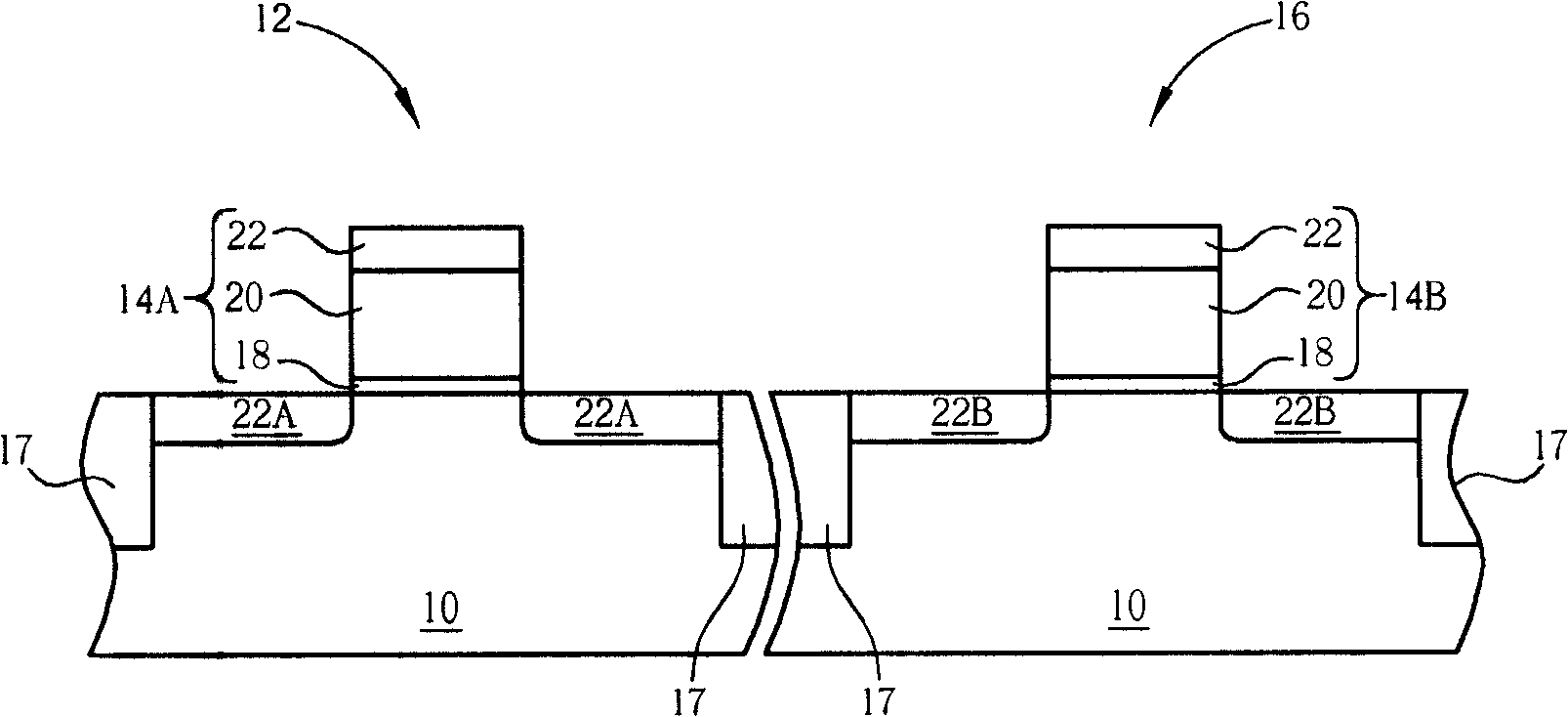

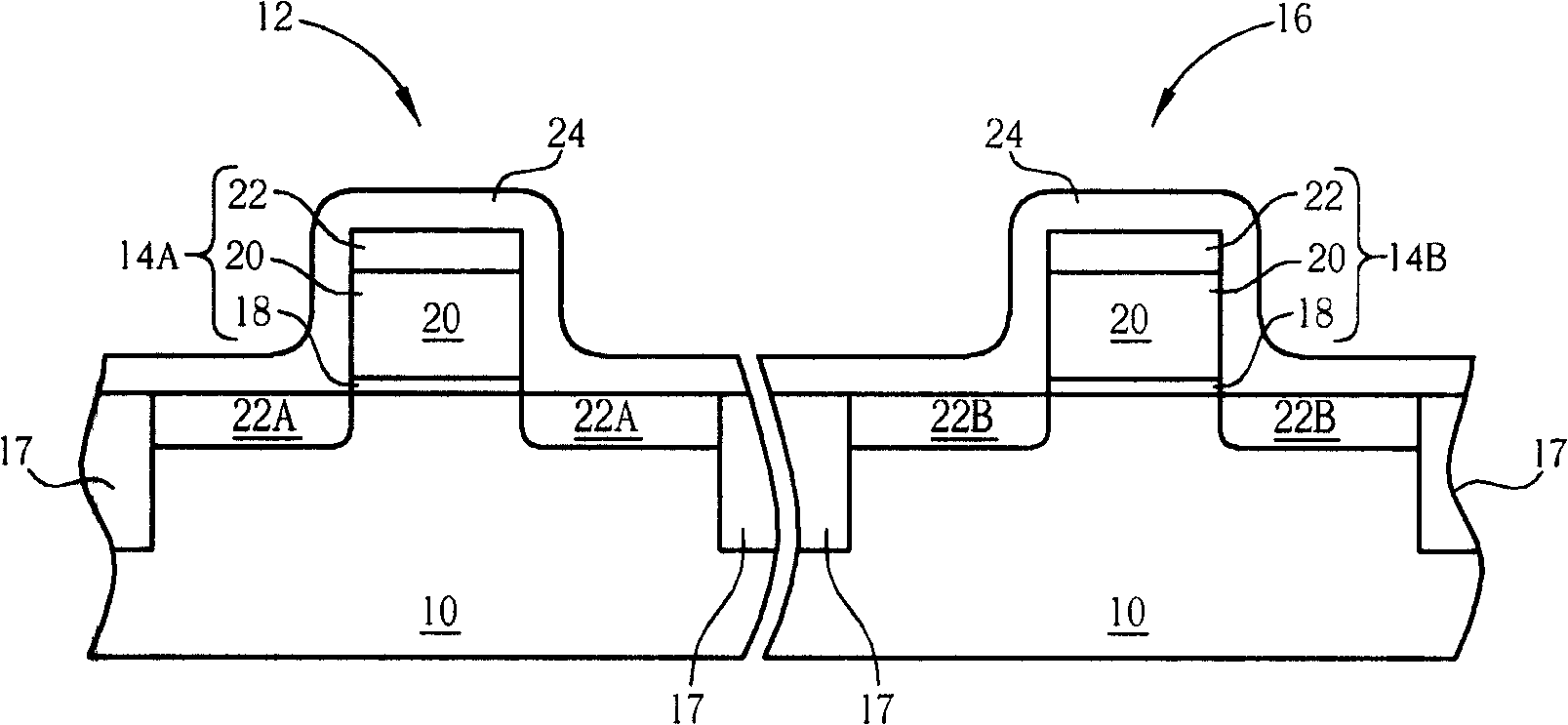

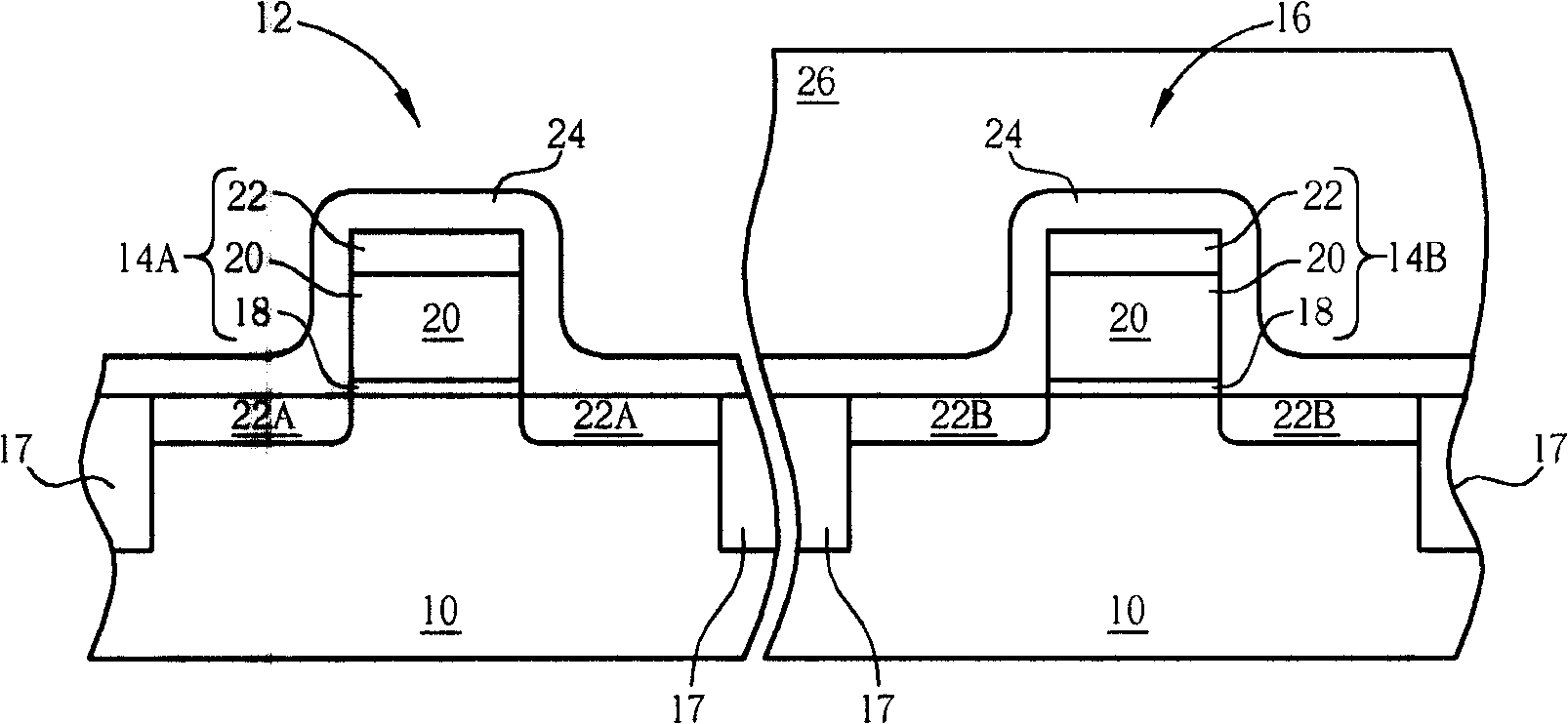

[0025] Please refer to Figure 1 to Figure 7 , Figure 1 to Figure 7 It is a schematic diagram illustrating each step of manufacturing a strained silicon CMOS transistor according to the first preferred embodiment of the present invention. Such as figure 1 As shown, firstly, a semiconductor substrate 10 is provided, and the semiconductor substrate 10 can be silicon, a strained silicon substrate, a compound semiconductor, a silicon-on-insulator substrate or a combination thereof. The semiconductor substrate 10 can be individually formed on the semiconductor substrate 10 by methods known to those skilled in the art, such as masking process, ion implantation process and rapid thermal annealing (rapid thermal annealing, hereinafter referred to as RT...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More