Metal silication technique for metal-oxide-semiconductor transistor and transistor construction

An oxide semiconductor and metal silicidation technology, which is applied in semiconductor devices, semiconductor/solid-state device manufacturing, electrical components, etc., can solve the problems of difficult control, complicated chemical mechanical polishing process steps, etc., and achieve the effect of easy control and simple process

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment Construction

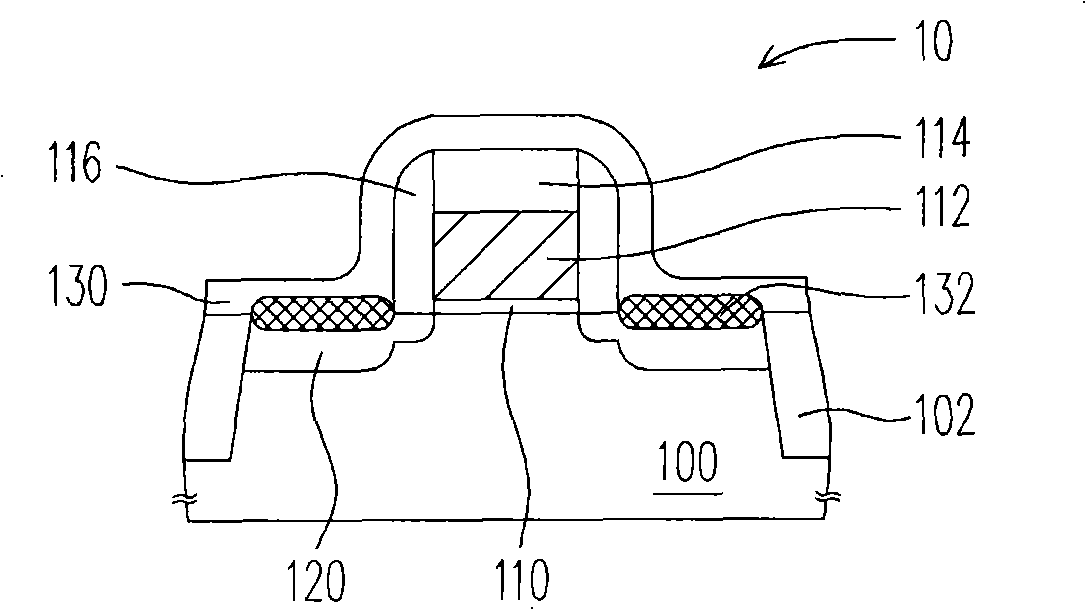

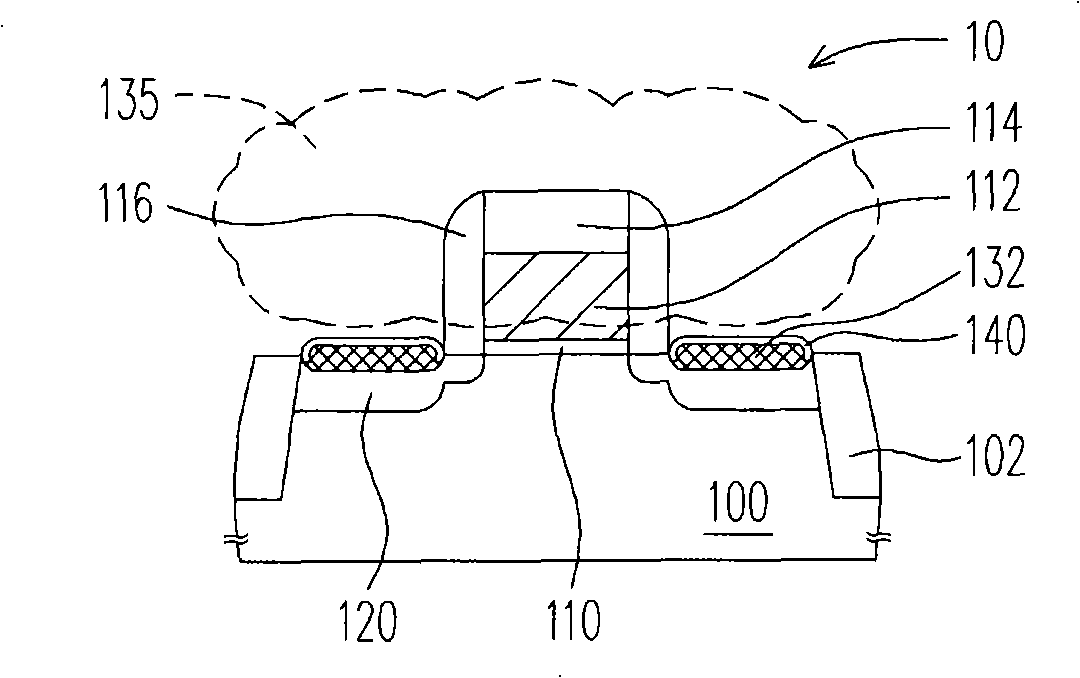

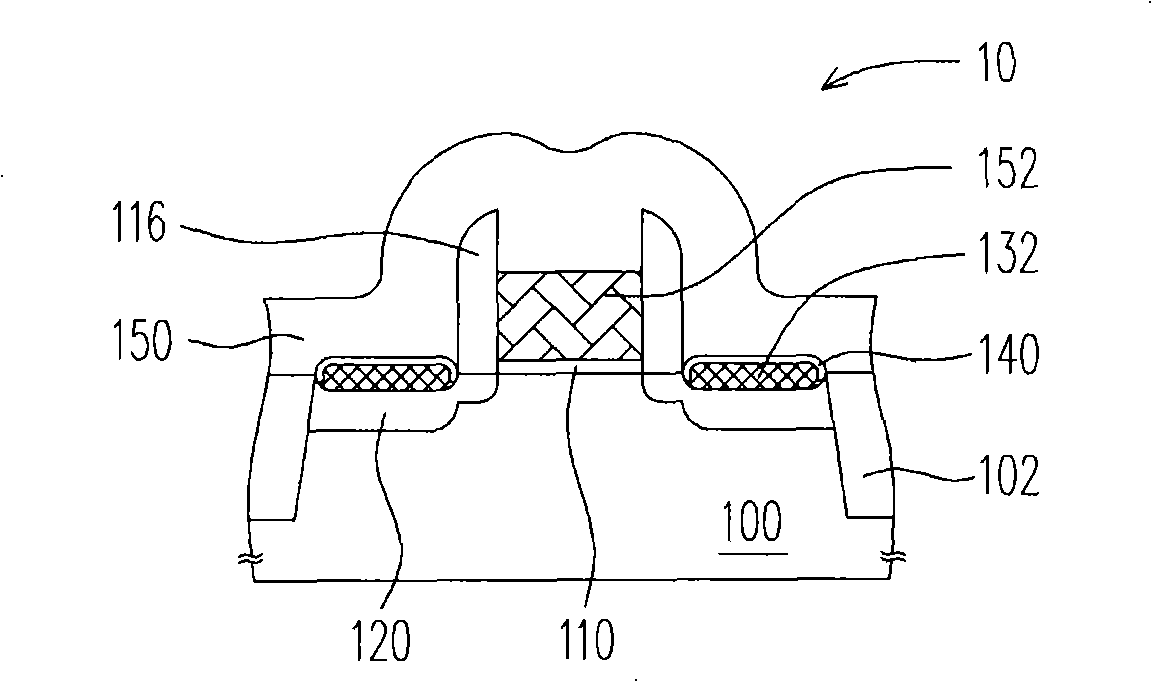

[0026] Figure 1~3 A cross-sectional flow diagram illustrating a metal silicide process for a metal oxide semiconductor transistor according to a preferred embodiment of the present invention.

[0027] Please refer to figure 1 , first provide a metal oxide semiconductor transistor 10, which includes a silicon substrate 100 formed with an isolation layer 102, a gate dielectric layer 110 on the silicon substrate 100, a silicon gate 112 on the gate dielectric layer 110, and a silicon gate 112 on the silicon gate 112. The top cap layer 114 , the spacer 116 between the silicon gate 112 and the sidewall of the top cap layer 114 , and the source / drain region 120 in the substrate 100 next to the silicon gate 112 . Wherein, the silicon substrate 100 is, for example, a lightly P-type or lightly N-type doped silicon substrate, the gate dielectric layer 110 is, for example, a gate oxide layer, and the material of the silicon gate 112 is, for example, polysilicon.

[0028] In addition, t...

PUM

Login to view more

Login to view more Abstract

Description

Claims

Application Information

Login to view more

Login to view more - R&D Engineer

- R&D Manager

- IP Professional

- Industry Leading Data Capabilities

- Powerful AI technology

- Patent DNA Extraction

Browse by: Latest US Patents, China's latest patents, Technical Efficacy Thesaurus, Application Domain, Technology Topic.

© 2024 PatSnap. All rights reserved.Legal|Privacy policy|Modern Slavery Act Transparency Statement|Sitemap