Integration process flow for flash devices with low gap fill aspect ratio

A technology of isolation structure and shallow trench, applied in the process of forming it, the structure of memory cells and the field of memory cell arrays

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment Construction

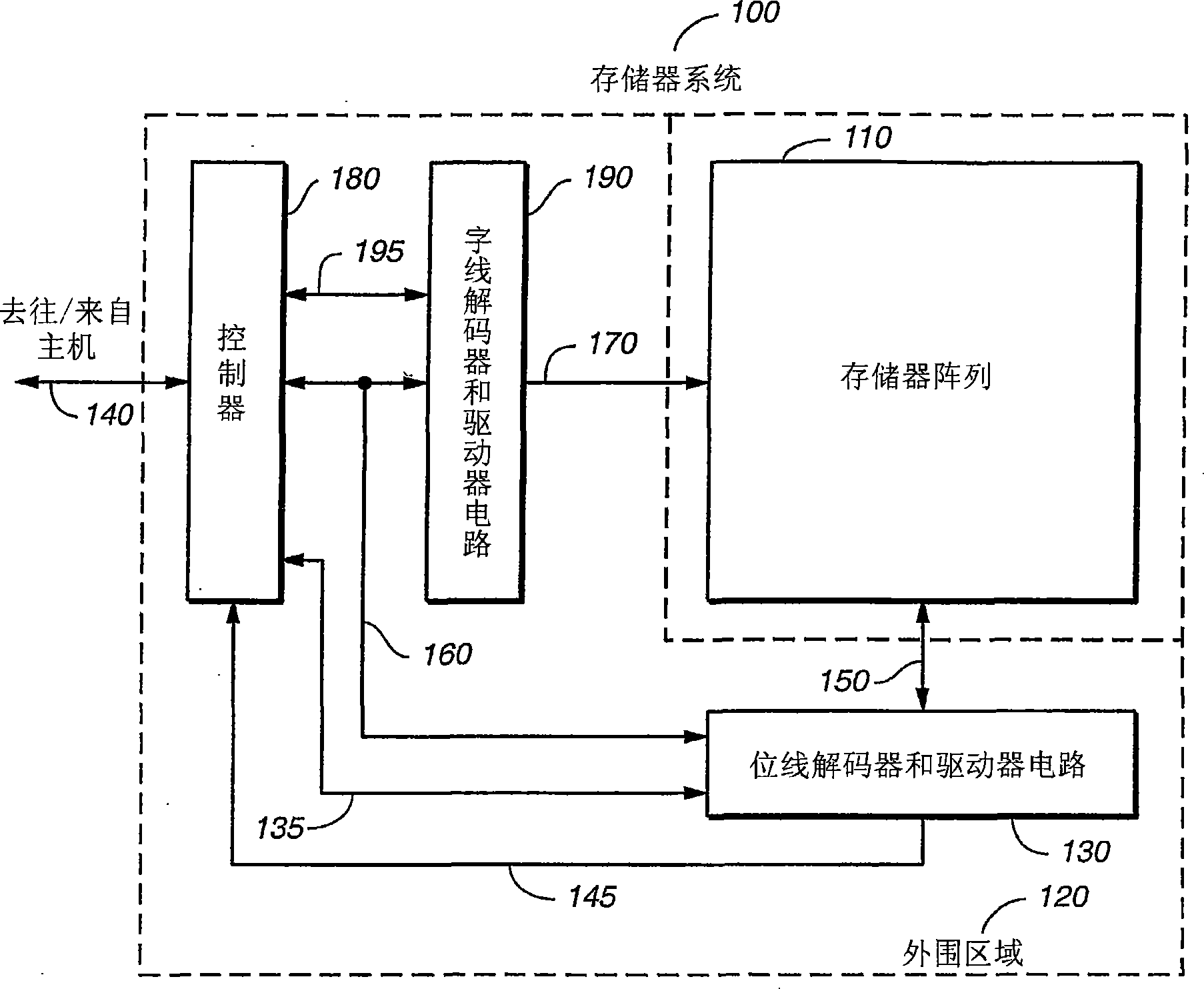

[0037] exist figure 1 An example of a memory system 100 incorporating various aspects of the present invention is generally illustrated in the block diagram of . A large number of individually addressable memory cells are arranged in a regular array of rows and columns 110, although other physical cell arrangements are of course possible. It is specified here that the bitlines extending along the columns of the array 110 are electrically connected to the bitline decoder and driver circuit 130 by lines 150 . Wordlines specified in this description to extend along a row of array 110 are electrically connected to wordline decoder and driver circuit 190 by line 170 . Each of decoders 130 and 190 receives memory cell addresses from memory controller 180 over bus 160 . The decoder and driver circuits are also connected to the controller 180 via respective control and status signal lines 135 and 195 .

[0038] The controller 180 can be connected to a host device (not shown) throu...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More