Method for reinforcing MOS device channel region strain

A technology for MOS devices and channel regions, applied in semiconductor/solid-state device manufacturing, electrical components, circuits, etc., can solve problems such as high cost, low cost, complex process, etc., to improve performance, increase strain, and improve device performance Effect

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment 1

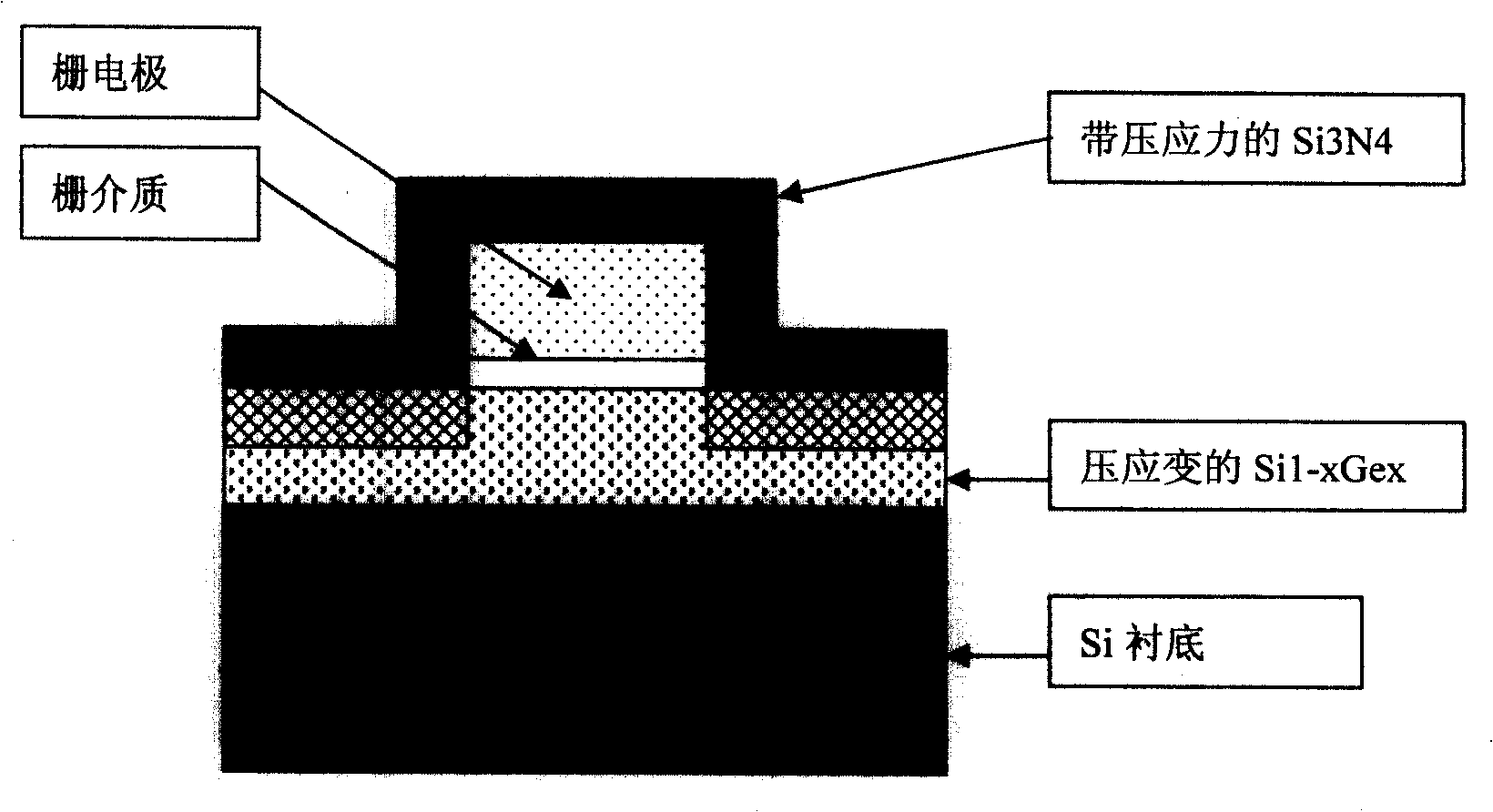

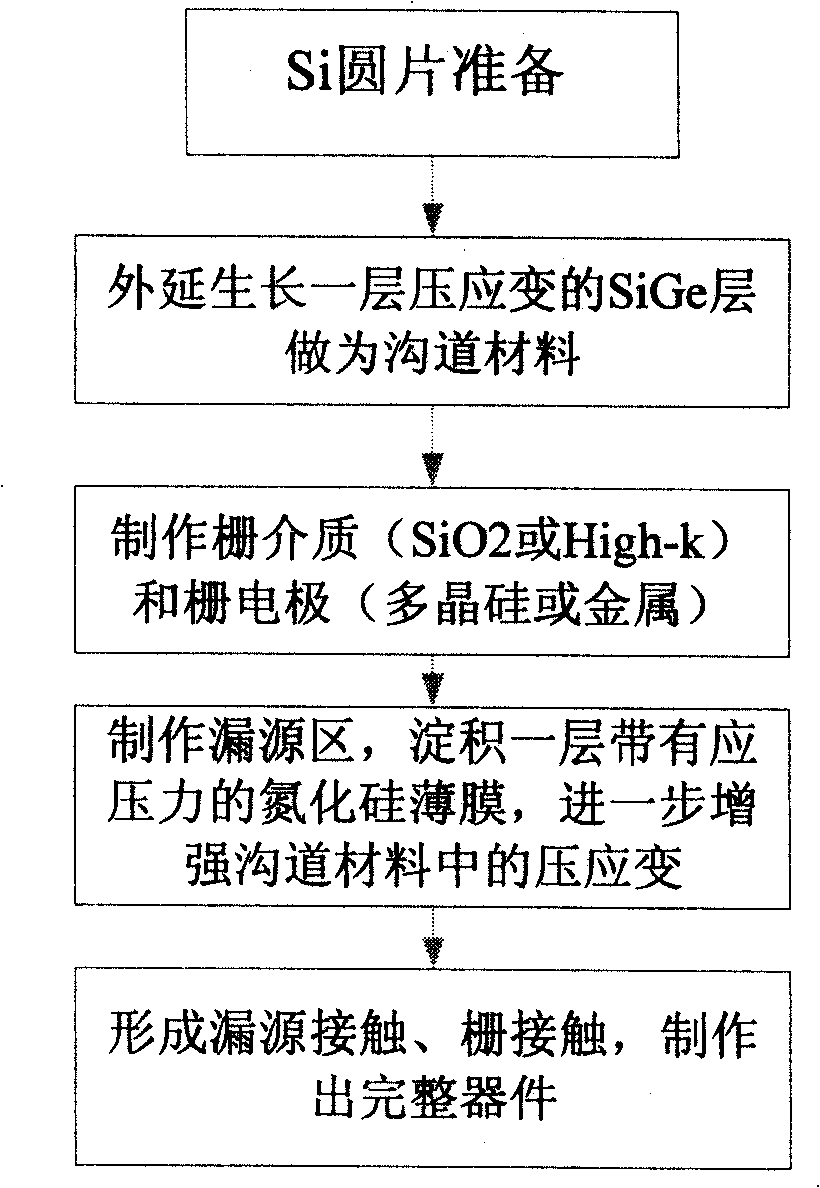

[0022] Embodiment 1: PMOS transistor with SiGe channel. A layer of compressively strained SiGe is epitaxially used as the channel layer on the silicon substrate, and a layer of High-k dielectric is deposited on it by ALD as the gate dielectric, and then a metal gate is deposited, and then a layer of nitrogen with compressive stress is deposited. Si 3 N 4 The strain degree of the channel layer is further enhanced to improve performance (in Example 1).

Embodiment 2

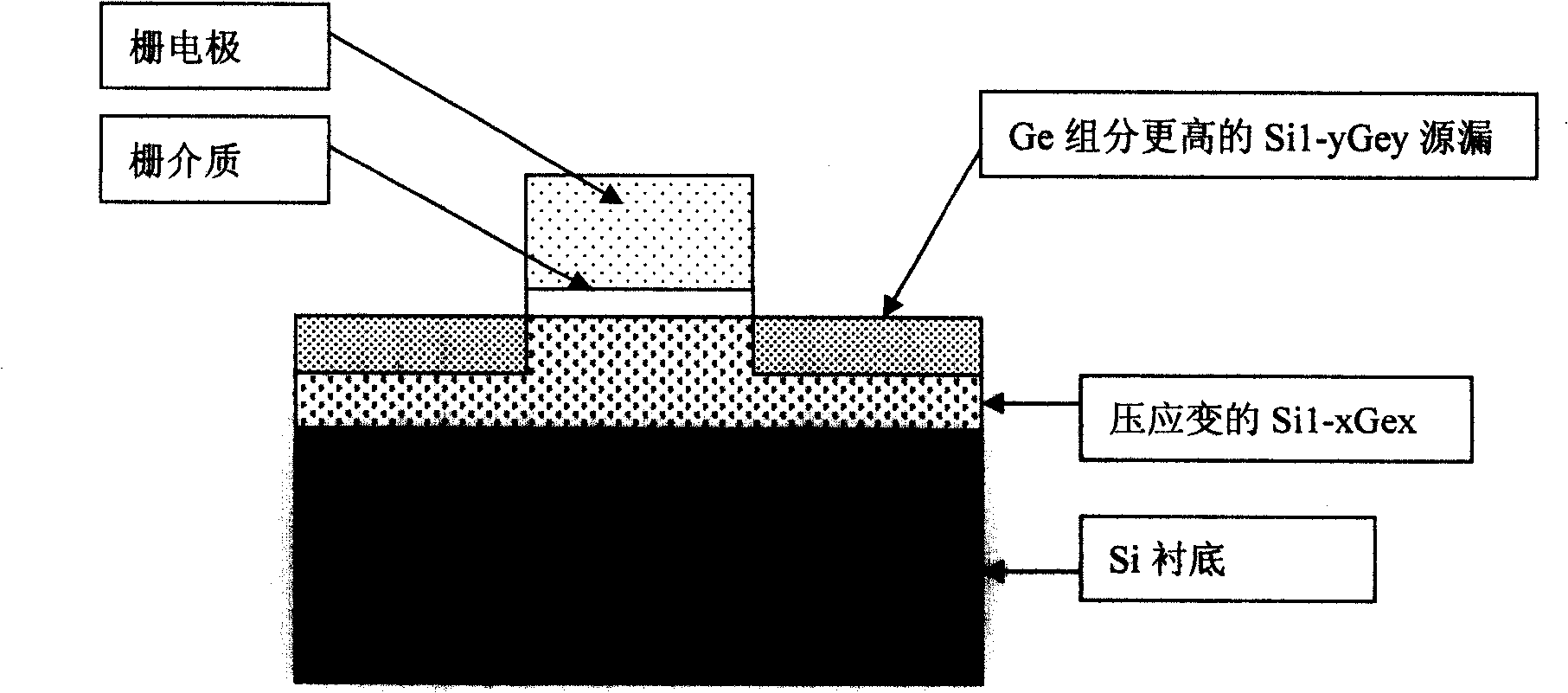

[0023] Embodiment 2: PMOS transistor with SiGe channel. A layer of strained SiGe is epitaxially used as the channel layer on the silicon substrate, and a layer of High-k dielectric is deposited on it by ALD as the gate dielectric, and then the metal gate is deposited, and then the source and drain are etched to remove the SiGe in the source and drain regions , and then grow a silicon germanium layer with a higher Ge content in the source and drain regions, squeeze the channel region material, and further introduce compressive stress in the channel to enhance strain and improve performance.

Embodiment 3

[0024] Embodiment 3: CMOS process on SOI composed of SIGe material PMOS and strained silicon NMOS. First, use Bonding or other methods to obtain a high-quality relaxed SiGe layer on the insulating layer as a virtual substrate, and then define a certain area on it by photolithography, and epitaxially grow a compressively strained SiGe layer with higher Ge content As the PMOS tube area, a layer of tensile strained Si layer is deposited in other areas as the NMOS tube area, and STI is used to isolate the two areas. PMOS transistors and NMOS transistors are fabricated in two regions respectively. Then deposit a layer of Si with compressive stress on the PMOS tube 3 N 4 The thin film introduces greater compressive stress in the channel region, and deposits a layer of Si with tensile stress on the NMOS tube. 3 N 4 The thin film introduces greater tensile stress in the NMOS channel region, so that high-performance PMOS tubes and NMOS tubes can be obtained at the same time, formin...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More