Method for forming fine pattern of semiconductor device

一种精细图案、半导体的技术,应用在半导体/固态器件制造、电气元件、电路等方向,能够解决覆盖对准不良、无法获得图案等问题,达到改善覆盖对准不良的效果

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment Construction

[0025] Hereinafter, the present invention will be described in detail with reference to the accompanying drawings.

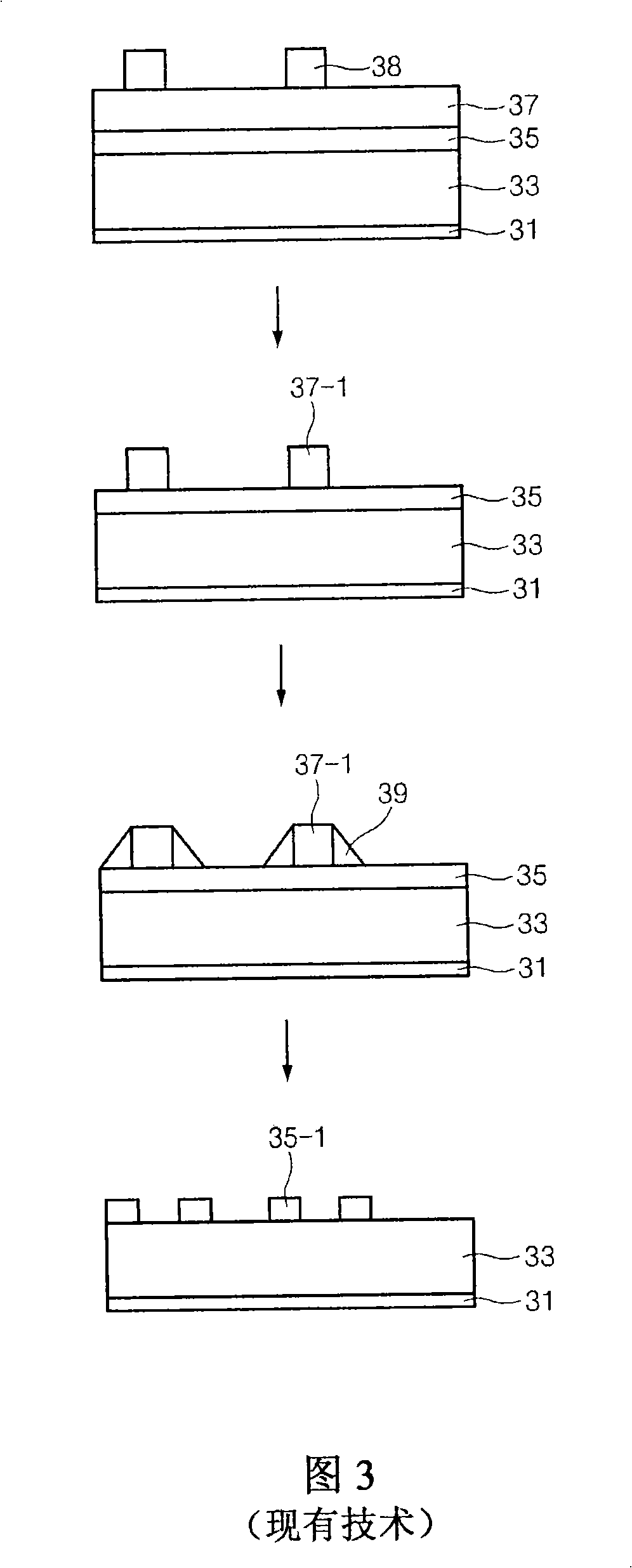

[0026] To prevent overlay and misalignment, two methods have been developed: i) Double Exposure Etching Technology (DEET) and ii) Spacer Patterning Technology (SPT), which have been used in the fabrication process of semiconductor devices.

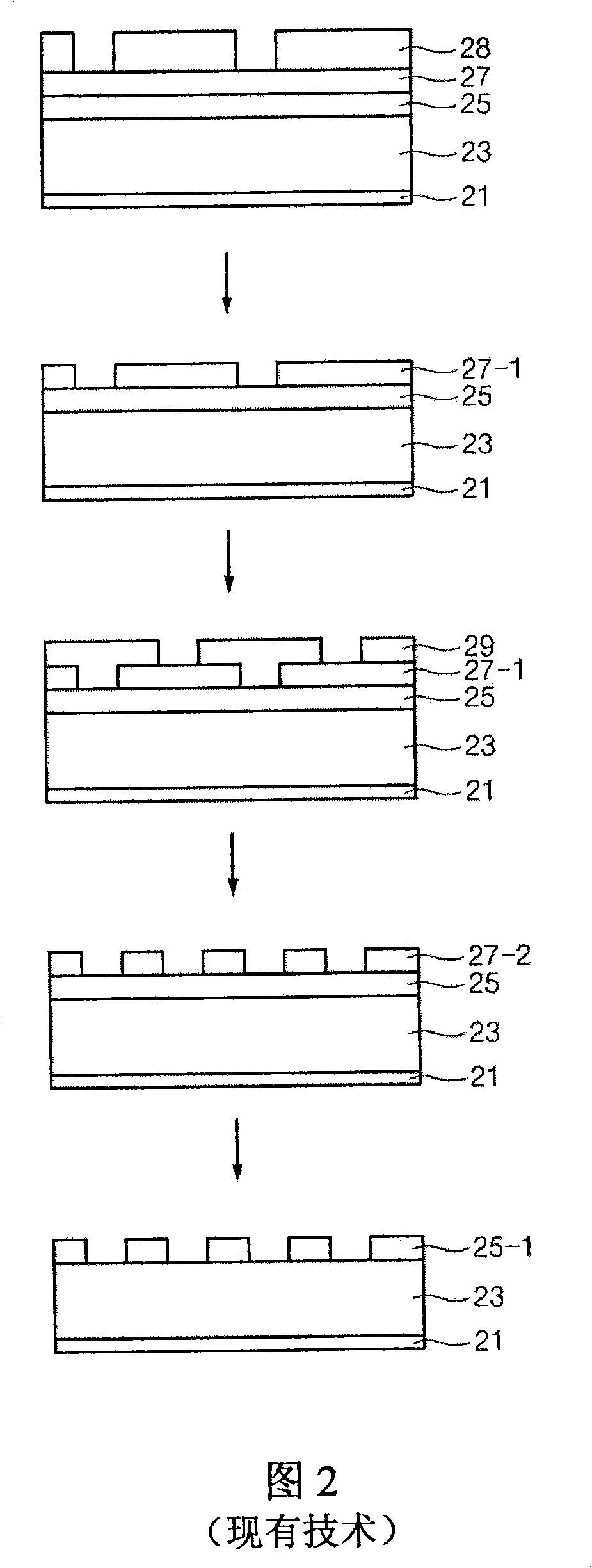

[0027] DEET involves forming first patterns with a line width twice that of the desired pattern, and forming a second pattern with the same line width between the first patterns. More specifically, DEET includes a) a positive approach and b) a negative approach.

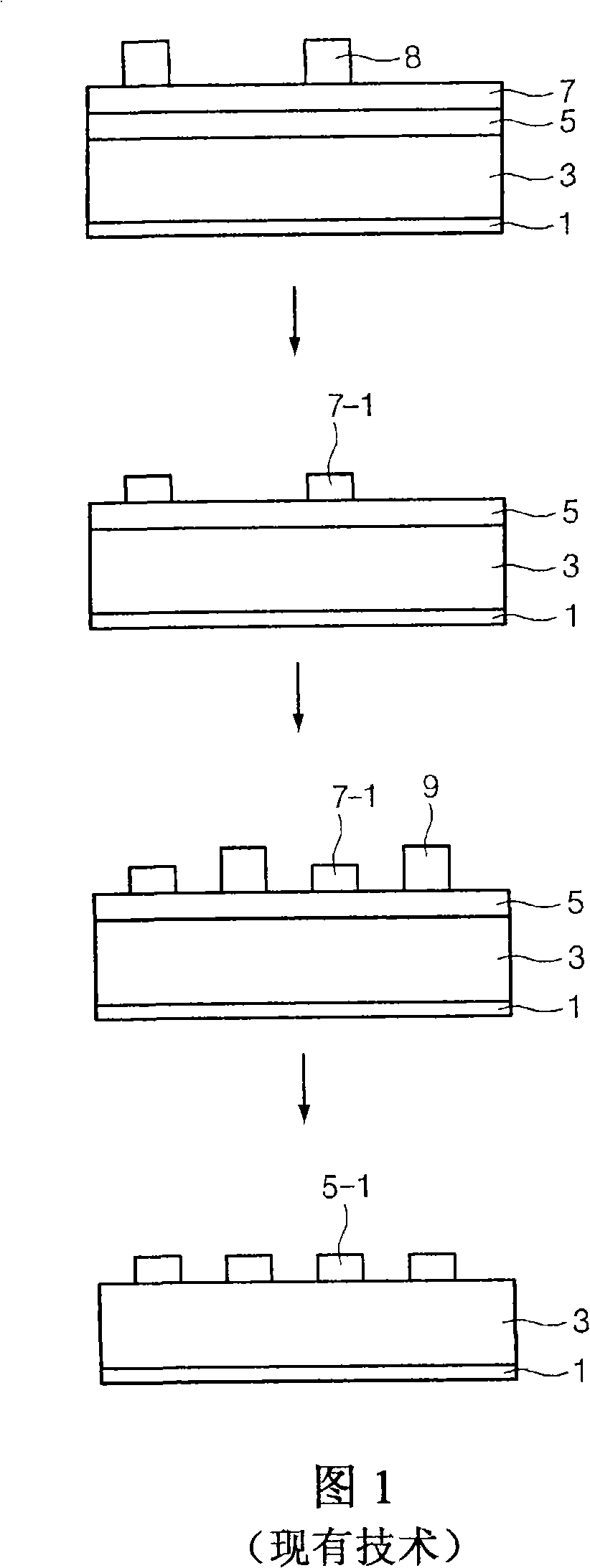

[0028] As shown in FIG. 1 , in the positive type method, an underlayer 3 , a first mask film 5 , a second mask film 7 and a first positive photoresist pattern 8 are formed over a semiconductor substrate 1 . A second mask pattern 7-1 is formed using the first positive photoresist pattern 8 as an etch stop mask. A second positive photoresist pattern 9 is formed bet...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More