Analog determining feedback equalizer used for high-speed serial interface

A technology of decision-feedback equalization and high-speed serial interface, applied in the field of analog decision-feedback equalizers, which can solve the problems of increasing noise in high-frequency areas and unable to completely eliminate ISI, achieving good linearity, saving design costs, and low linearity and absolute error Effect

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment Construction

[0023] Below the present invention will be further described in conjunction with the embodiment in the accompanying drawing:

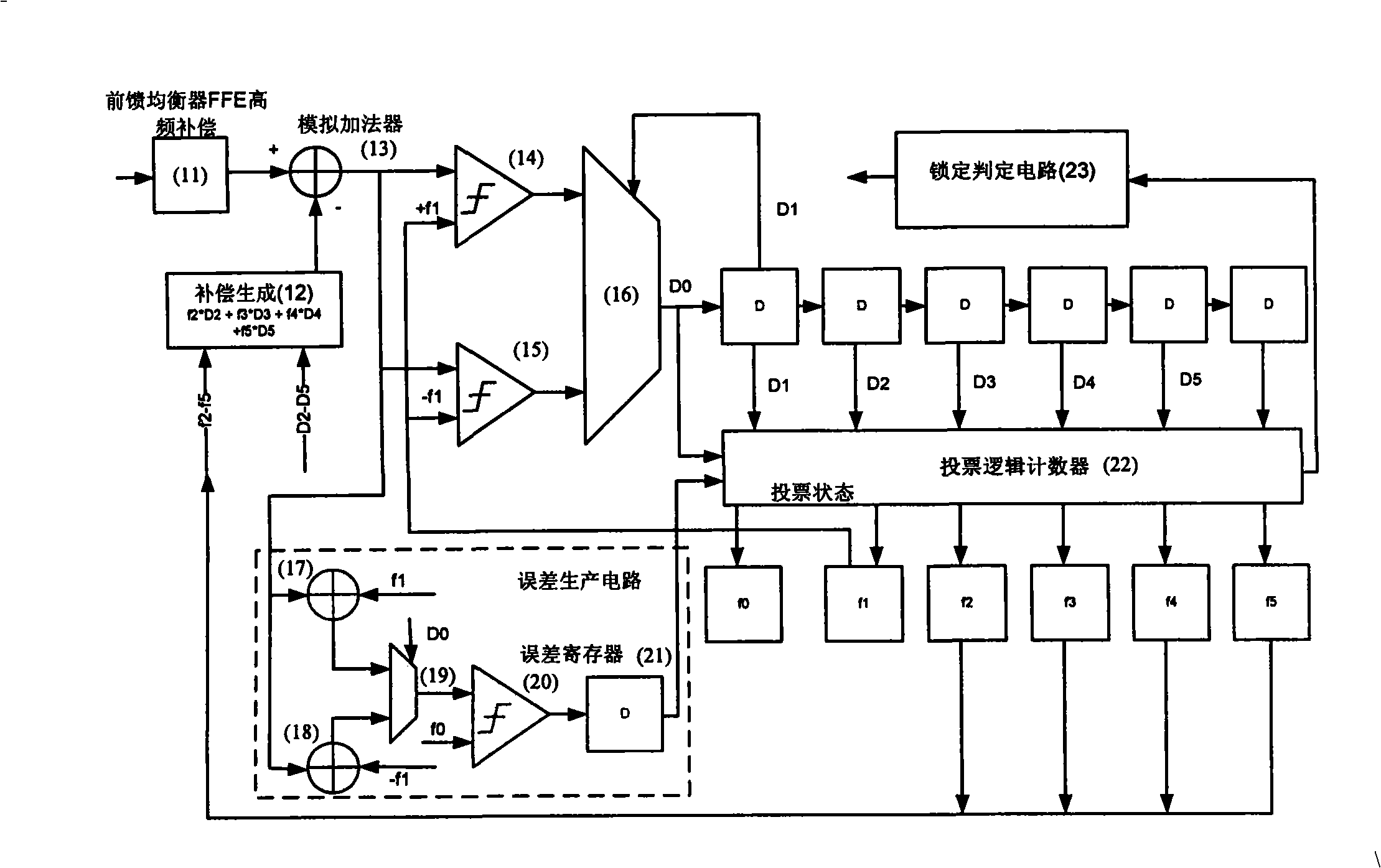

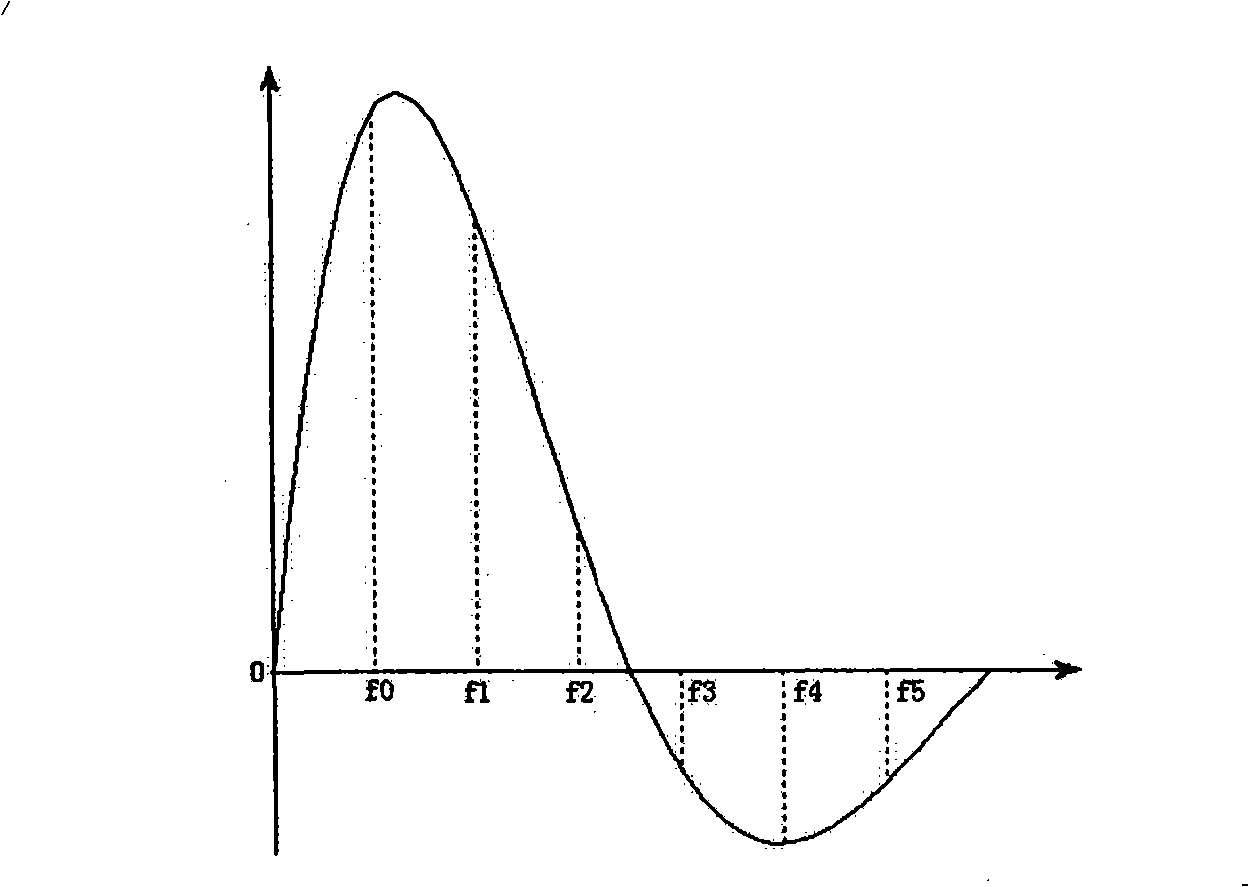

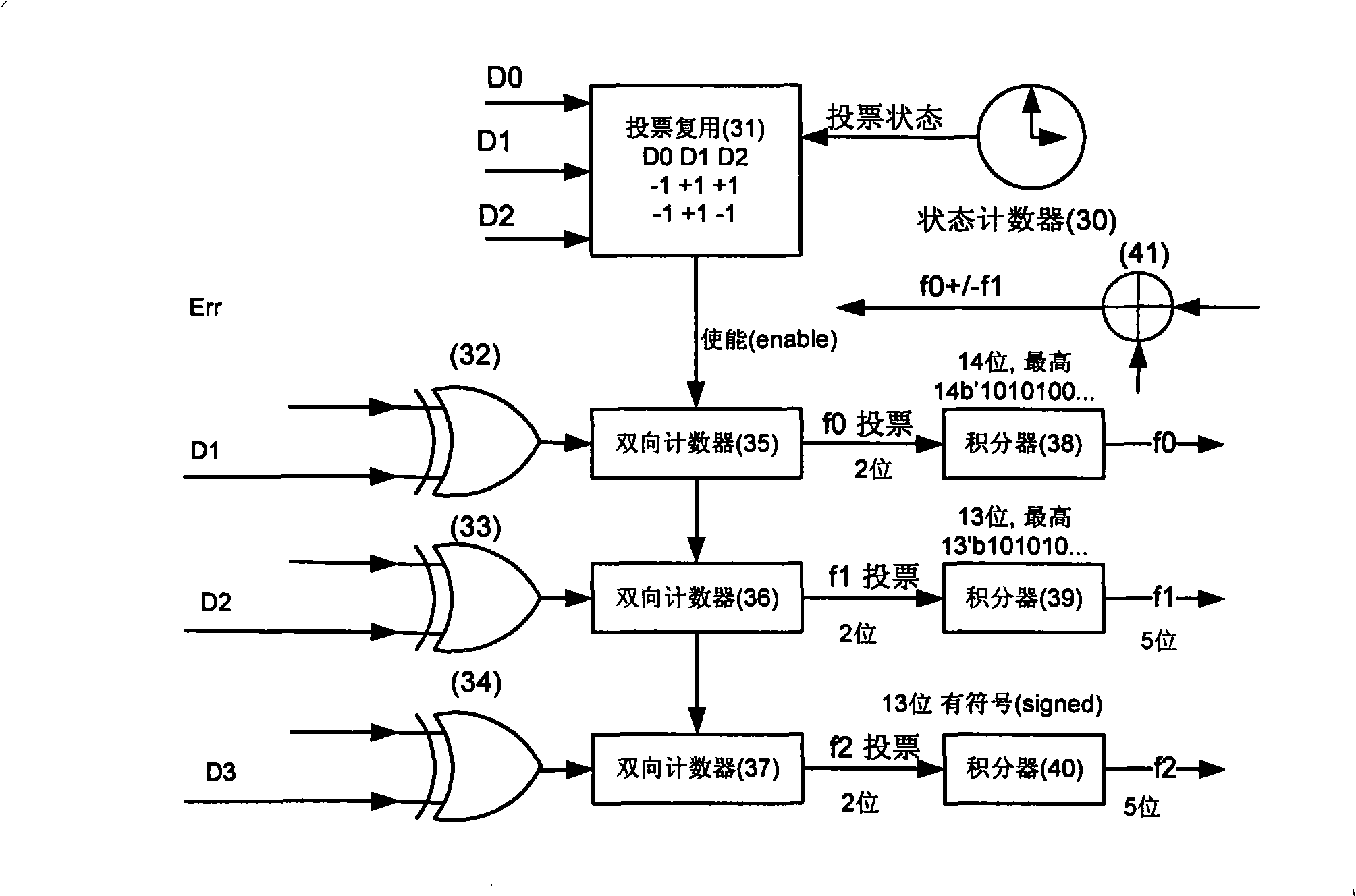

[0024] Figure 1 to Figure 4 As shown, it includes a high-frequency compensation circuit 11, an analog compensation signal generation circuit 12, a first analog adder 13, a first shift comparator 14, a second shift comparator 15, a first output multiplexer 16, a second analog adder device 17, the third analog adder 18, the second output multiplexer 19, the third displacement comparator 20, the error register 21, the voting logic counter 22, the lock determination circuit 23, the state counter 30, the voting multiplexing circuit 31, the first XOR gate 32, second XOR gate 33, third XOR gate 34, first bidirectional counter 35, second bidirectional counter 36, third bidirectional counter 37, first integrator 38, second integrator 39, the first Three integrators 40, an adder 41, a fourth exclusive OR gate 45, a fifth exclusive OR gate 46, an OR gate 47, a ...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More