Method for manufacturing parasitic NPN transistor and structure thereof

A manufacturing method and transistor technology, which is applied in the direction of transistor, semiconductor/solid-state device manufacturing, electrical components, etc., can solve the problems of parasitic transistor application limitations, affecting the performance of other devices, etc., and achieve the effect of improving the amplification gain

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment Construction

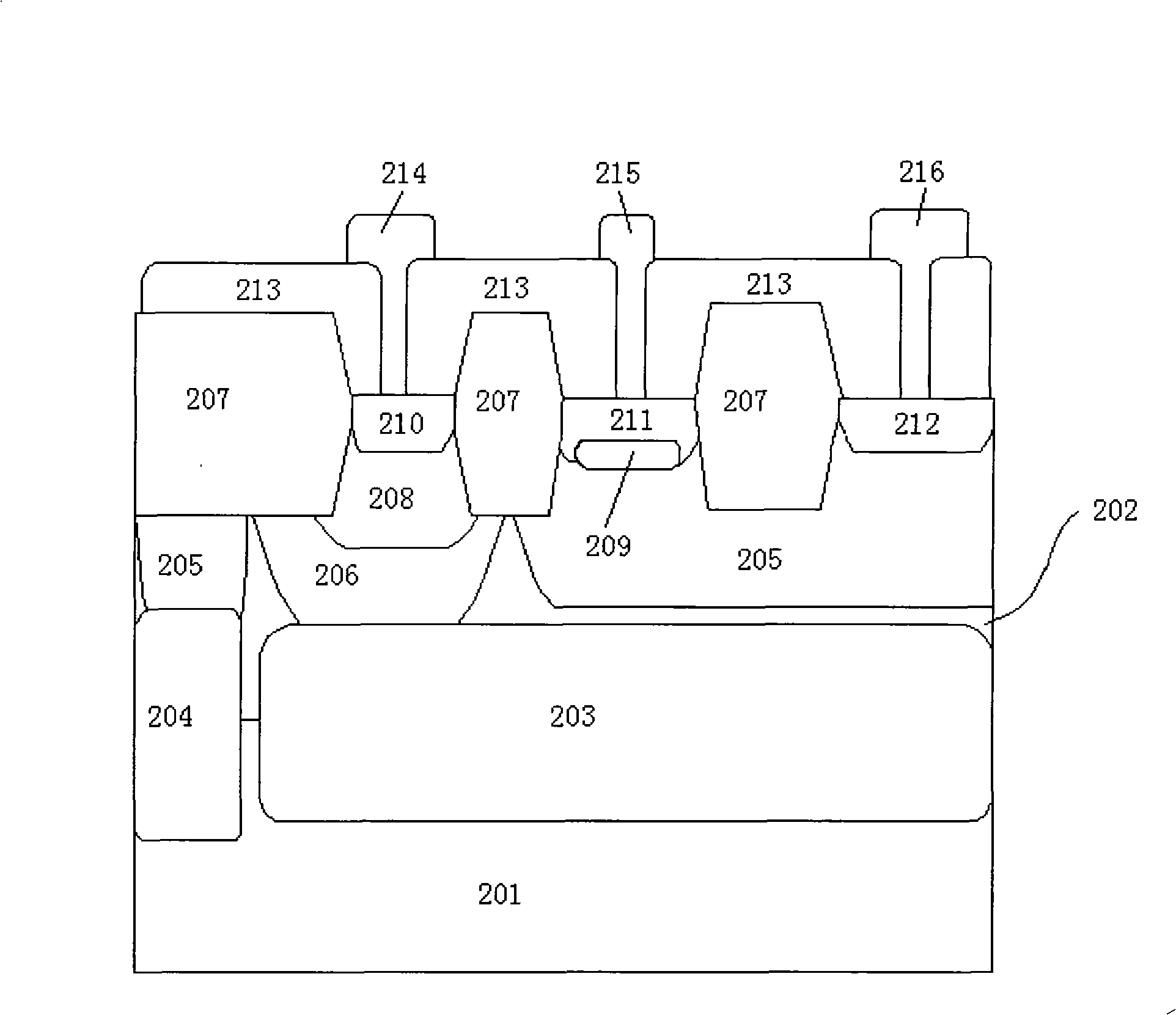

[0018] control figure 2 , in one embodiment, in order to improve the amplification gain of the parasitic NPN transistor, it can be manufactured by the following method:

[0019] In the first step, a P-type single crystal silicon substrate 201 is prepared. Then, using a known photolithography technique, N-type impurities such as As (arsenic) or Sb (antimony) are implanted and diffused from the surface of the substrate 201 to form an N-type buried diffusion layer 203 . Next, P-type impurities, such as boron (B) plasma, are implanted and diffused from the surface of the substrate 201 using known photolithography techniques to form a P-type buried diffusion layer 204 .

[0020] In the second step, since the N-type buried diffusion layer 203 is advanced, a layer with a thickness of about 2300~ Therefore, in this step, it is necessary to use a wet method (such as chemical reagent hydrofluoric acid, etc.) to remove the buried oxide layer, and then place the substrate 201 on the s...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More