Gate layer manufacturing method, semiconductor device manufacturing method and semiconductor construction

A manufacturing method and semiconductor technology, applied in semiconductor/solid-state device manufacturing, semiconductor devices, electrical components, etc., can solve problems such as increased leakage current, threshold voltage drift of metal oxide semiconductor devices, large energy and energy, etc., to achieve improved Yield rate, avoiding multiple handling or transmission, and improving stability

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment Construction

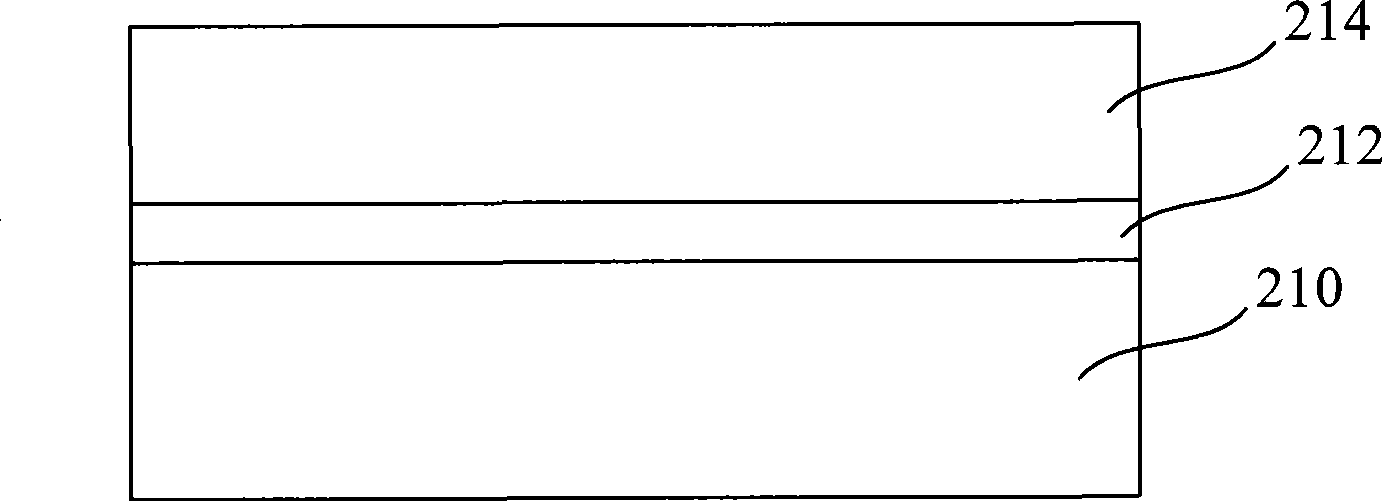

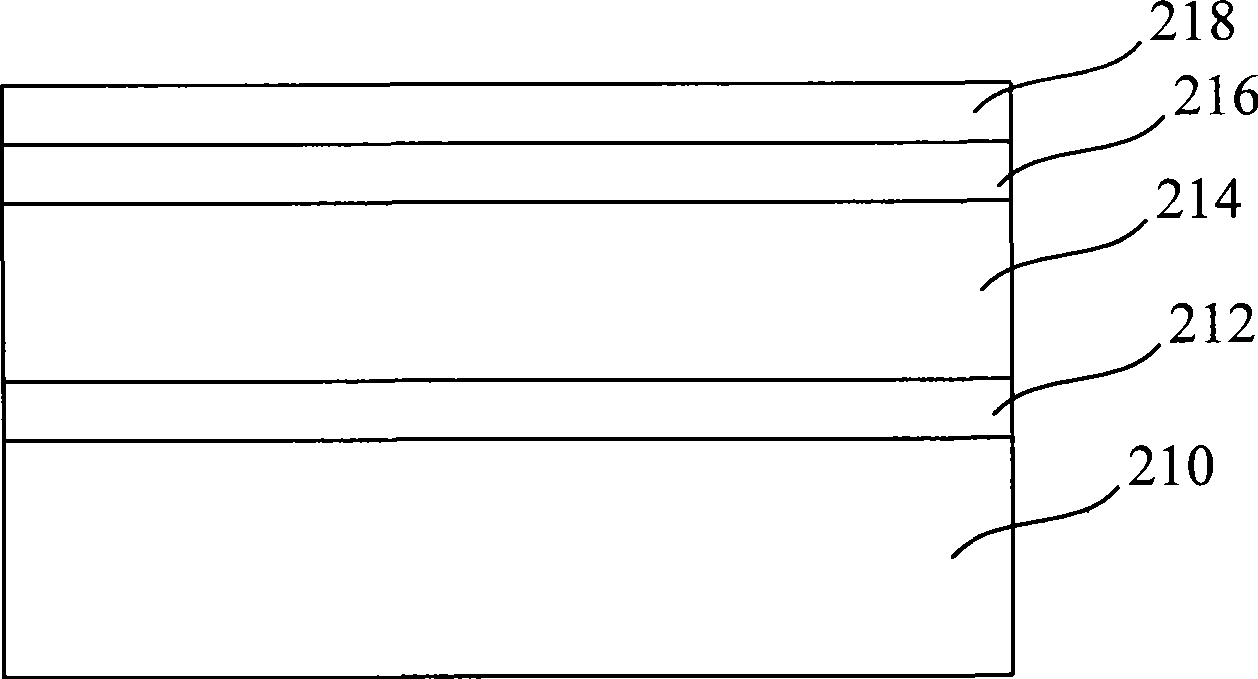

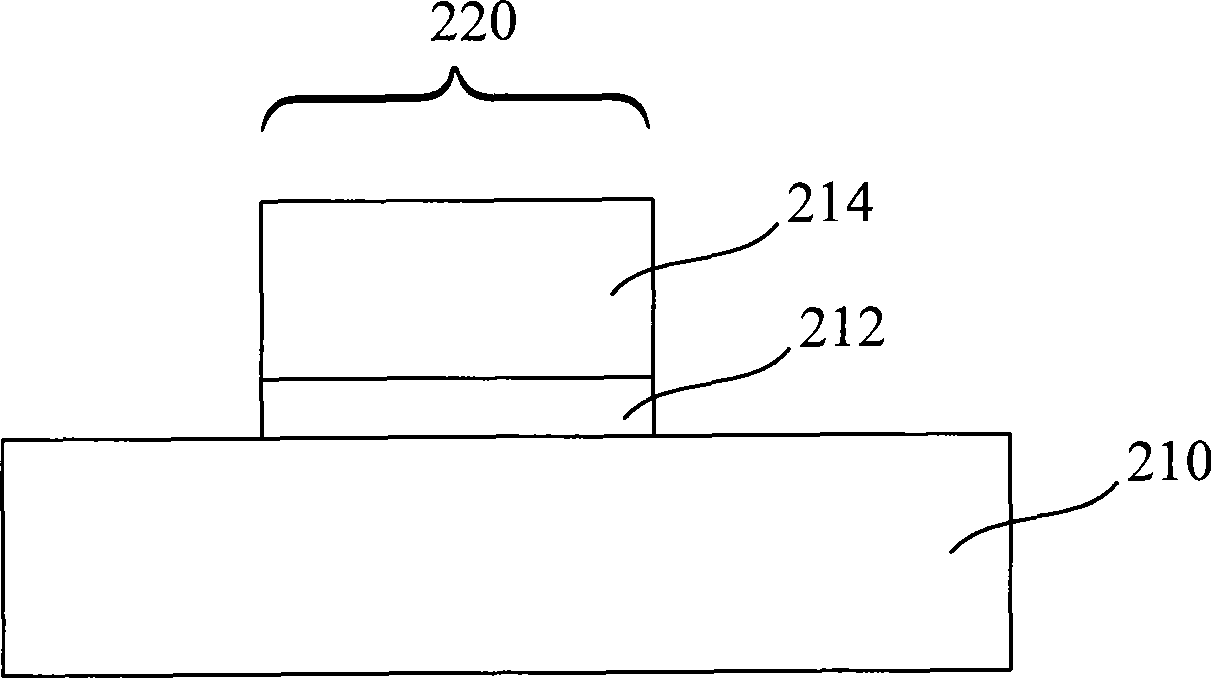

[0053] The specific embodiments of the present invention will be described in detail below in conjunction with the accompanying drawings.

[0054] With the continuous development of the semiconductor manufacturing process, the size of the gate is getting smaller and smaller. In order to ensure the fast response and low power consumption of the formed semiconductor device, it is necessary to reduce the resistance of the gate. One of the methods is to form a polysilicon gate. During ion implantation, polysilicon is doped by ion implantation; however, during ion implantation, due to the high energy of the implanted ions, the implanted ions will pass through the gate insulating layer and enter the conductive channel.

[0055] The invention provides a method for manufacturing a gate layer. When forming a polysilicon gate layer for manufacturing a gate, at least one polysilicon layer in which crystal grains are randomly arranged (or distributed) is formed in the gate layer, and the p...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More