Semiconductor device and method for fabricating the same

A technology for semiconductors and high-voltage regions, which is applied in the field of semiconductor devices and their manufacturing, and can solve problems such as lowering device reliability, lowering doping concentration, and subthreshold leakage

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

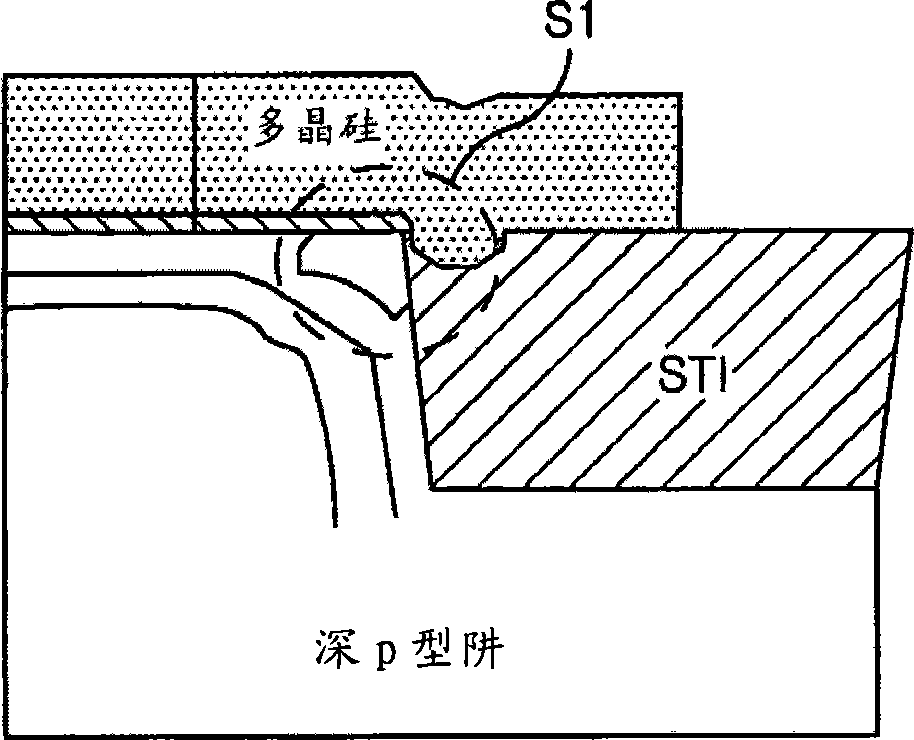

Problems solved by technology

Method used

Image

Examples

Embodiment Construction

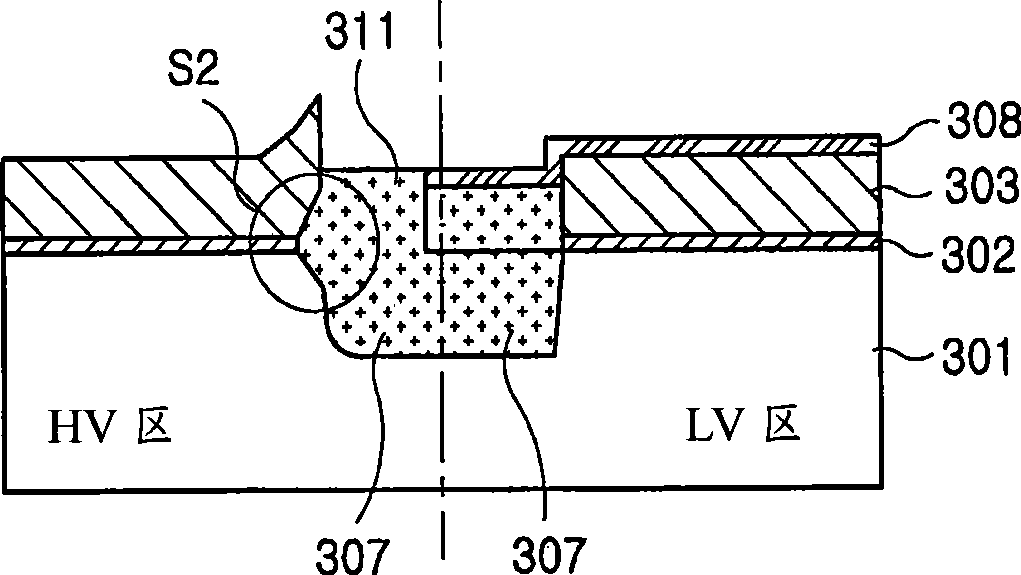

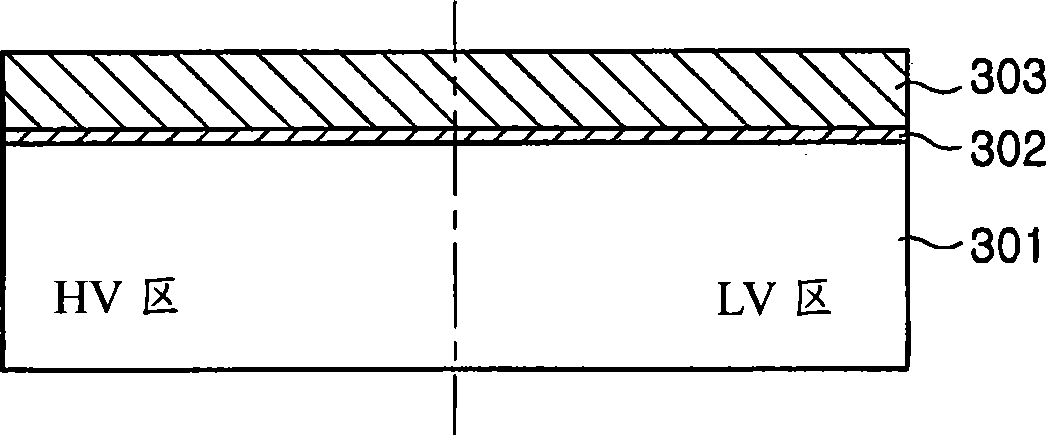

[0011] example figure 2 A structure of a semiconductor device in which an STI is formed according to an embodiment of the present invention is shown. reference example figure 2 , a pad oxide film 302 may be sequentially formed over a semiconductor substrate (P-type substrate (P-Substrate)) which may include a high voltage (hereinafter, referred to as HV) region and a low voltage (hereinafter, referred to as LV) region and nitride film 303. The pad oxide film 302 and the nitride film 303 can be selectively removed using the PR pattern 304 . The STI 305 can be formed using the removed pad oxide film 302 and nitride film 303 as an etching mask.

[0012] An oxide film 306 may be formed thereon and planarized by a planarization process. A capping layer (for example, a nitride film) 308 may be formed over the entire surface of the planarized top portion. The PR pattern 309 may be formed to open only the HV region, and then the nitride film of the HV region may be removed by a...

PUM

| Property | Measurement | Unit |

|---|---|---|

| Thickness | aaaaa | aaaaa |

Abstract

Description

Claims

Application Information

Login to View More

Login to View More