Radio frequency identification label chip data receiving synchronous method

A radio frequency identification tag and data technology, applied in instruments, inductive record carriers, computer parts, etc., can solve problems such as data sampling errors, complex timing problems, inability to generate clock edges, etc., and achieve simple structure and strong adaptability. Effect

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment Construction

[0041] The radio frequency identification tag chip data reception synchronization method of the present invention will be described in detail below in conjunction with specific embodiments and accompanying drawings.

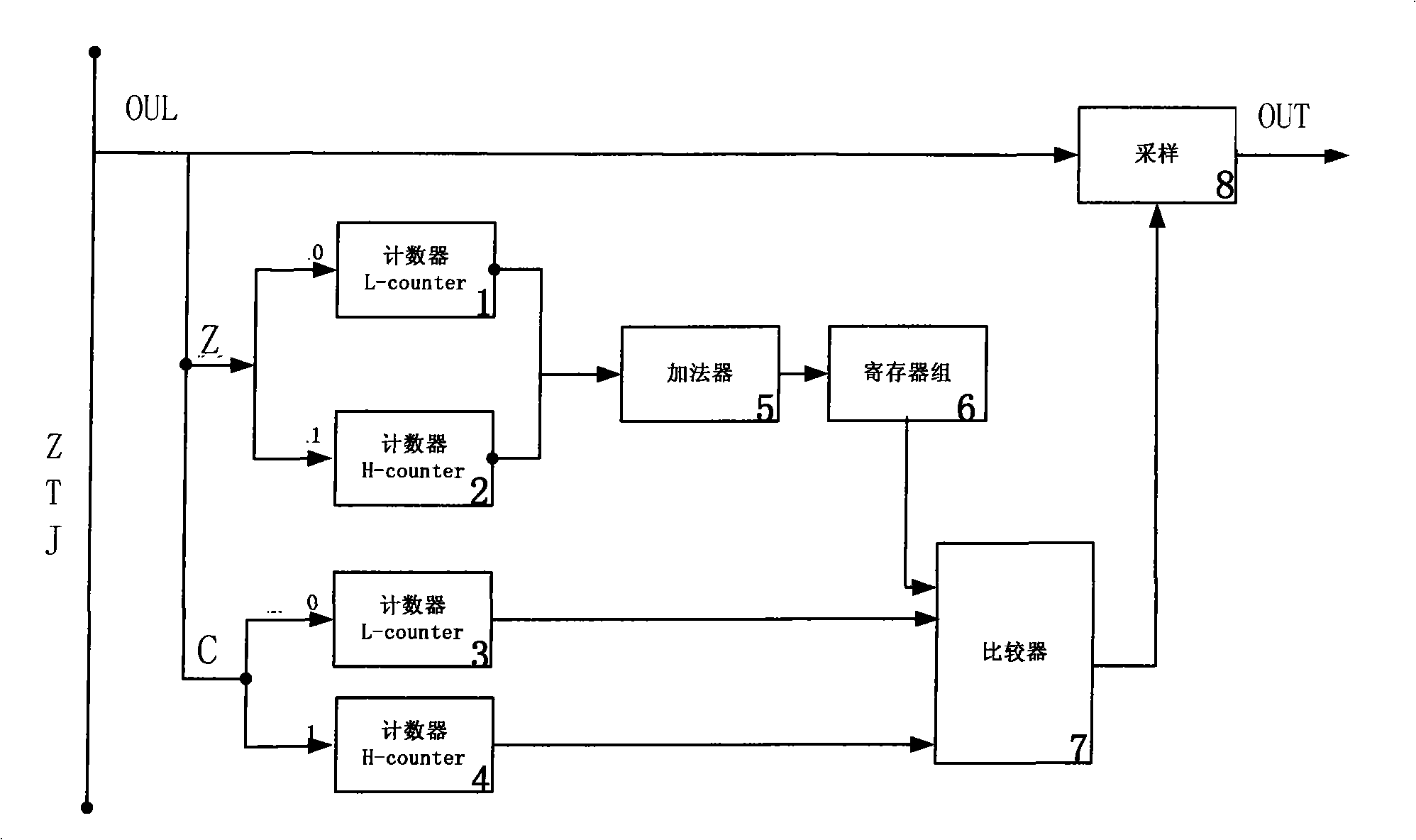

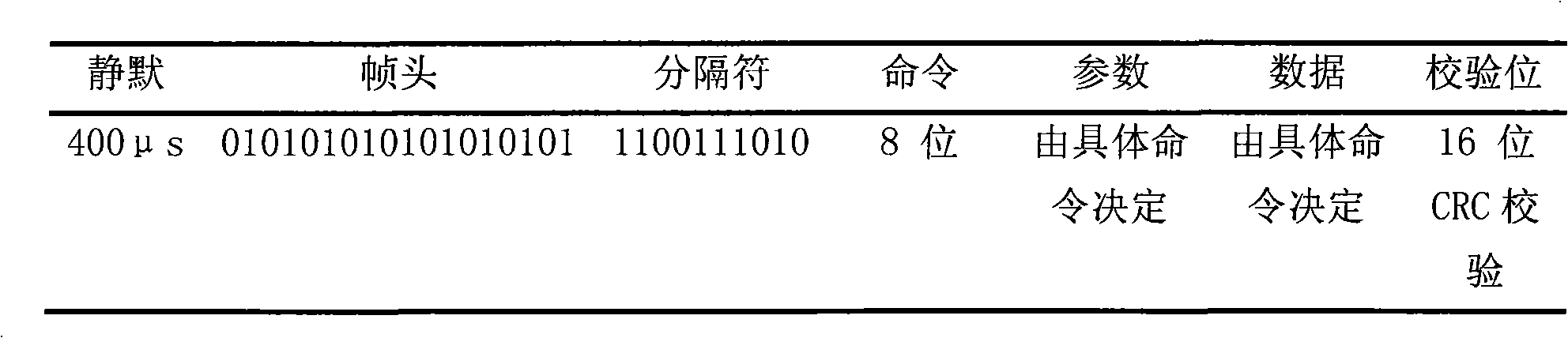

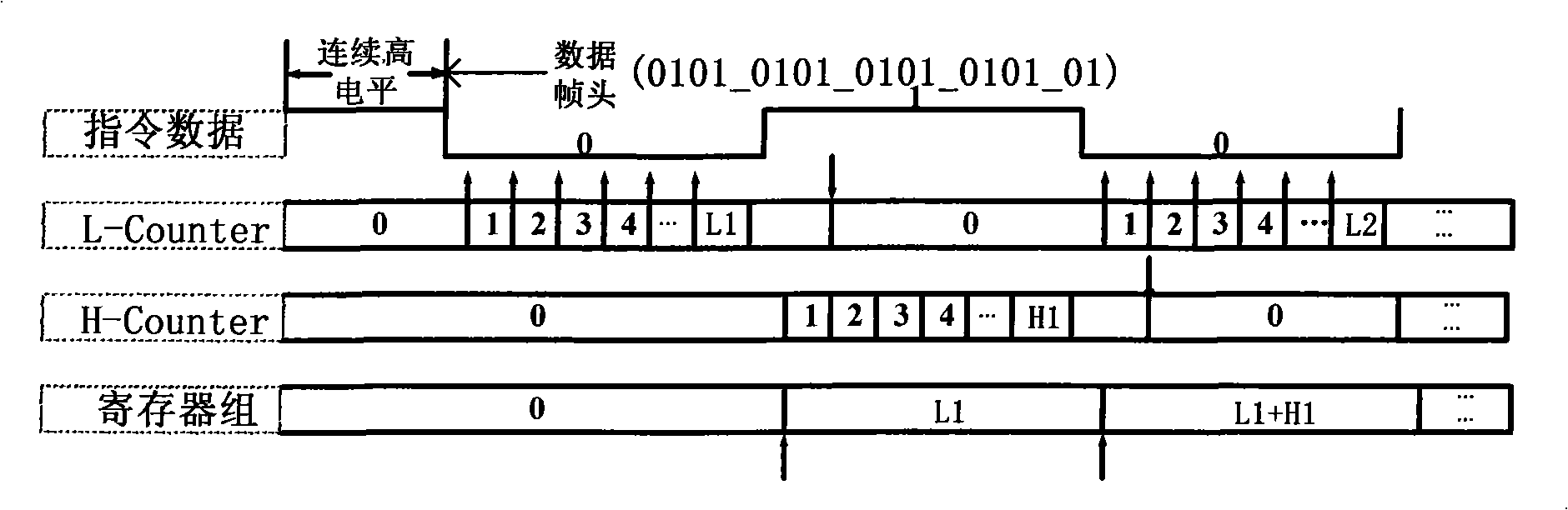

[0042] The radio frequency identification tag chip data reception synchronization method of the present invention is to adopt two counters (H-counter and L-counter) respectively to comply with the high level 1 and the low level in the instruction format of the ISO / IEC 18000-6 Type B agreement. The length of flat 0 is counted, and an adder matching the number of counter digits is used for cumulative operation, and the synchronous count value is temporarily stored in the register group. When sampling, the comparator is used to compare the count value with the accumulated and divided operation. The base reference value is compared to give the correct sampling clock edge.

[0043] Specific as figure 1 As shown, the first counter 1 is used to receive the low-level da...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More