Printed circuit boards with stacked micros vias

A printed circuit board, circuit board technology, applied in the direction of printed circuit, printed circuit, printed circuit manufacturing, etc., can solve the problems of expensive, difficult to achieve rapid change, time-consuming processing sequence, etc.

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment Construction

[0046] In the following detailed description, there are shown and described, by way of illustration, certain exemplary embodiments of the invention. As those skilled in the art would realize, the described exemplary embodiment may be modified in various different ways, all without departing from the spirit and scope of the present invention. Accordingly, the drawings and descriptions are to be regarded as illustrative in nature and not restrictive. Parts shown in the drawings, or parts not shown in the drawings, which are not discussed in the specification, are not considered indispensable to a complete understanding of the invention. The same reference numerals denote the same elements.

[0047] first exemplary embodiment

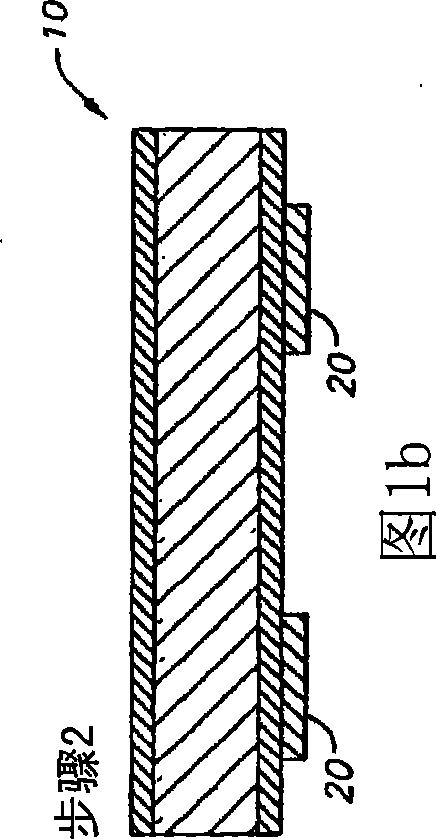

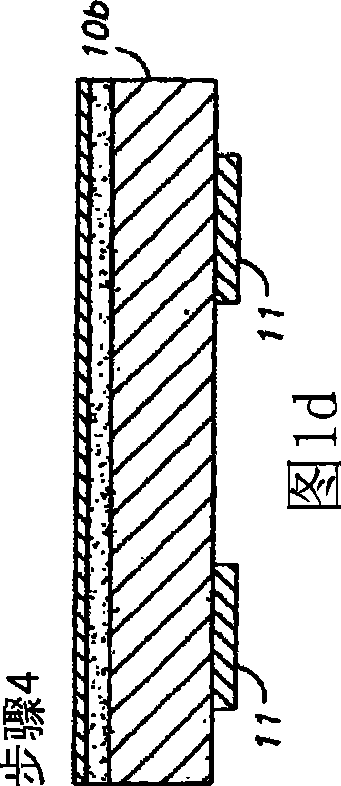

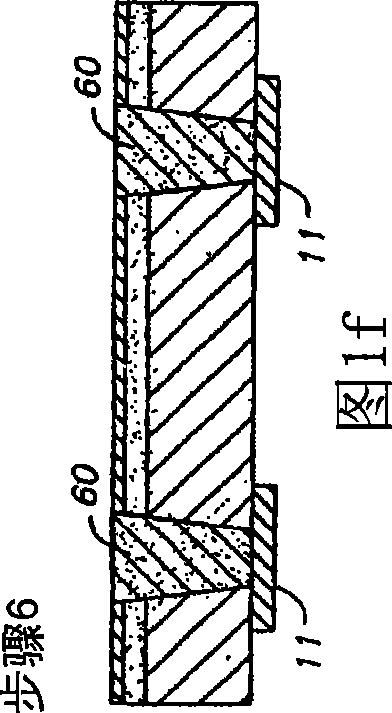

[0048] A method of manufacturing a printed circuit board according to a first exemplary embodiment of the present invention, utilizing a single lamination cycle or a processing sequence with stacked (or staggered) microvias, will be described with refere...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More