Integrated circuit and method for implementing high speed two-dimension discrete cosine transform

A discrete cosine transform and two-dimensional discrete cosine technology, applied in television, electrical components, image communication, etc., can solve problems such as high-speed image data compression processing

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment 1

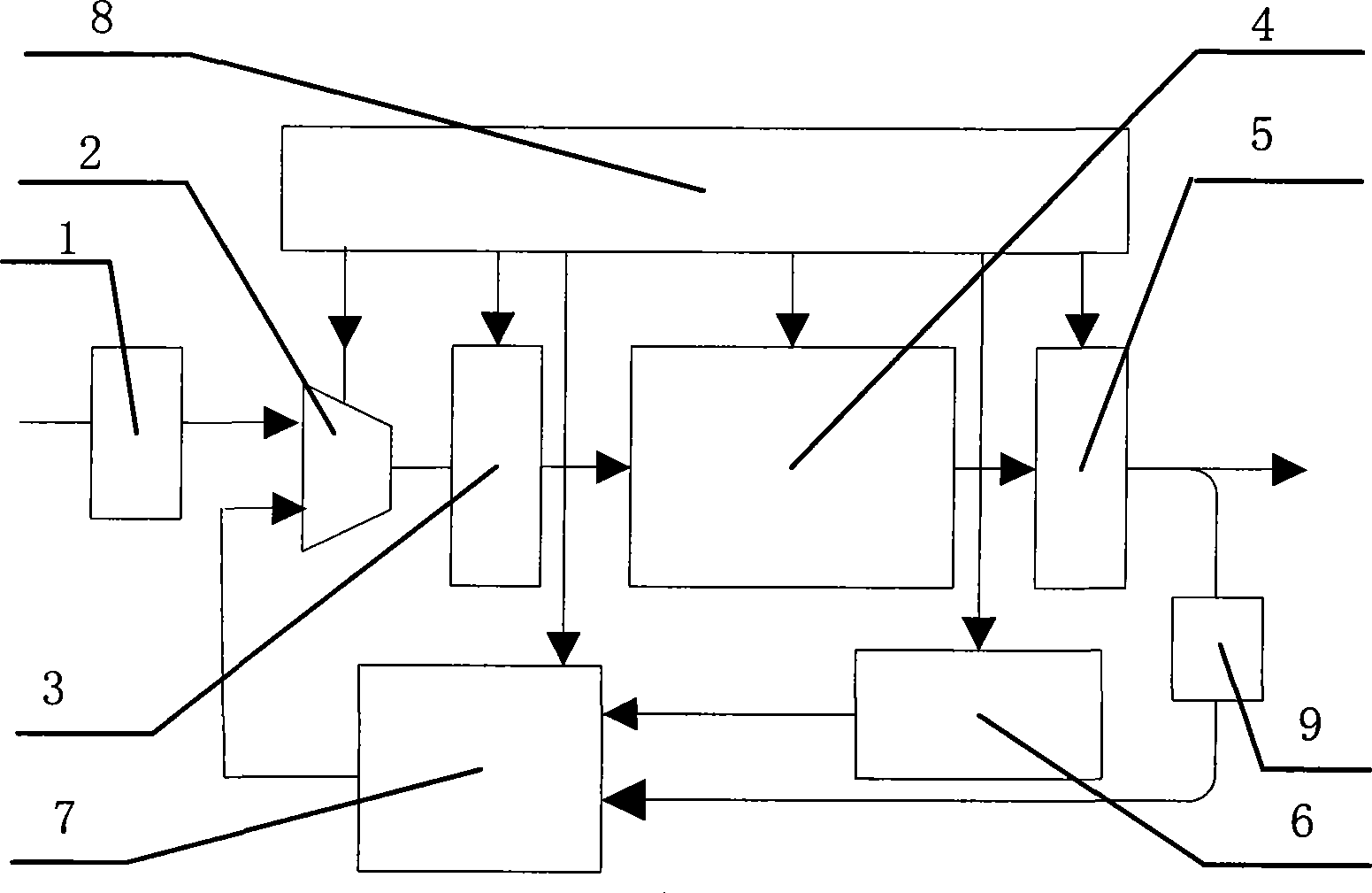

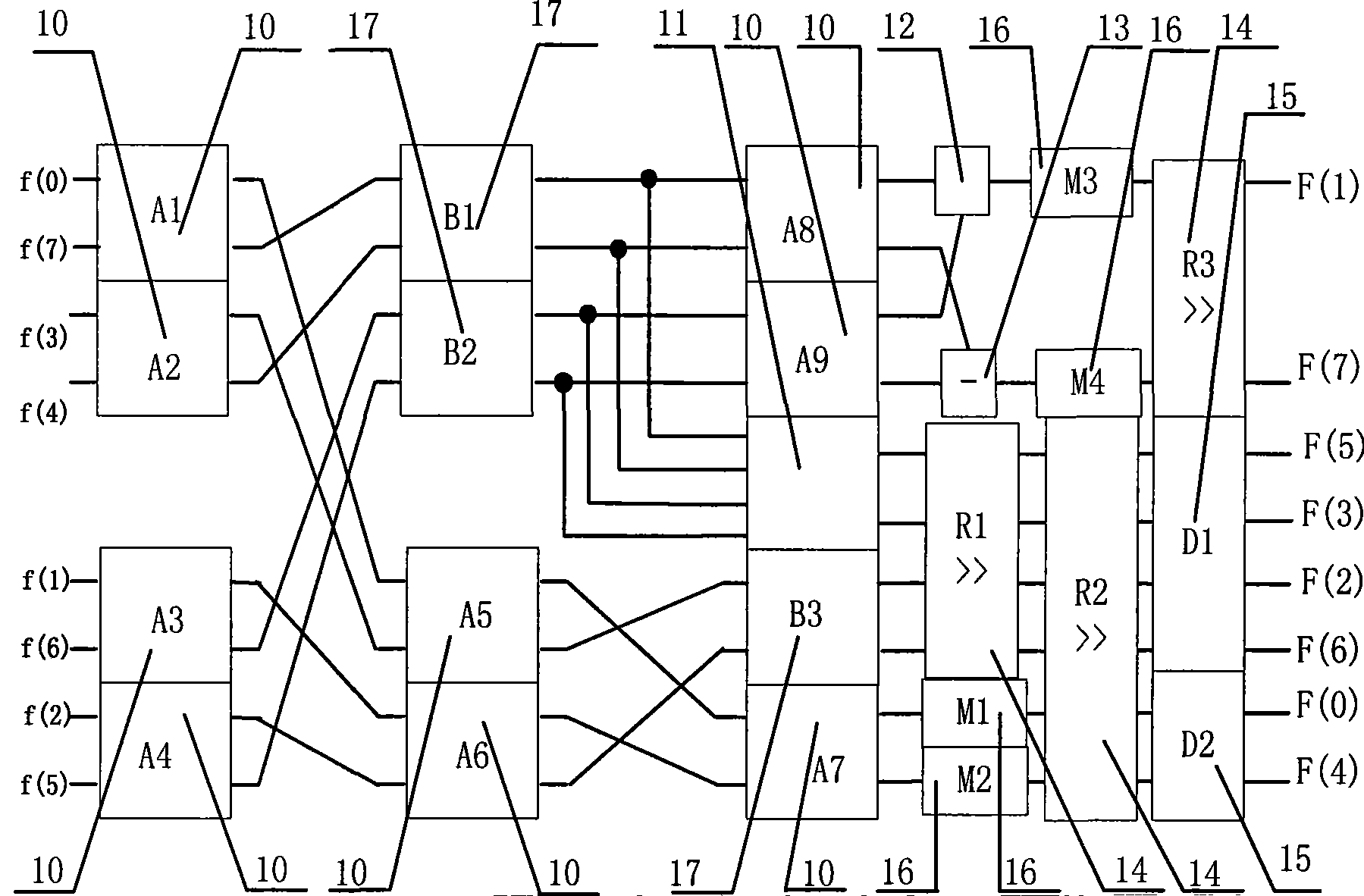

[0079] Embodiment 1: (hardware embodiment)

[0080] The integrated circuit embodiment of the present invention is for example Figure 1-2 As shown, it includes a transformation coding control module 8, a bit expansion module 1, a data selection module 2, a serial-to-parallel conversion module 3, a one-dimensional discrete cosine transform module 4, a parallel-to-serial module 5, a transposed storage matrix RAM module 7, and a bit interception Module 9 and transposition address generation module 6 are characterized in that bit expansion module 1 is connected with data selection module 2; data selection module 2 is connected with serial parallel conversion module 3; serial parallel conversion module 3 and one-dimensional discrete cosine transform module 4 are connected; the one-dimensional discrete cosine transform module 4 is connected with the parallel-to-serial module 5; the parallel-to-serial module 5 is connected with the transposed storage matrix RAM module 7 through the b...

Embodiment 2

[0087] Embodiment 2: (method embodiment)

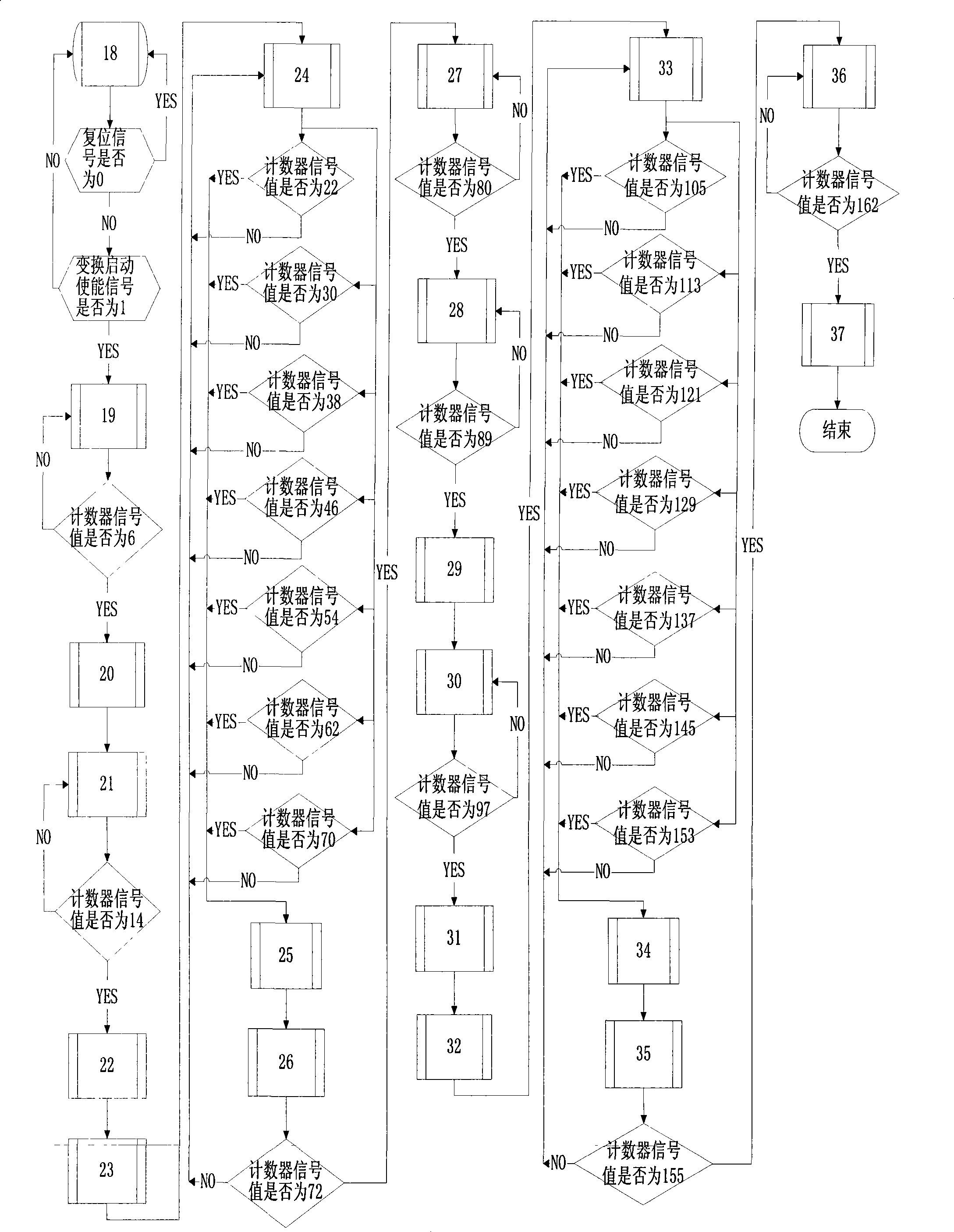

[0088] A working method of the transformation coding control module 8 in the above-mentioned circuit, as image 3 As shown, the steps are as follows:

[0089] 18: In the initial state, the device is idle, and the data conversion end signal is high level; other control output signals are low level;

[0090] 19: Input the conversion start enable signal to be high level, the modulo 163 counter included in the conversion coding control module 8 starts counting, all the module output signals are low level, and when the counter increases to 6, jump to the next step;

[0091] 20: The output serial-to-parallel conversion enable signal is high level, and other control output signals are low level; jump to the next step in the next clock cycle;

[0092] 21: Output the one-dimensional discrete cosine transform module to transform the enable signal to a high level, and other control signals to a low level, and the counter increases to 14 to jum...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More