Dynamic multi-clock low power consumption AHB bus design method for SOC

A technology of dynamic power consumption and design method, applied in energy-saving computing, energy-saving ICT, instruments, etc., to achieve the effect of reducing circuit power consumption

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment

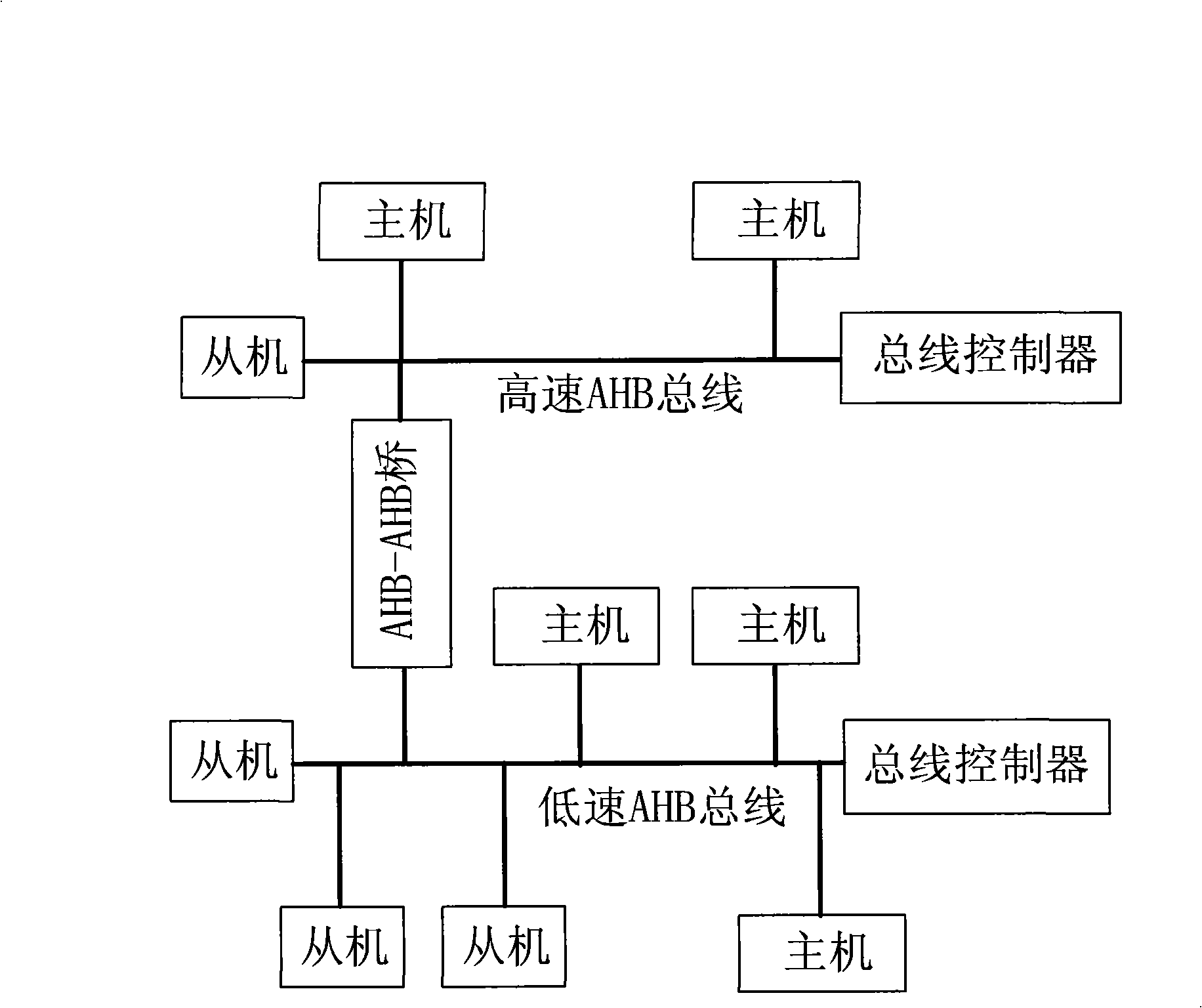

[0016] It mainly has the following two working states:

[0017] 1. When the master on the high-speed AHB bus accesses the slaves on the high-speed AHB bus, the AHB-AHB bridge does not work. At this time, the master on the low-speed AHB bus can also access the slaves on the low-speed AHB bus at the same time. The high-speed AHB bus and the low-speed AHB bus work at the same time to improve the working efficiency of the system

[0018] 2. When the master on the high-speed AHB bus accesses the slave on the low-speed AHB bus, we need to transmit data through the AHB-AHB bridge. First, the master of the high-speed AHB bus accesses the AHB-AHB bridge as a slave, and stores the transmitted data in the register of the AHB-AHB bridge; then the AHB-AHB bridge acts as a master of the low-speed AHB bus on its bus. slaves to access. Because the processing speed of the devices on the low-speed AHB bus is slow, when the AHB-AHB bridge operates as the host of the low-speed bus, it sends a s...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More