Method for producing single-layer polysilicon gate non-volatile memory

A single-layer polysilicon, non-volatile technology, applied in the manufacture of electric solid-state devices, semiconductor devices, semiconductor/solid-state devices, etc., can solve the problems of poor charge storage performance and high mobile ion concentration of single-layer polysilicon gate memory, and achieve improvement Charge storage performance, moderate temperature effect

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment 1

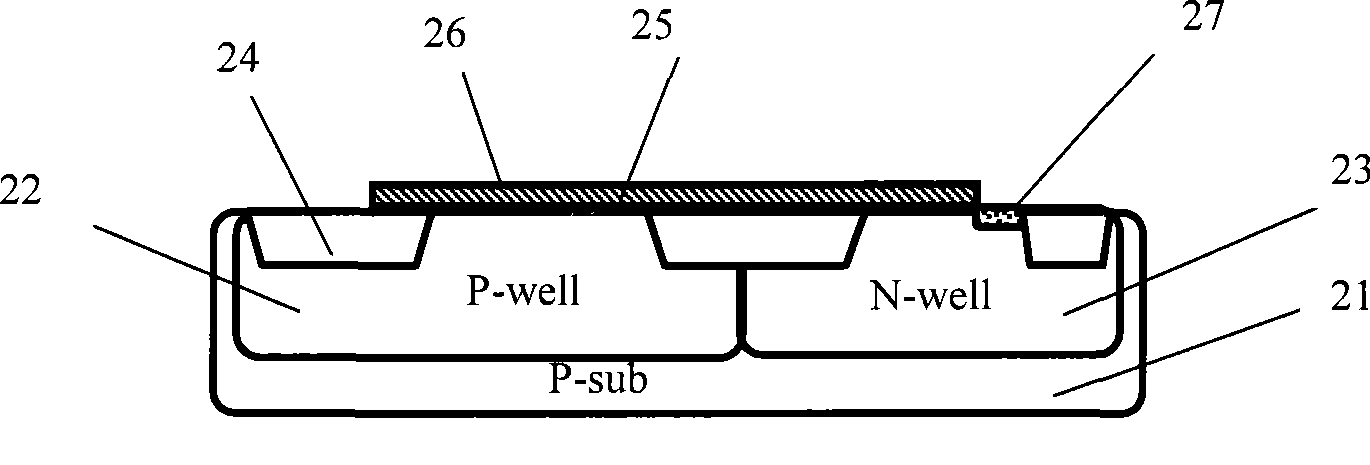

[0019] Using the same prior art (including prior art methods and materials used in the prior art) to complete the partial structure of the single-layer polysilicon gate memory cell, including the following steps:

[0020] 1 Form an isolation region on a P-type silicon substrate;

[0021] 2 Photolithography to form the N-well pattern as the control gate, and perform N-well ion implantation;

[0022] 3 Form gate oxide layer and undoped polysilicon gate in sequence;

[0023] 4 Perform lightly doped drain (LDD) implantation;

[0024] 5 forming a protective layer on the gate side;

[0025] 6 Form contact holes.

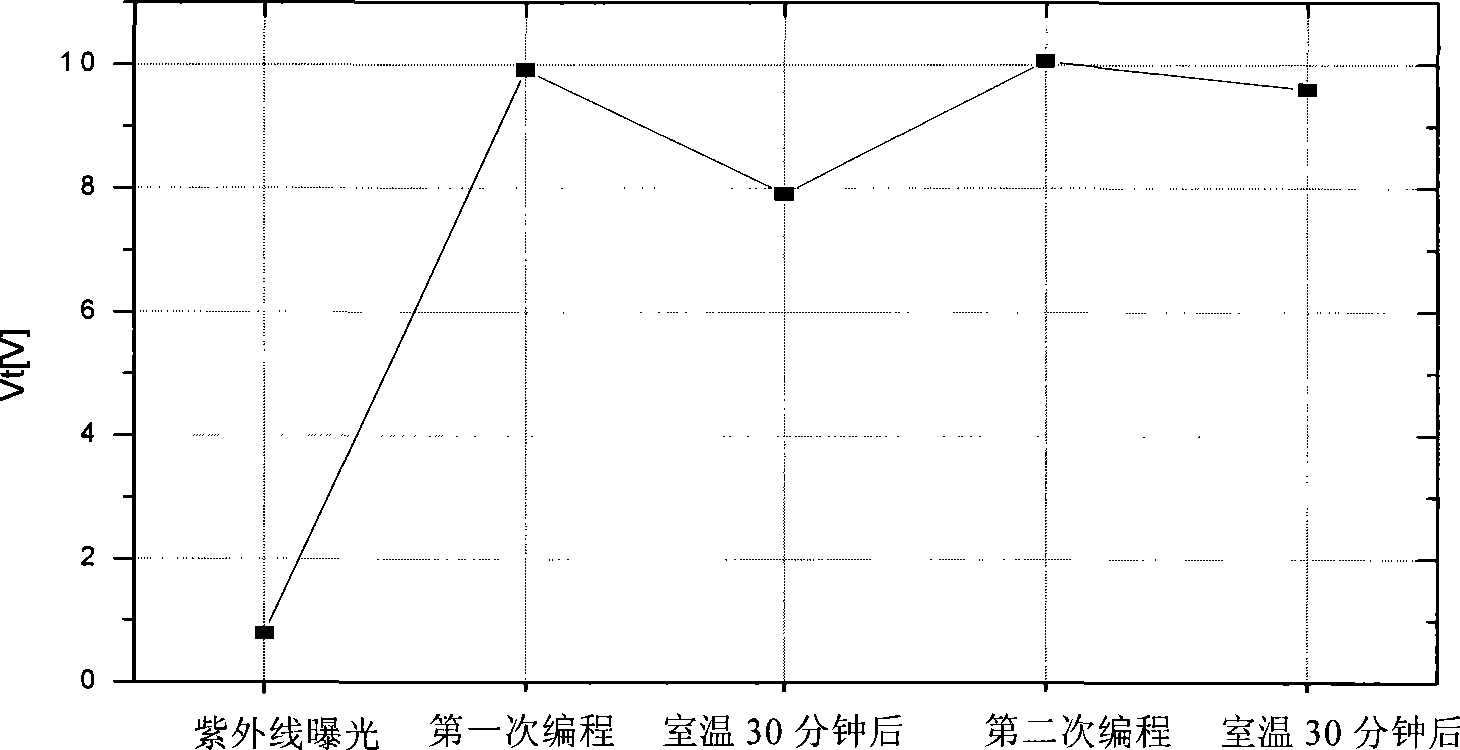

[0026] Afterwards, use the method of low pressure vapor phase chemical deposition (the method of low pressure chemical vapor deposition here is the same as the growth method of LPTEOS film layer in the prior art) TEOS, grow The thickness of the LPTEOS film layer is used as the SAB layer, replacing the existing technology Thickness of the SRO film layer, as the SAB l...

Embodiment 2

[0033] In this embodiment, after the step 6 in the embodiment 1, the following method is used to manufacture the SAB layer:

[0034] At first, use the method of low pressure vapor phase chemical deposition (the method of low pressure chemical vapor deposition here is the same as the growth method of LPTEOS film layer in the prior art), grow The first low pressure chemical vapor deposition orthosilicate film layer (also can be called the first LPTEOS film layer) of thickness; The method of growing the silicon nitride film layer by the low pressure chemical vapor deposition method is the same) Thick silicon nitride film layer; Finally, use the method of low pressure vapor phase chemical deposition (the method of low pressure chemical vapor phase deposition here is the same as the growth method of LPTEOS film layer in the prior art), grow The thickness of the second low-pressure chemical vapor deposition tetraethyl silicate film layer (also called the second LPTEOS film layer...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More