Chip package substrate, chip package body, and method for manufacturing chip package body

A technology of chip packaging and manufacturing methods, applied in semiconductor/solid-state device manufacturing, electric solid-state devices, semiconductor devices, etc., can solve problems such as breakage, failure to upgrade, and high cost, so as to reduce costs, increase yields, and be less prone to damage Effect

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment Construction

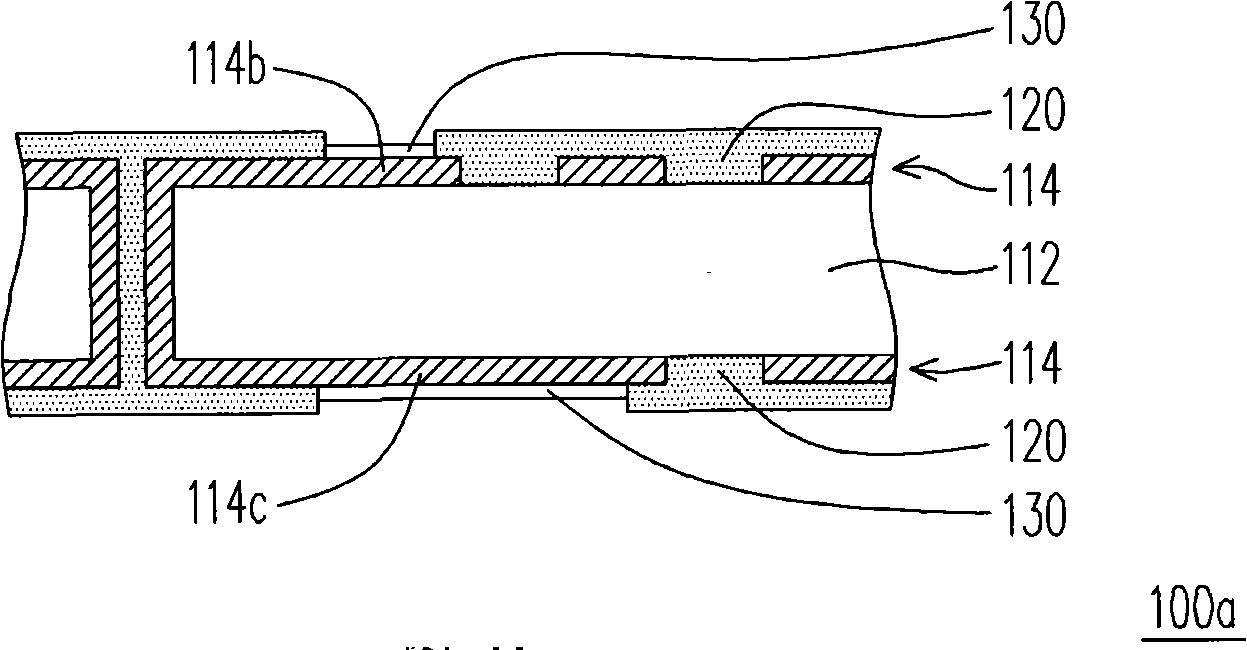

[0078] Figure 2A It is a schematic cross-sectional view of a chip package according to an embodiment of the present invention. See Figure 2A , The chip package 200a includes a circuit substrate 300a, a chip 210, and a packaging glue 220, wherein Figure 2A The circuit substrate 300a shown has a two-layer circuit structure.

[0079] In detail, the circuit substrate 300a includes a conductive pattern layer 310, a first circuit layer 320a, a first dielectric layer 330, and a plurality of first conductive blind hole structures 340a. The conductive pattern layer 310 includes a plurality of first pads 312, and each of the first pads 312 has a bottom surface B. In this embodiment, the conductive pattern layer 310 may only include these first pads 312. In other words, the conductive pattern layers 310 are composed of the first pads 312.

[0080] The first circuit layer 320a is disposed above the conductive pattern layer 310, and the first dielectric layer 330 is disposed between the co...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More