Method and device for designing standard cell library and integrated circuit

A technology of standard cell library and design method, applied in computing, electrical digital data processing, special data processing applications, etc., can solve the problems of waste of dynamic power consumption and insufficient use of clocks, etc., and achieve reduction of dynamic power consumption, The effect of reducing the amount of clock activity and reducing the number of clock transitions

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment Construction

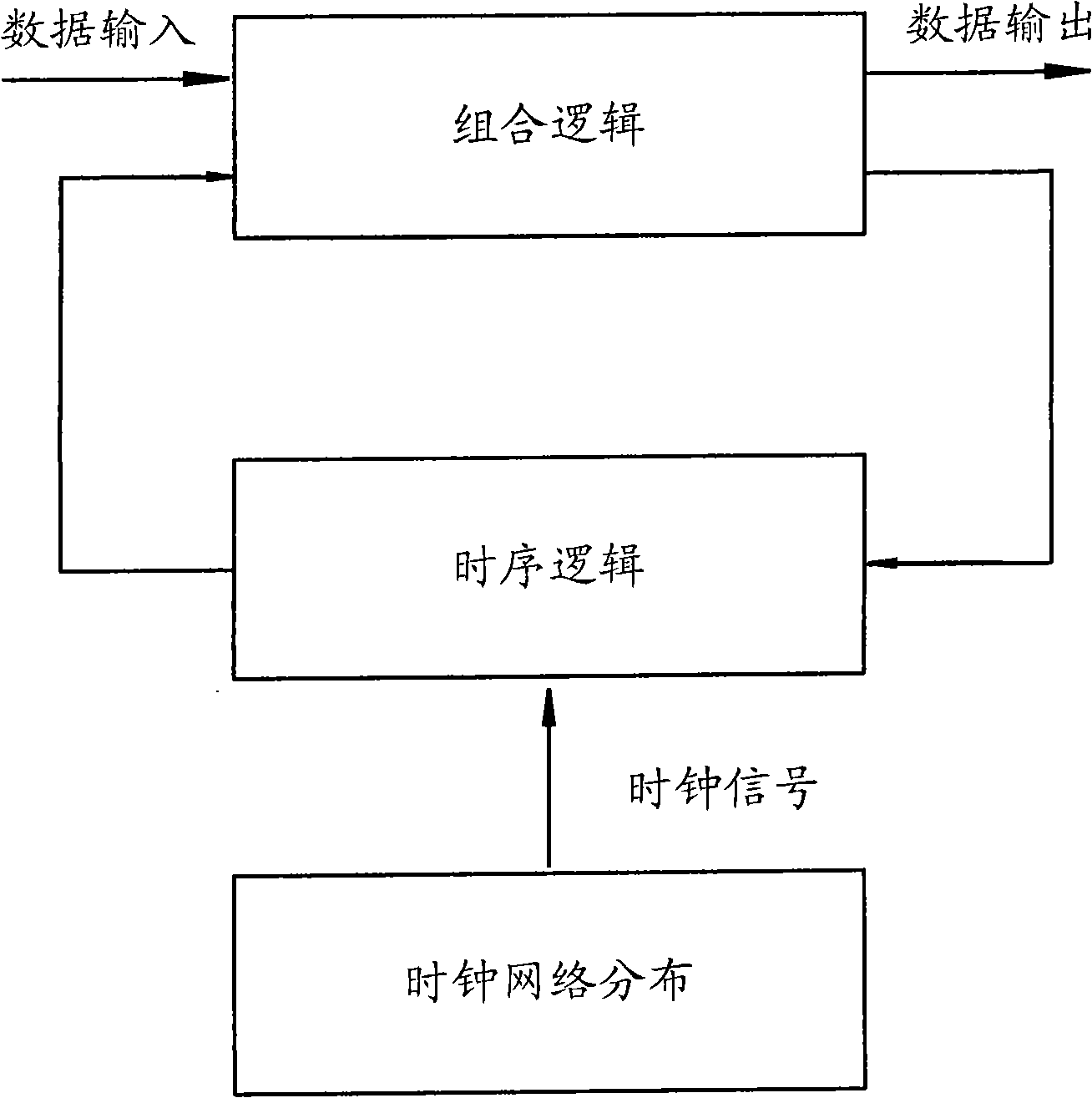

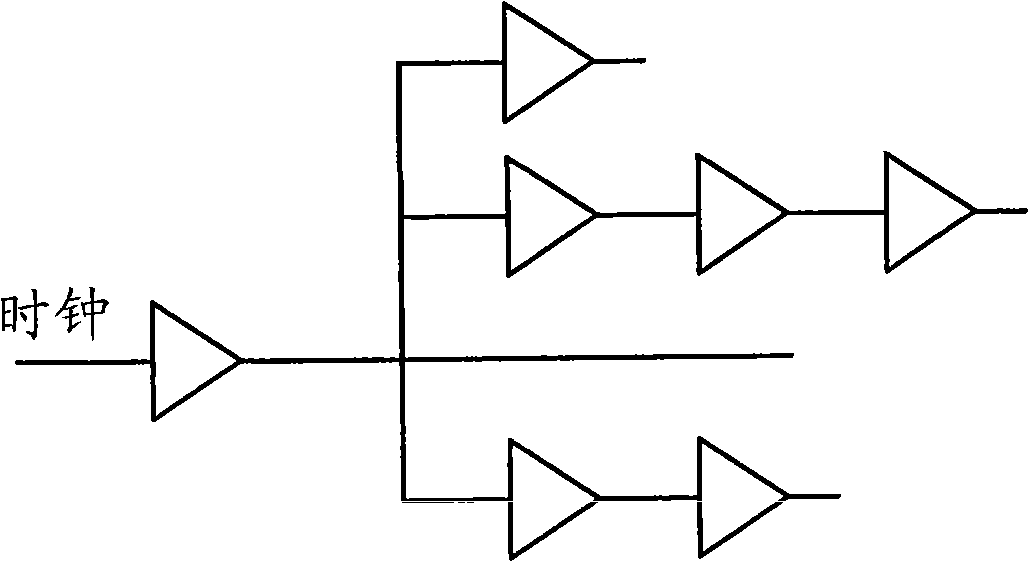

[0080] Reducing the dynamic power consumption in the circuit can be considered from two aspects: first, try to control the clock jumping activity of each node in the chip that does not work for the sequential logic function, and block its penetration into the circuit, thereby inhibiting its corresponding The dynamic power consumption; the second aspect, should try to improve the utilization rate of each clock jump activity, so that each jump, even the front and rear edges (rising edge and falling edge) of each jump can be used to realize the logic of the chip. Functional services, so that the number of clock jumps required to complete the same logic function is reduced, so as to achieve the purpose of reducing the amount of clock activity and reducing the dynamic power consumption of the circuit.

[0081] The embodiment of the present invention considers from the above-mentioned second aspect, in order to reduce the dynamic power consumption of the circuit, under the premise of...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More