DC interference suppressor circuit used for transimpedance preamplifier of infrared receiving system

A preamplifier, DC interference technology, applied in the direction of differential amplifiers, logic circuit coupling/interface using field effect transistors, DC coupled DC amplifiers, etc., can solve the problems of small gain, infrared remote control distance limitation, poor suppression ability, etc. , achieve the effect of stable active inductance value, suppression of interference signal and stable gain

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

specific Embodiment approach 1

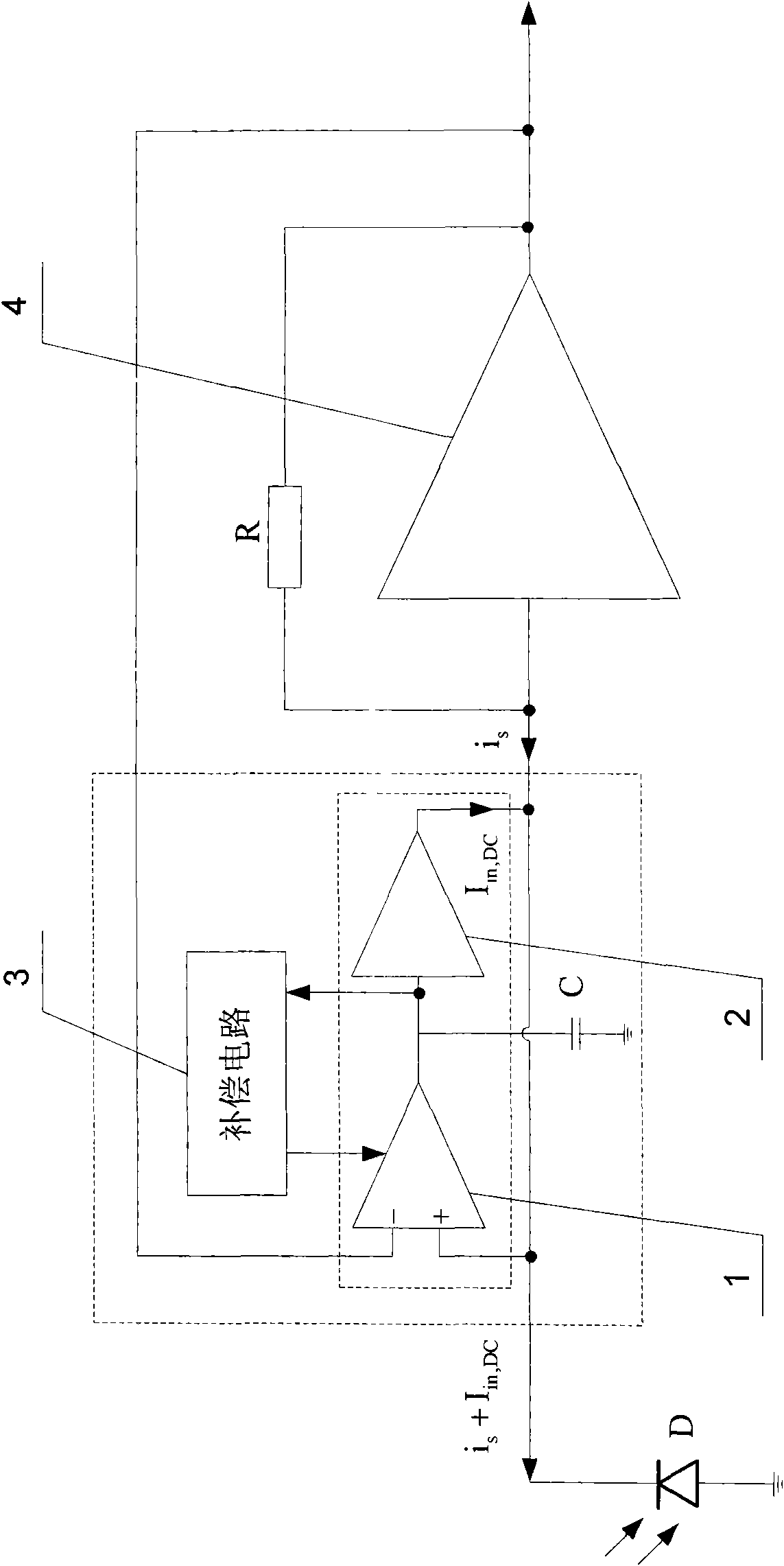

[0010] Specific implementation mode one: the following combination figure 1 Describe this embodiment, this embodiment comprises gyrator, compensation circuit 3 and capacitor C, gyrator comprises first transconductance operational amplifier 1 and second transconductance operational amplifier 2, the output end of first transconductance operational amplifier 1 is connected with the first transconductance operational amplifier 1 The input terminals of the two transconductance operational amplifiers 2 are connected, and the output terminal of the first transconductance operational amplifier 1 is connected with one end of the capacitor C, and the other end of the capacitor C is grounded. The output terminal of the first transconductance operational amplifier 1 and the connection point lead-out line of the input terminal of the second transconductance operational amplifier 2 are also connected with the input terminal of the compensation circuit 3, and the output terminal of the compen...

specific Embodiment approach 2

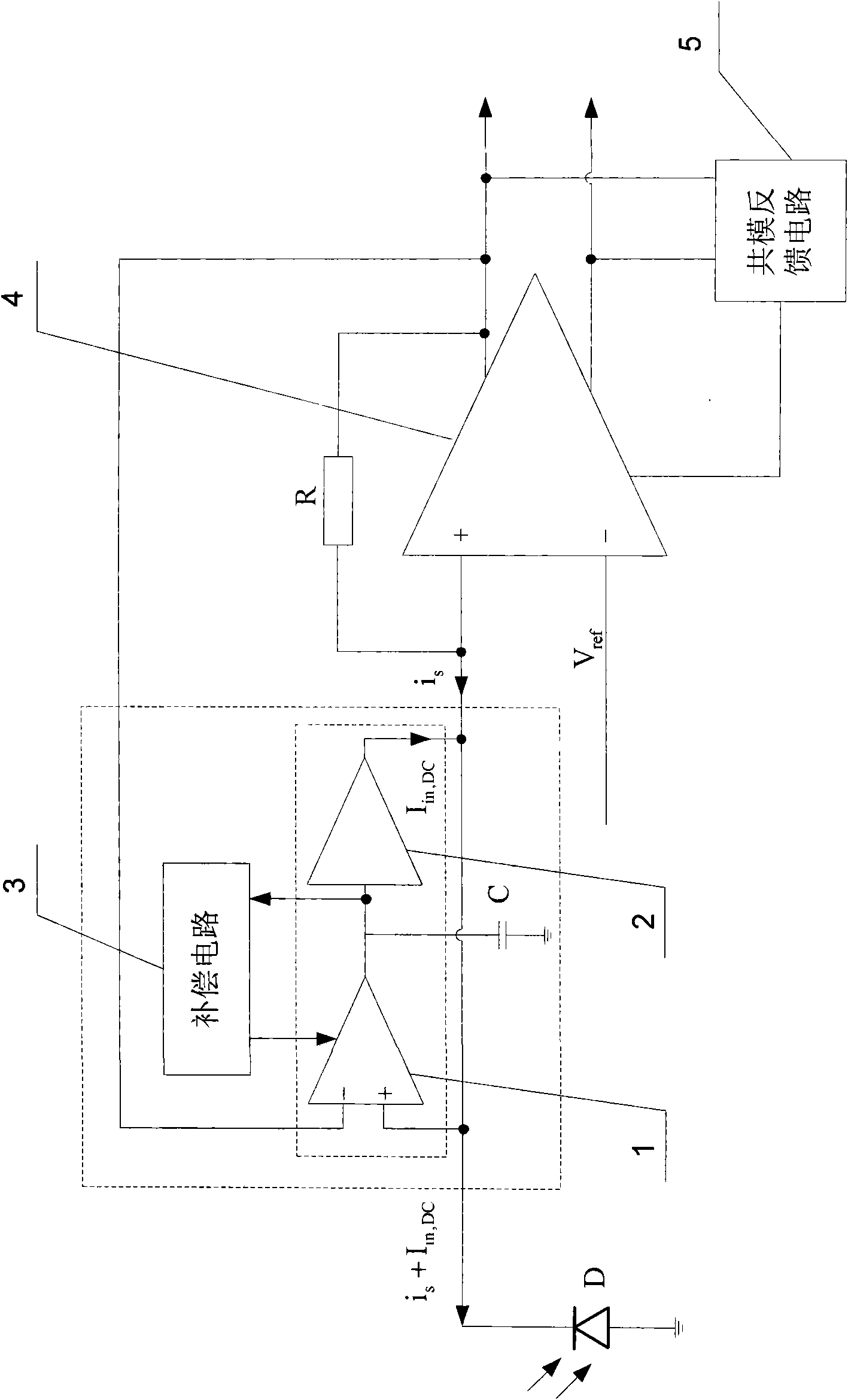

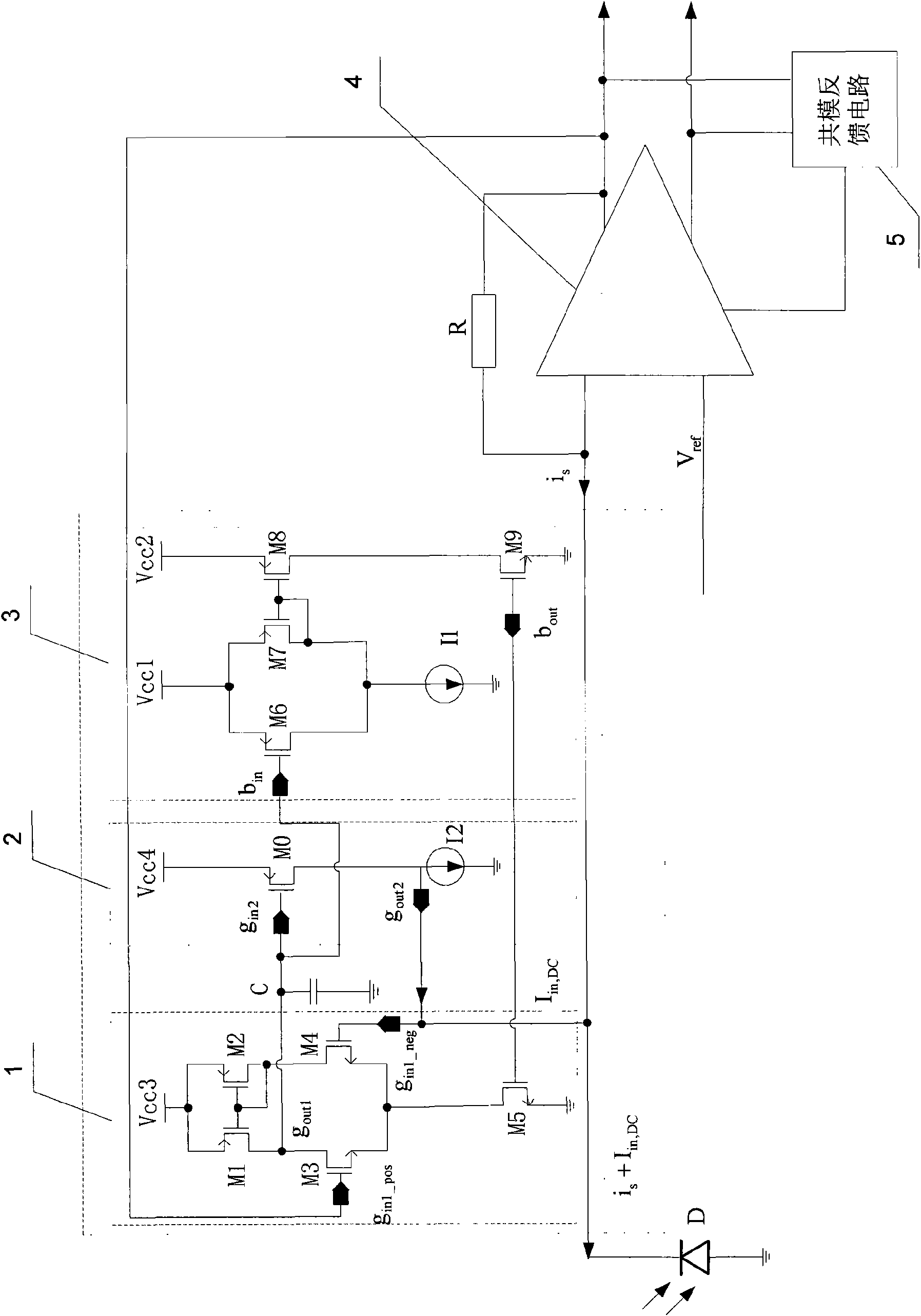

[0012] Specific implementation mode two: the following combination Figure 2 to Figure 8 This embodiment is described. The difference between this embodiment and the first embodiment is that the compensation circuit 3 includes a sixth MOS transistor M6, a seventh MOS transistor M7, an eighth MOS transistor M8, a ninth MOS transistor M9 and a first current source I1, the source of the sixth MOS transistor M6 is connected to the source of the seventh MOS transistor M7 and connected to the first power supply Vcc1, the drain of the sixth MOS transistor M6 is connected to the drain of the seventh MOS transistor M7 and connected to the first current The positive pole of the source I1 is connected, the negative pole of the first current source I1 is grounded, the gate of the seventh MOS transistor M7 is connected to the drain of the seventh MOS transistor M7, and the gate of the seventh MOS transistor M7 is also connected to the drain of the eighth MOS transistor M8. The gate is conn...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More