High-speed lossless data compression system based on content addressable memory

A lossless data compression and addressing memory technology, applied in memory systems, electrical digital data processing, memory address/allocation/relocation, etc., can solve the problems of limited RAM resources of hardware chips, indeterminate search cycles, and low compression rates. , to reduce the search delay, solve the speed problem, and improve the compression rate

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

specific Embodiment approach 1

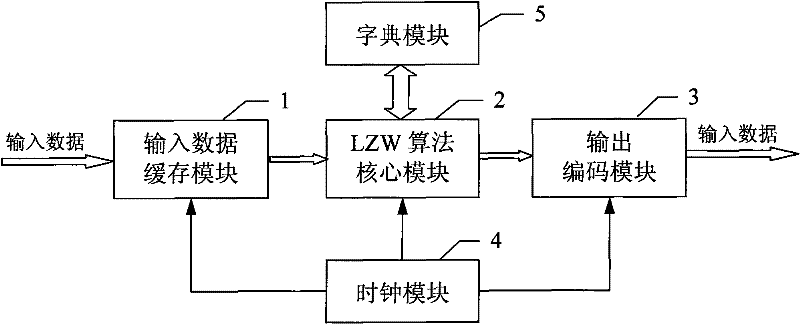

[0019] Embodiment one: a high-speed lossless data compression system based on content addressable memory, which includes a clock module 4, an input data cache module 1, a dictionary module 5, an LZW algorithm core module 2 and an output encoding module 3, wherein:

[0020] The clock module 4 is used to provide all clock signals required by the system;

[0021] The input data cache module 1 is composed of the first-in-first-out memory FIFO inside the FPGA, which is used to cache the input data, and provides the input data to the LZW algorithm core module in the form of data stream for compression;

[0022] The LZW algorithm core module 2 is used to receive the data stream output by the input data cache module 1; it is also used to compress the input data stream through the initialization, search, update and application of the LZW algorithm to the dictionary module 5, and compress the compressed The generated code stream is input to the output encoding module 3;

[0023] The ou...

specific Embodiment approach 2

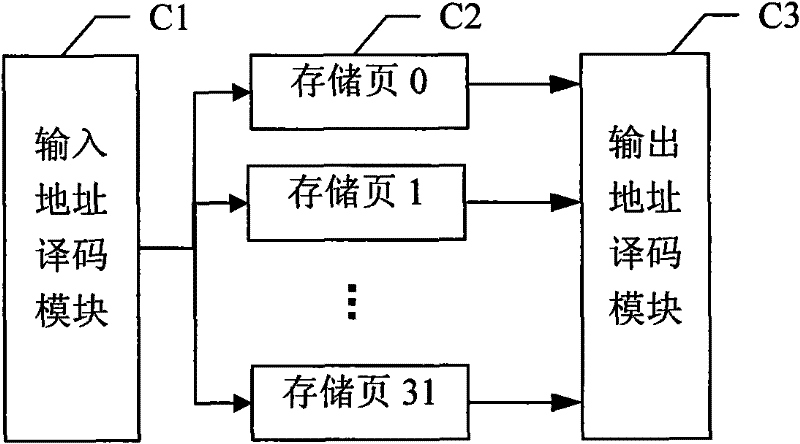

[0031] Embodiment 2: This embodiment further describes the structure of the dictionary module 5 in the content-addressable memory-based high-speed lossless data compression system described in Embodiment 1.

[0032] The CAM that constitutes dictionary module 5 described in the present embodiment is made up of 32 memory pages and an input address decoding module, an output address decoding module and a control module, and each memory page is made up of 16 memory banks; The address of the memory bank is 9 bits, and each bit width is 17 bits. The first 9 bits are used to store the prefix Prefix of the entity Entry, and the last 8 bits are used to store the suffix Suffix of the entity Entry. The structure of each memory bank is the same. The memory bank is composed of a comparator and a flip-flop, and the flip-flop is used to store data. When the write enable signal is valid, when a certain memory bank is selected, new data is written into the flip-flop in the memory bank to perfor...

specific Embodiment approach 3

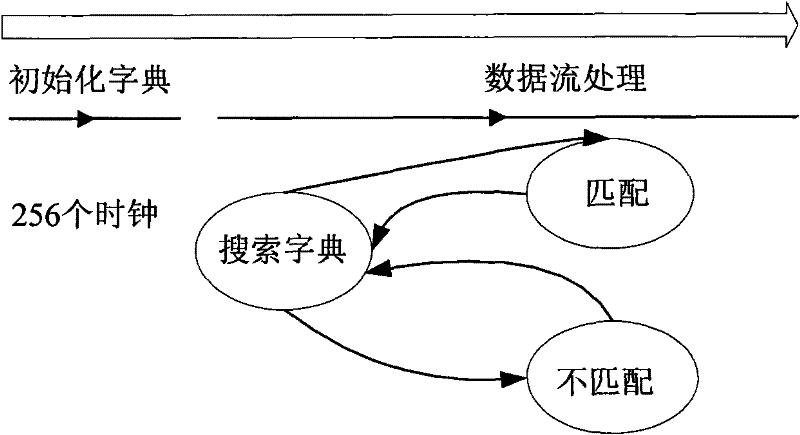

[0053] Embodiment 3: This embodiment further defines the structure of the LZW algorithm core module 2 in the content-addressable memory-based high-speed lossless data compression system described in Embodiment 1 or 2. The LZW algorithm core module 2 in this embodiment is composed of two nested state machines.

[0054] The two state machines described in this embodiment can be used to implement the system main program and the data compression program respectively. Wherein, the state machine for realizing data compression is nested in the state machine for realizing the main program of the system.

[0055] In this embodiment, the state machine used to implement the main program of the system has four working states, the work done by each working state and the mutual conversion process between the states can be found in Figure 6 Shown:

[0056] The idle state is used to judge the state of the reset signal Reset, and when the reset signal is valid Reset=1, it enters the initial...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More