Patents

Literature

33results about How to "Increase compression rate" patented technology

Efficacy Topic

Property

Owner

Technical Advancement

Application Domain

Technology Topic

Technology Field Word

Patent Country/Region

Patent Type

Patent Status

Application Year

Inventor

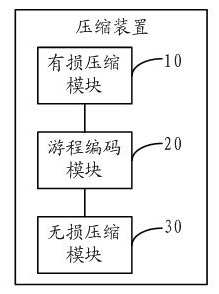

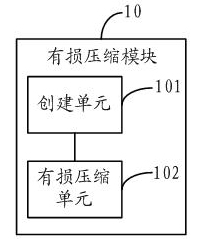

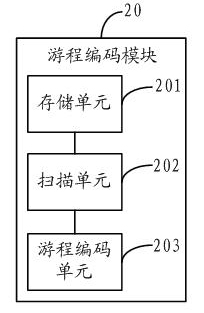

Method and device for compressing film thumbnails

ActiveCN102088604AReduce digitsSmooth displayTelevision systemsDigital video signal modificationThumbnailLossless compression

The embodiment of the invention discloses a method for compressing film thumbnails, comprising the following steps: carrying out loss compression on the film thumbnails to acquire film thumbnails with specific digits; carrying out run coding on the film thumbnails with the specific digits; and carrying out lossless compression on the film thumbnails which are subjected to the run coding to acquire compressed pictures. The embodiment of the invention also provides a device for compressing film thumbnails. In the invention, the loss compression, the run coding and the lossless compression are combined effectively to compress the film thumbnails, thus having the advantages of higher compression ratio, high compression efficiency, low degree of distortion and fast decoding speed.

Owner:SHENZHEN SKYWORTH DIGITAL TECH CO LTD

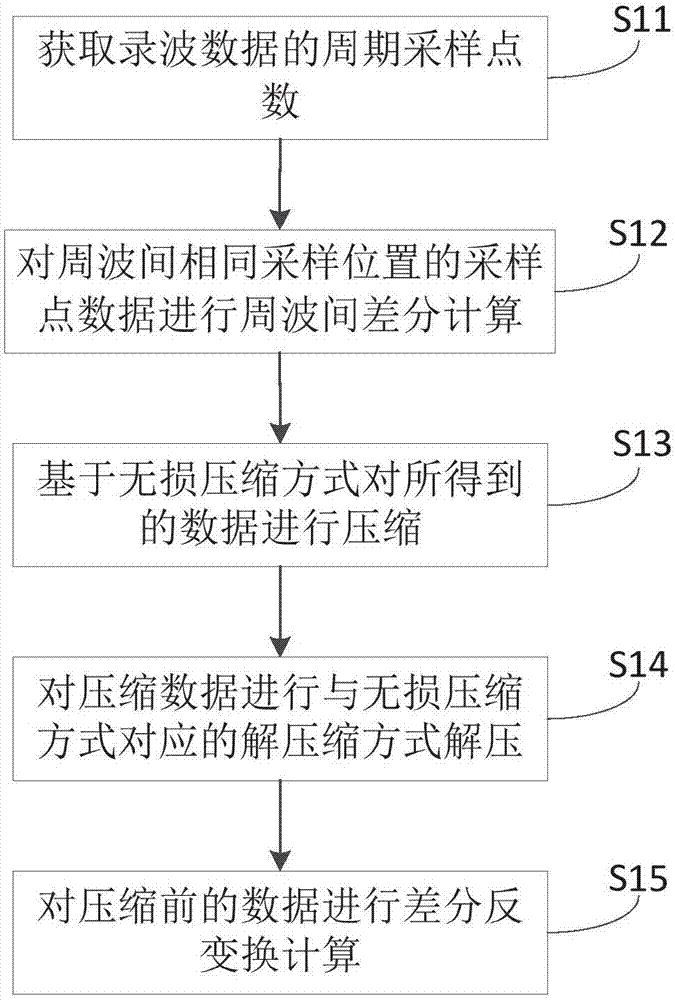

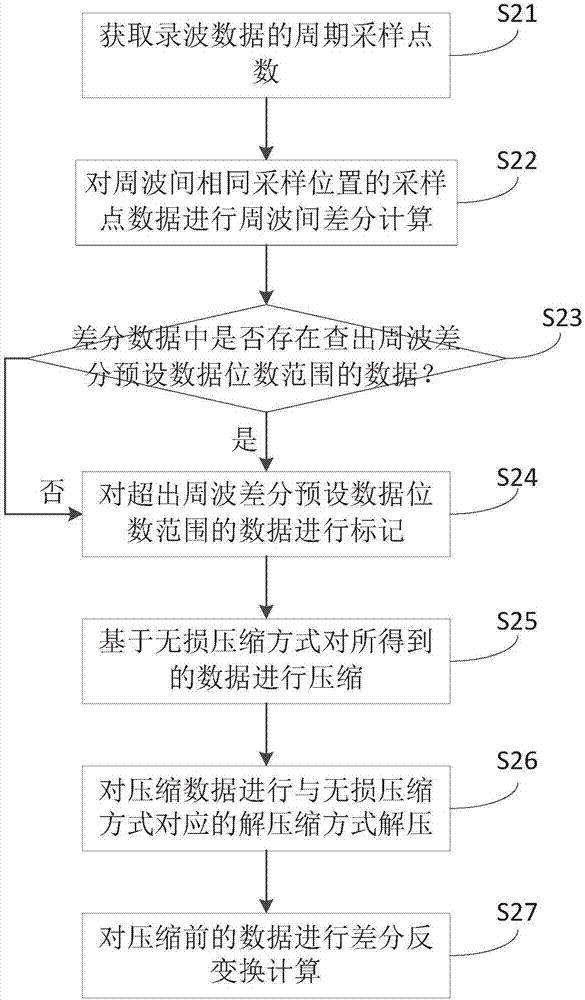

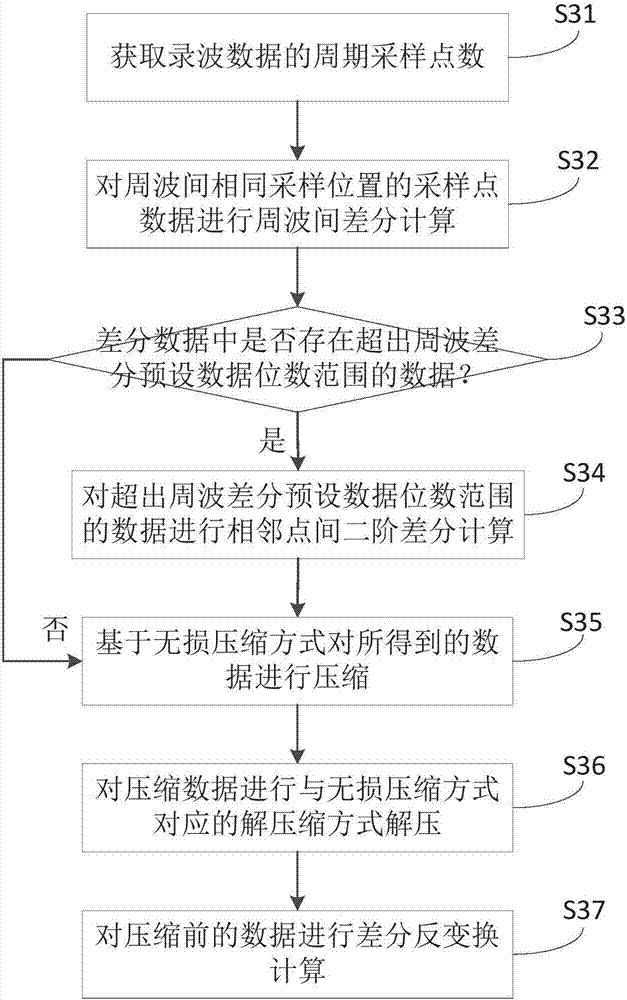

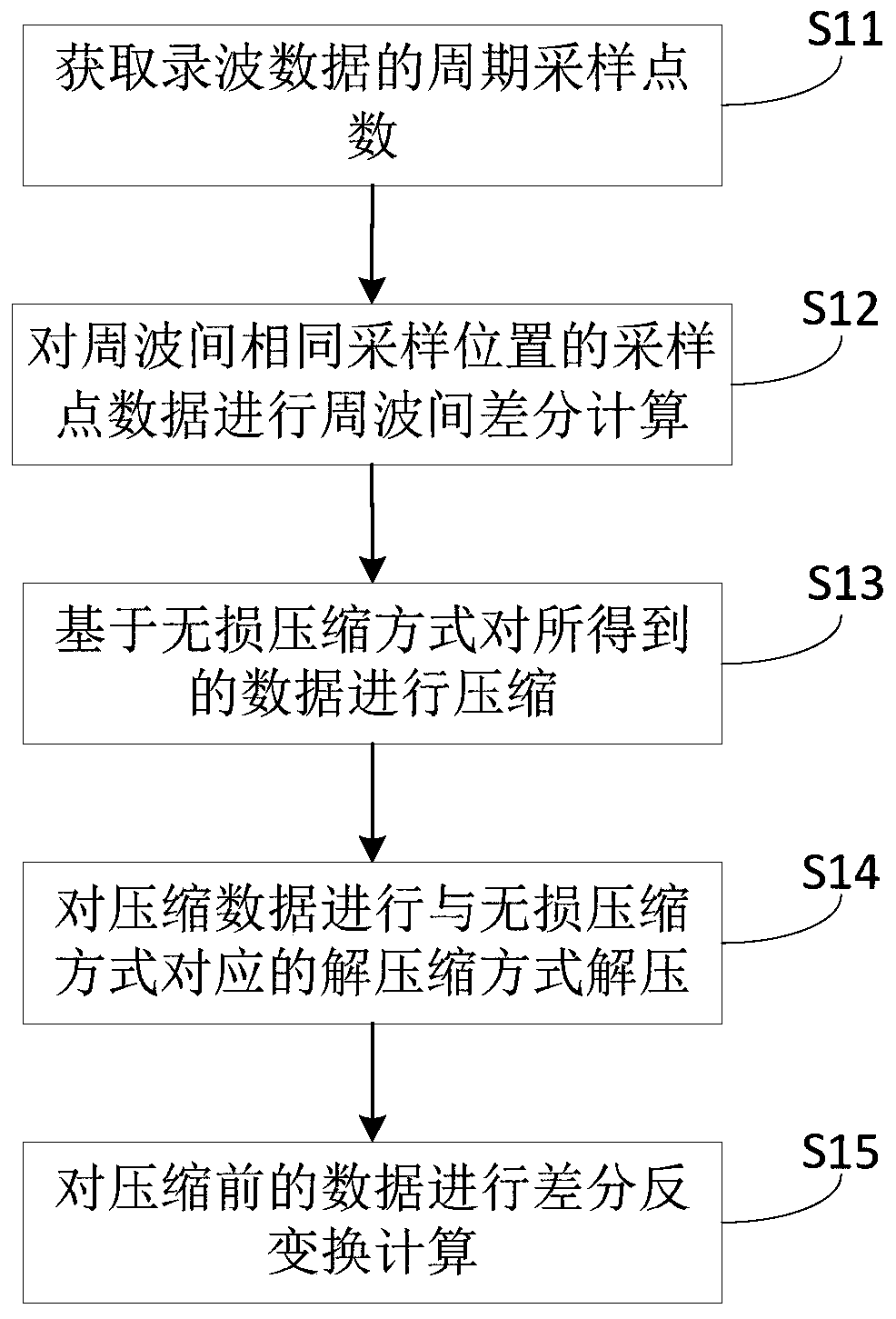

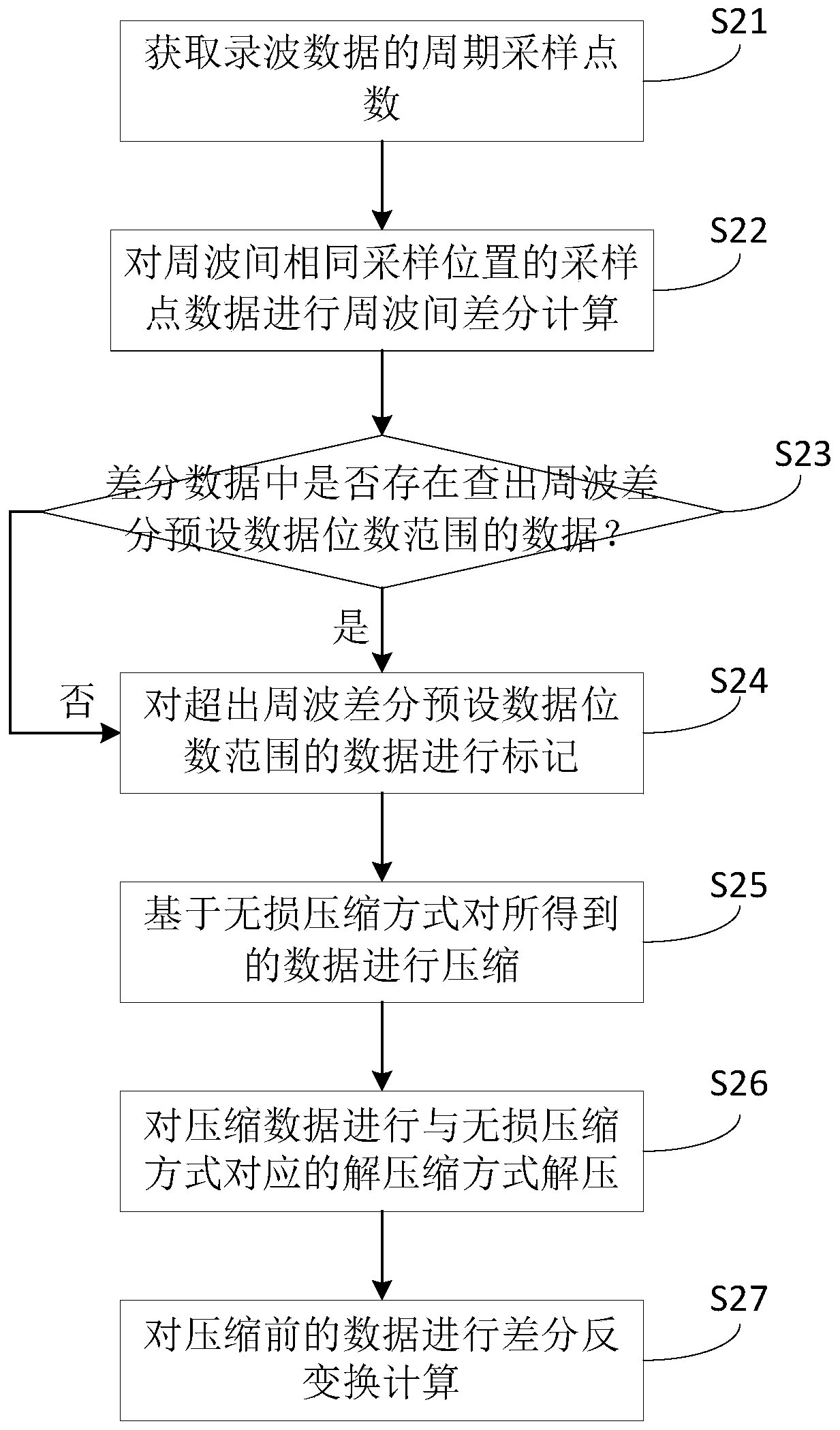

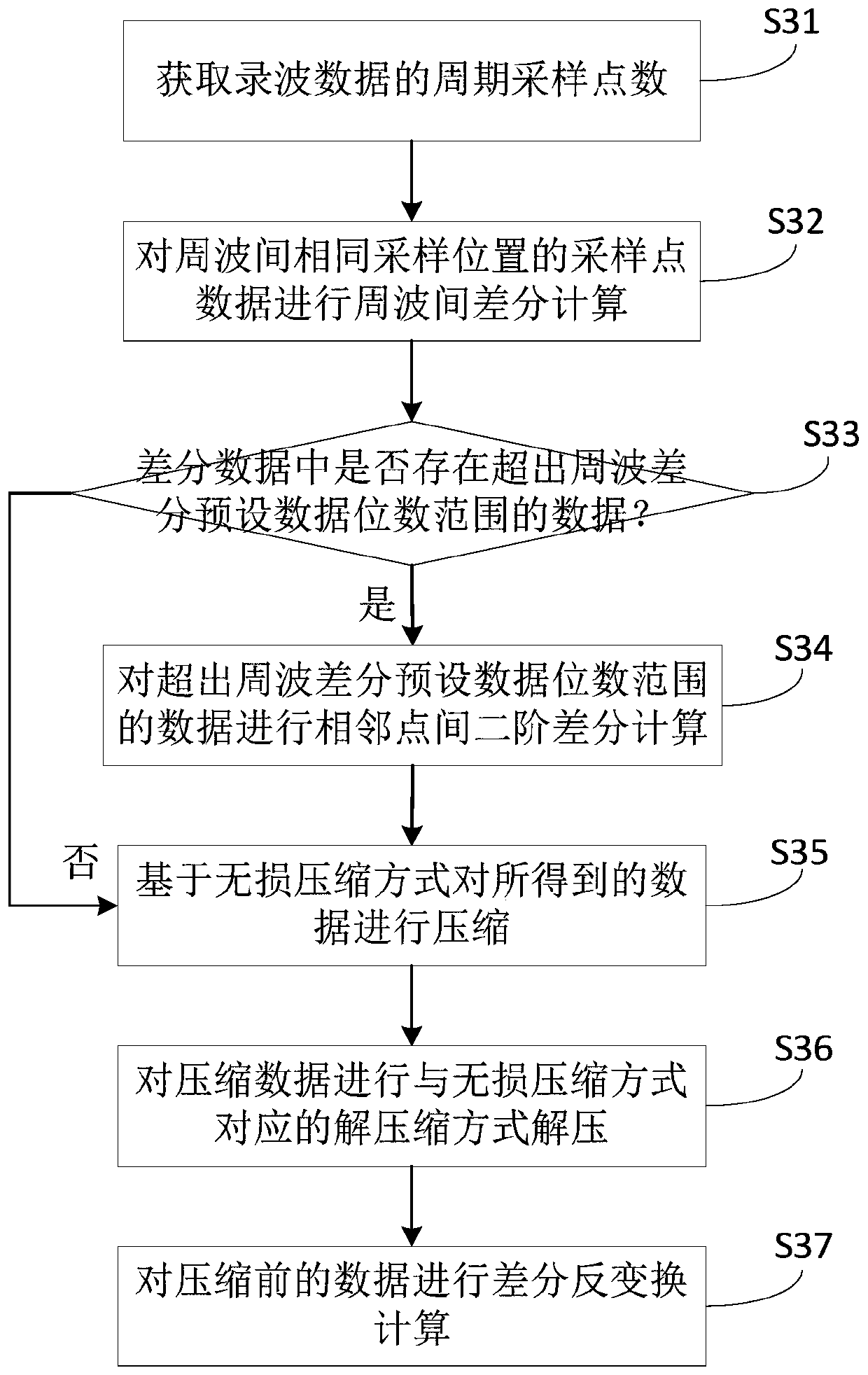

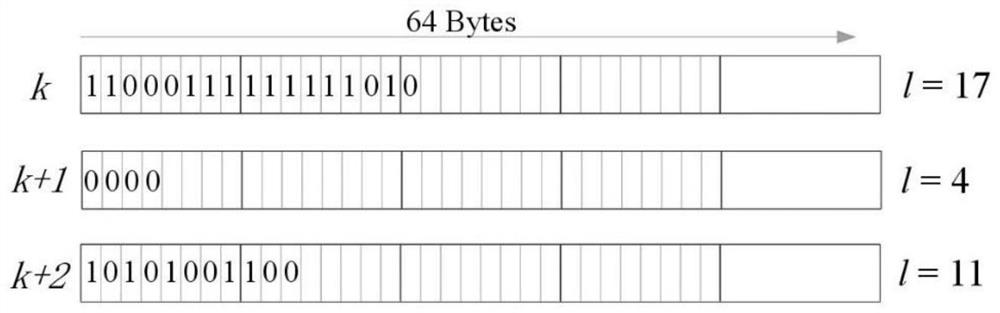

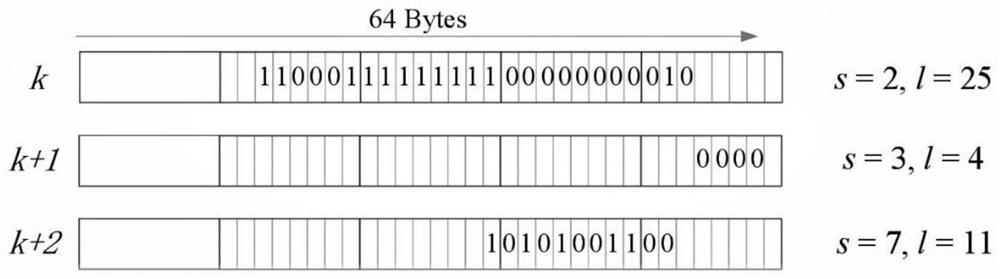

Recorded waveform data processing method and recorded waveform data processing device

ActiveCN107102220AReduce data volumeWithout breaking integrityElectrical testingPower qualityComputer terminal

The invention discloses a recorded waveform data processing method and a recorded waveform data processing device, wherein the recorded waveform data processing method comprises the steps of acquiring the number of periodical sampling points of recorded waveform data, wherein the recorded waveform data are electric energy quality monitoring data; and performing inter-cycle differential calculation on the sampling point data at the same position between the cycles for obtaining differential data, so that advantages of low subsequent processing data volume, high processing speed in compression or transmission, and the like are realized. The recorded waveform data processing method and the recorded waveform data processing device can reduce data volume of to-be-compressed data or to-be-transmitted data, thereby reducing compression calculation amount and data volume after compression, and improving compression rate. Furthermore the recorded waveform data processing method and the recorded waveform data processing device can relatively effectively reduce storage and / or transmission load of the mass recorded waveform data of an electric energy quality monitoring terminal.

Owner:GLOBAL ENERGY INTERCONNECTION RES INST CO LTD +1

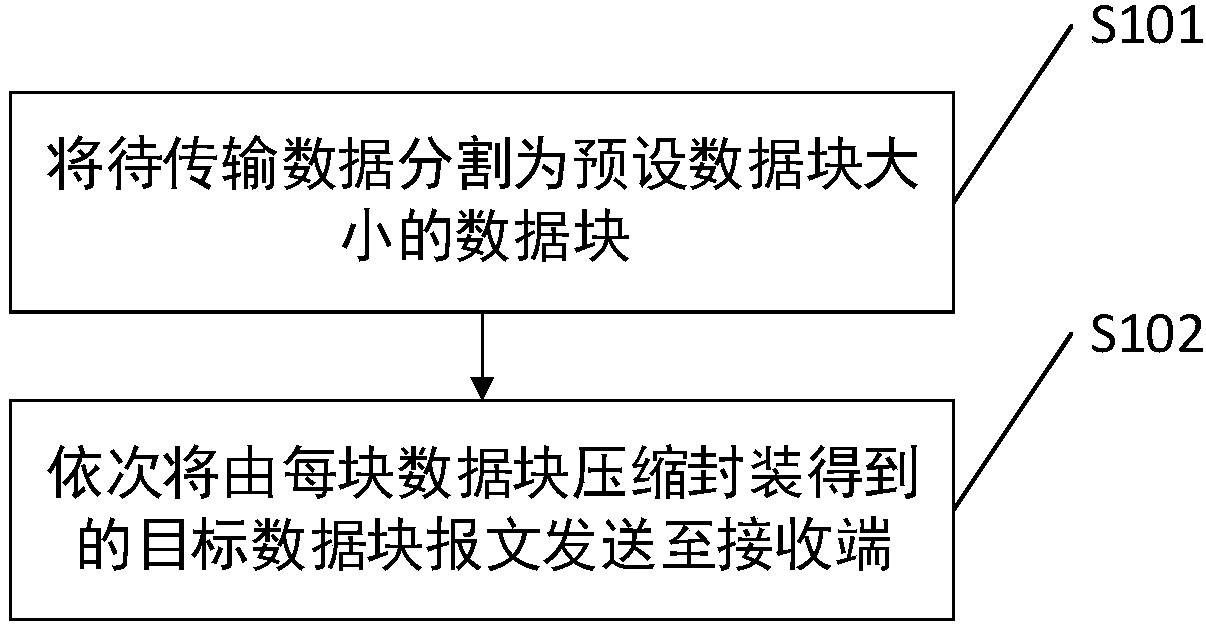

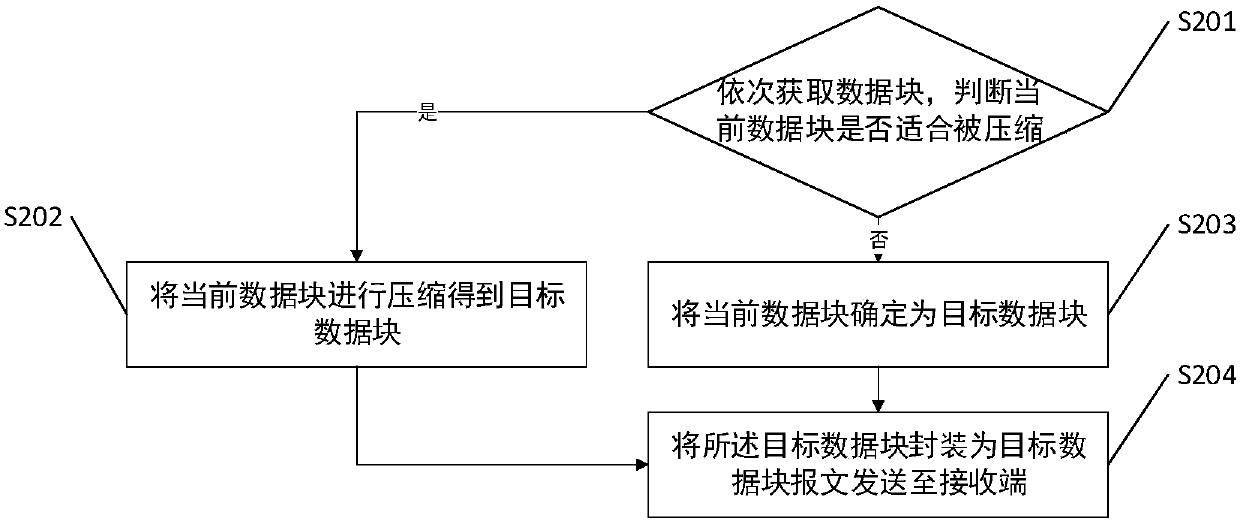

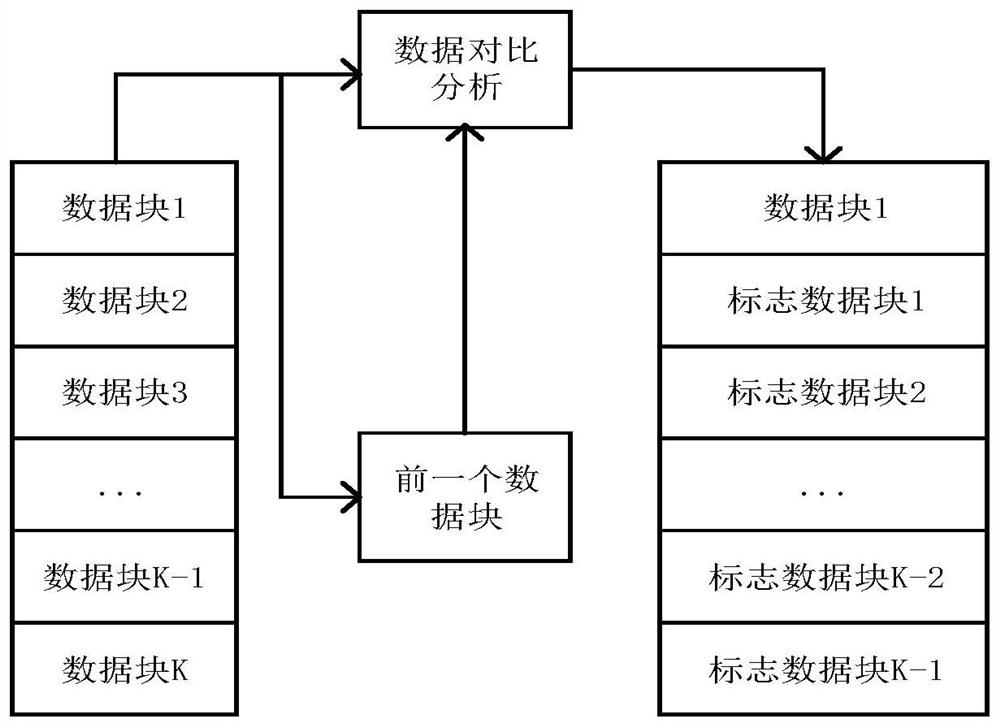

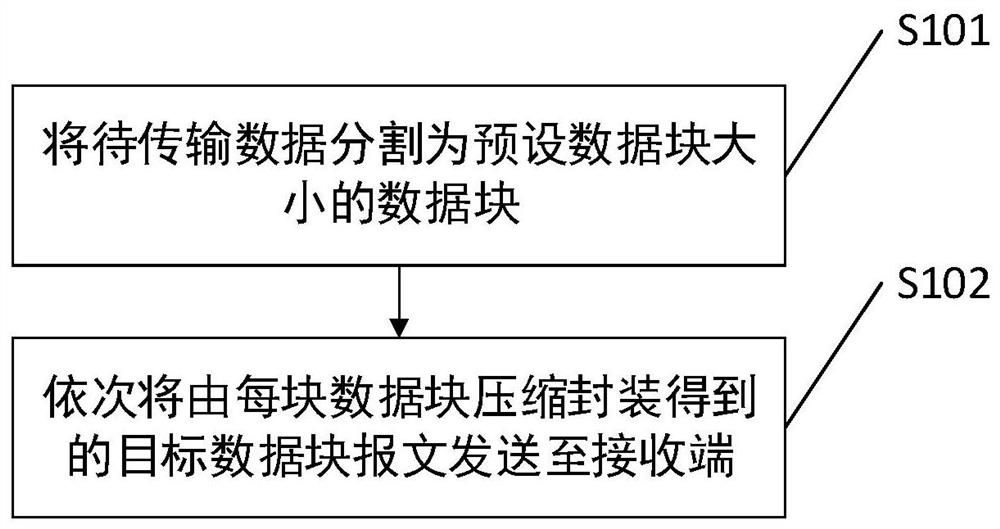

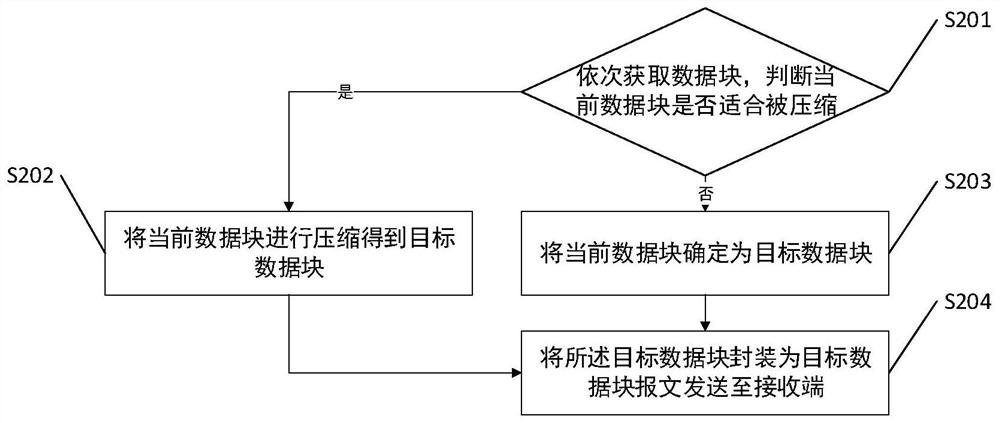

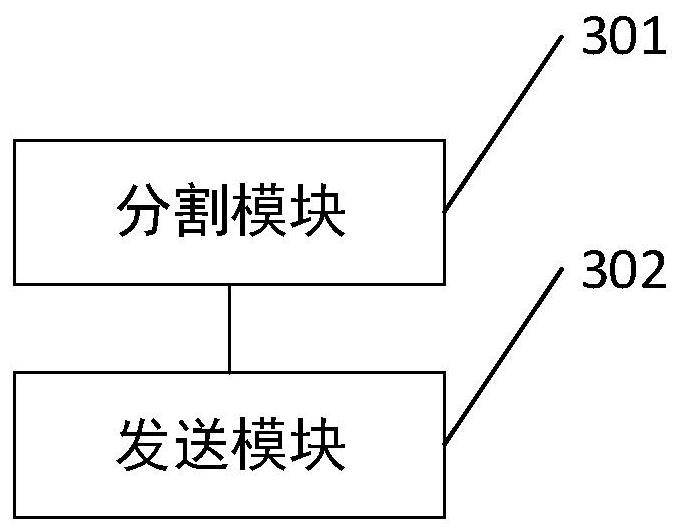

Data transmission method, device and system

ActiveCN109756536AReduce the amount of calculation and transmissionAvoid computing resourcesTransmissionData transmissionData compression

The invention discloses a data transmission method. The method comprises the following steps: dividing data to be transmitted into data blocks with preset data block sizes; and sequentially sending the target data block message obtained by compressing and packaging each data block to a receiving end. Therefore, the data can be partitioned before data transmission, compressed and packaged one by one, and then sent to a receiver one by one, so that the one-time calculation amount and transmission amount are effectively reduced, consumption of a large number of calculation resources is avoided, and the transmission speed can be effectively increased. Meanwhile, each data block can be judged, if the current data block does not need to be compressed, computing resources are not wasted to compress the current data block, the data compression rate is further increased, and therefore the data transmission rate is increased. The embodiment of the invention further provides a data transmission device and system, and the above technical effects can also be achieved.

Owner:ZHUZHOU CSR TIMES ELECTRIC CO LTD

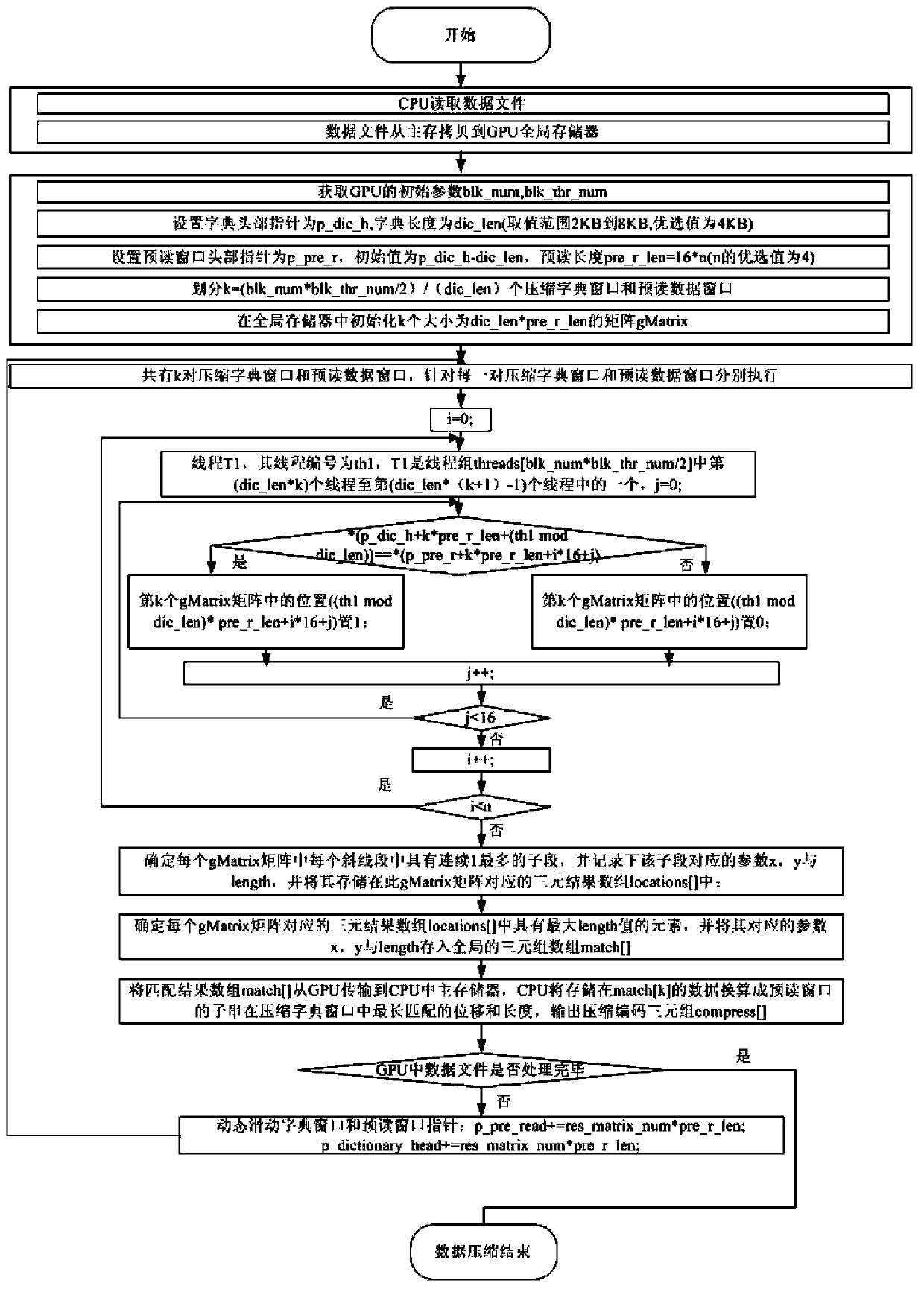

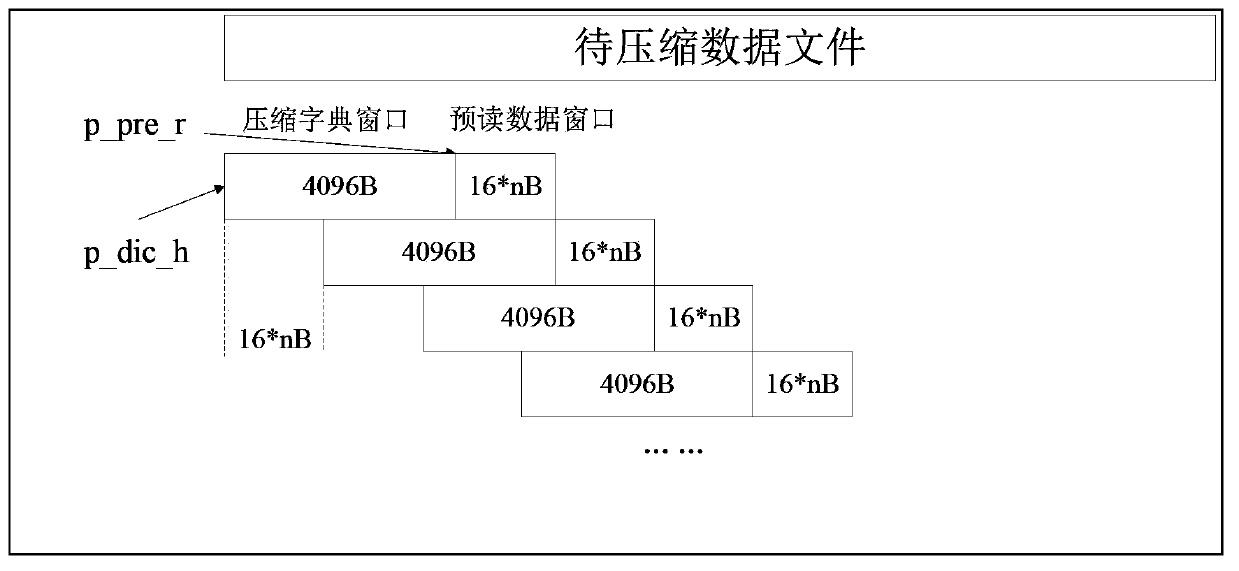

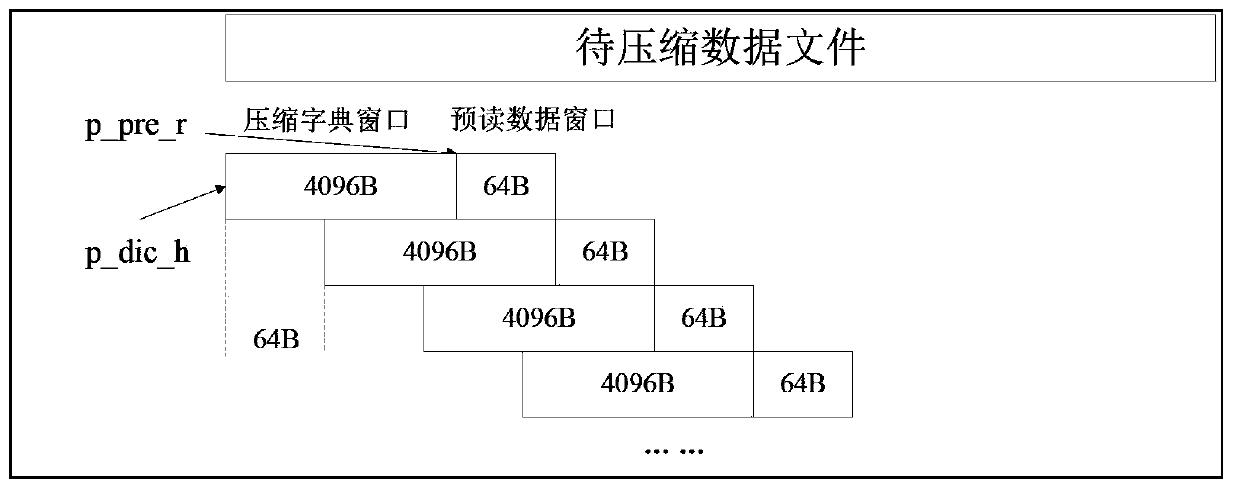

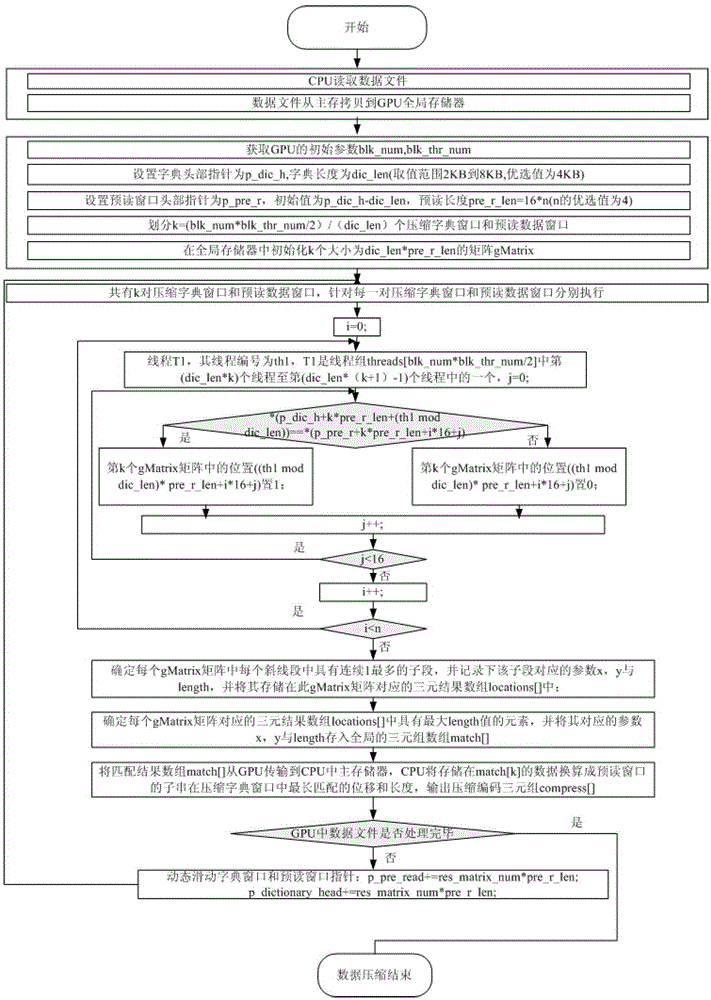

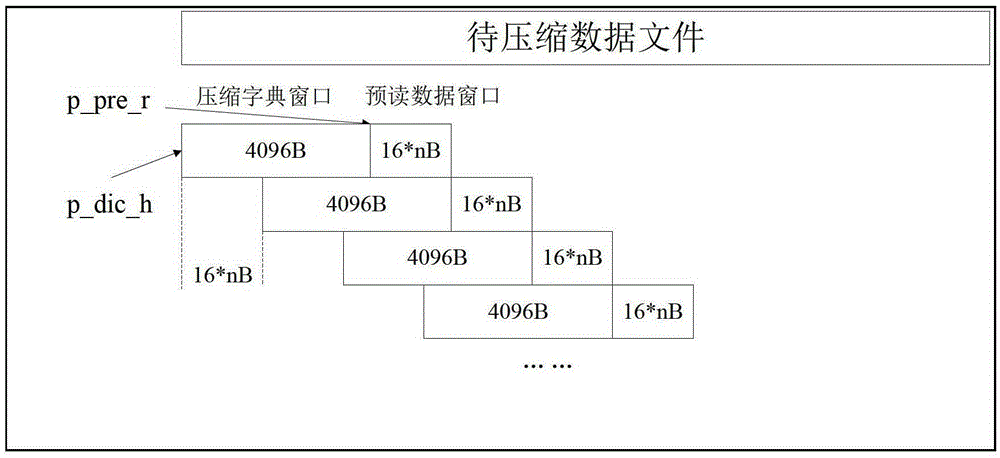

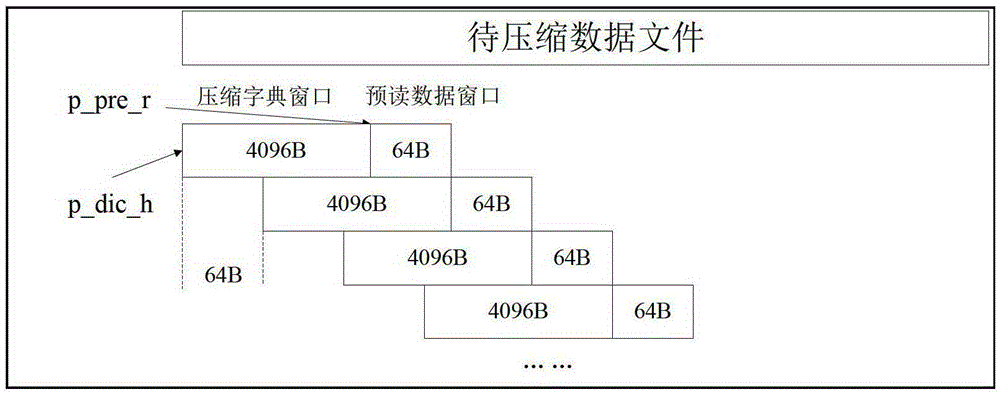

High-speed lossless data compression method based on GPU-CPU hybrid platform

ActiveCN103427844AImprove matching speedShorten the timeCode conversionData compressionArray data structure

The invention discloses a high-speed lossless data compression method based on a GPU-CPU hybrid platform. The method includes: allowing a CPU to read a data file to be compressed, copying the data file to be compressed from a memory to a global memory of a GPU, setting a thread block set bk(a) of the GPU, setting the number b of threads in each thread block, setting a length c of a compression dictionary window, setting a head hand p_dic_h pointing to a first compression dictionary window, setting the size d of a pre-reading window, setting a hand p_pre_r pointing to a first pre-reading window, setting an initial value p_dic_h-c of the hand, initializing an operating thread set threads(a*b), c*d in size, and (a*b / 2) / c matrixes gMatrix, calling the (a*b / 2)-th thread in the operating thread set threads(a*b) to process q=(a*b / 2) / c data, c+d in length, in the data file to be compressed, searching for oblique segments having most continuous 1 from each of the q result matrixes gMatrix, and determining a three-element result array locations(p) of each result matrix. The method has the advantage that compression rate of massive data can be increased greatly.

Owner:HUAZHONG UNIV OF SCI & TECH

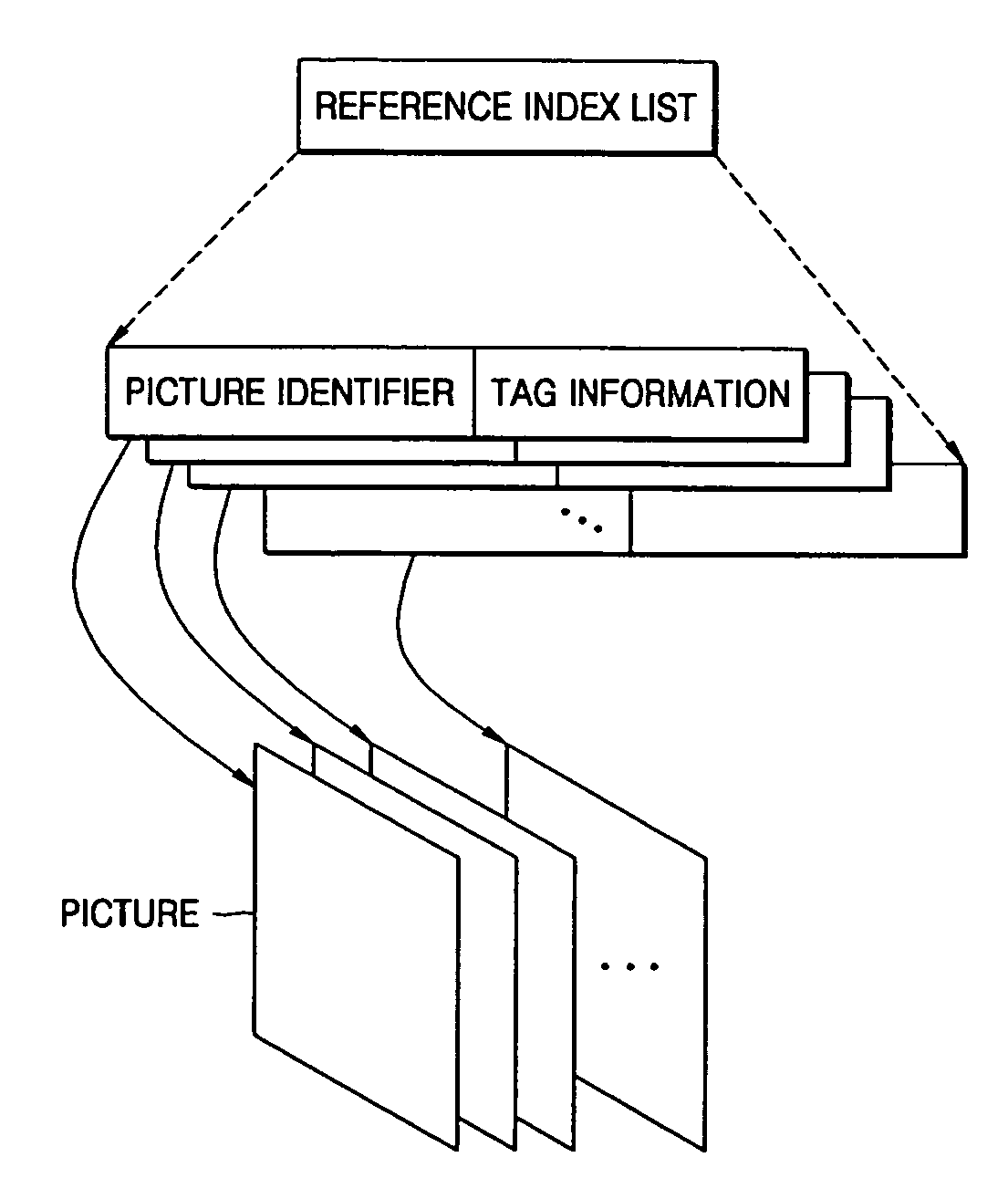

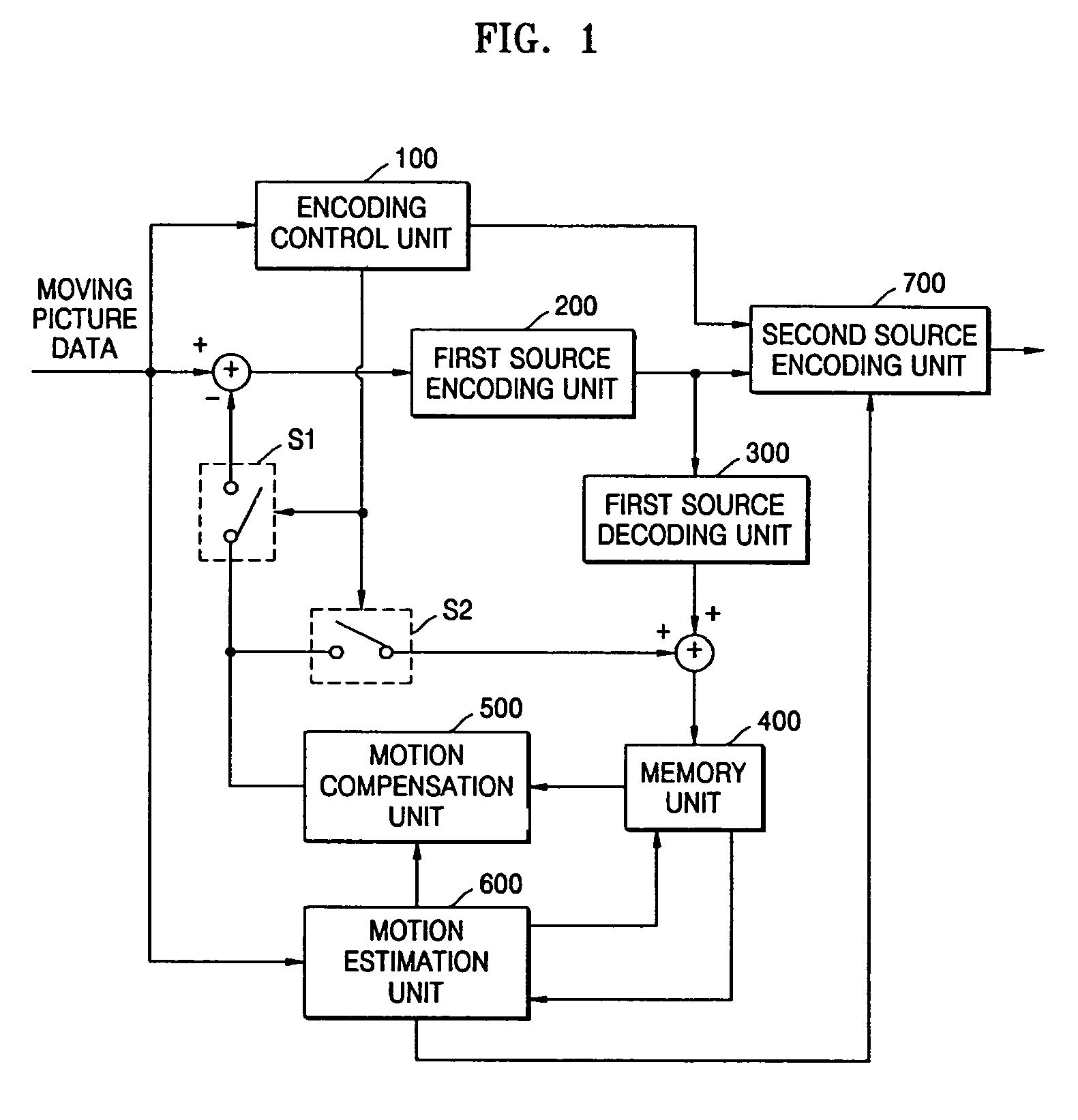

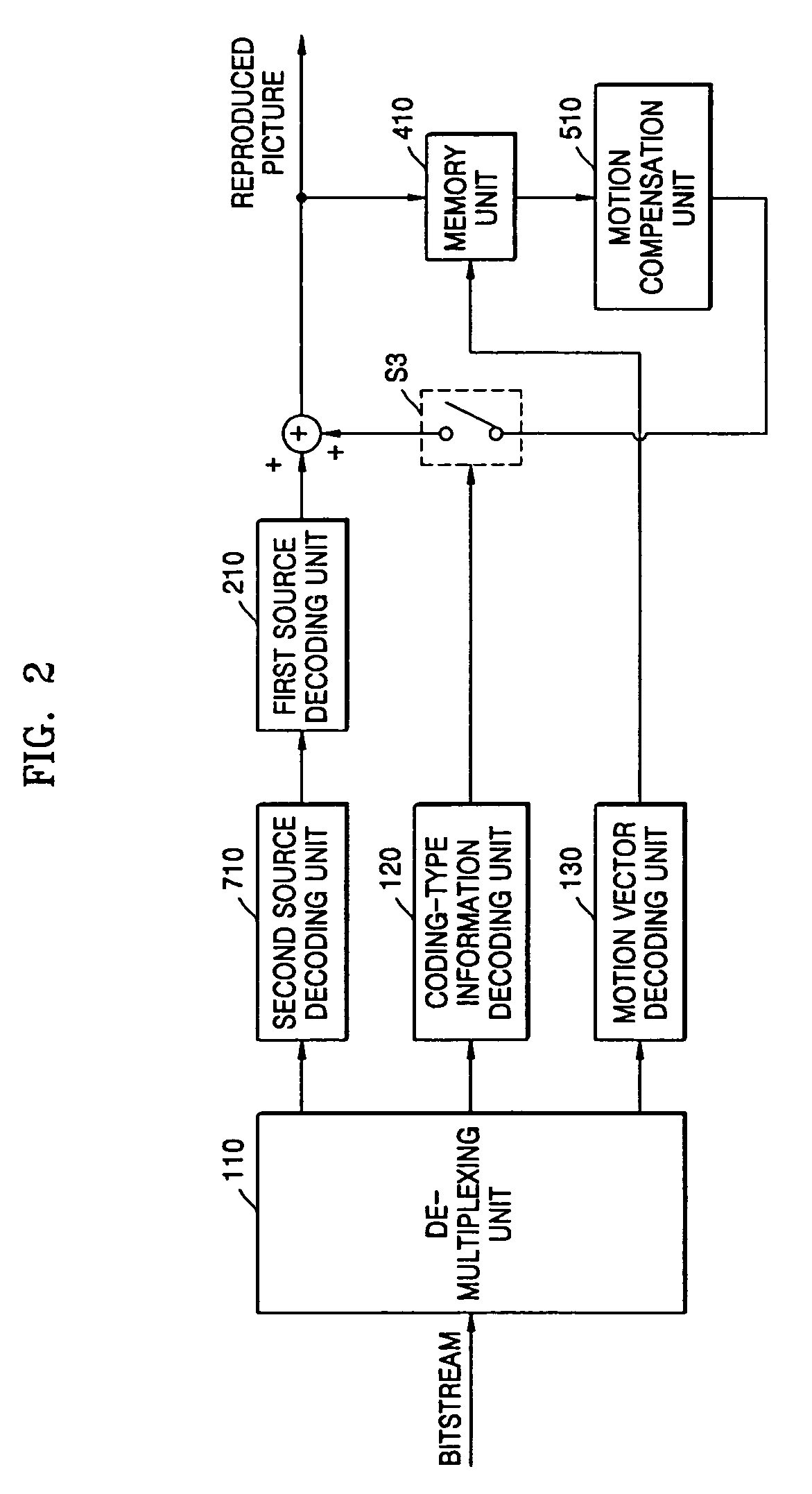

Method of determining reference picture, method of compensating for motion and apparatus therefor

InactiveUS7646811B2Increase compression rateImprove image qualityPicture reproducers using cathode ray tubesPicture reproducers with optical-mechanical scanningComputer vision

Owner:SAMSUNG ELECTRONICS CO LTD

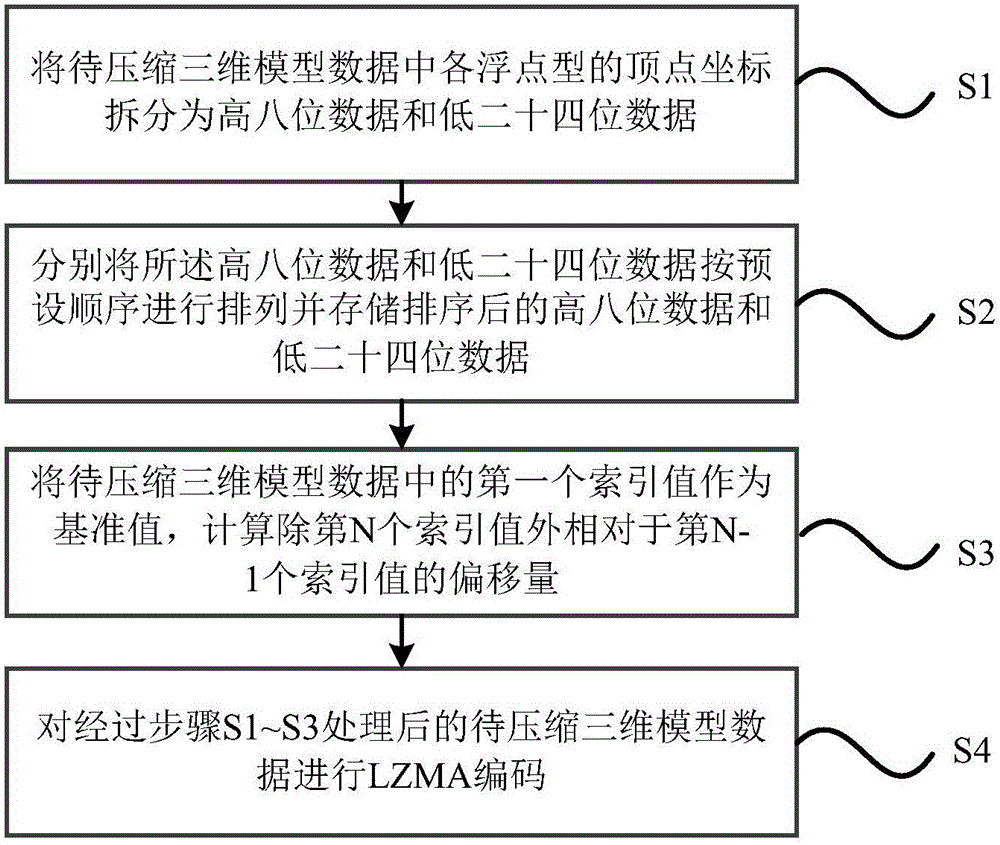

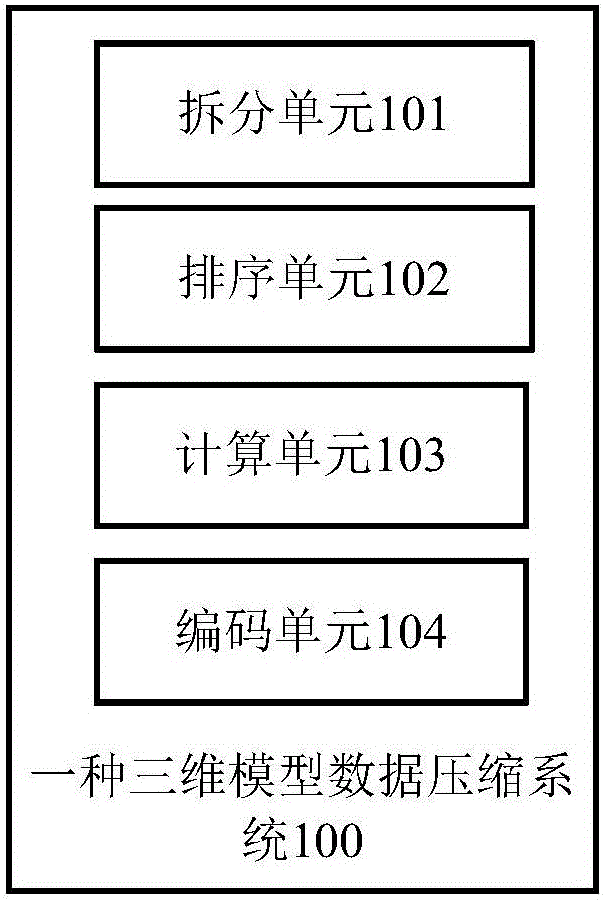

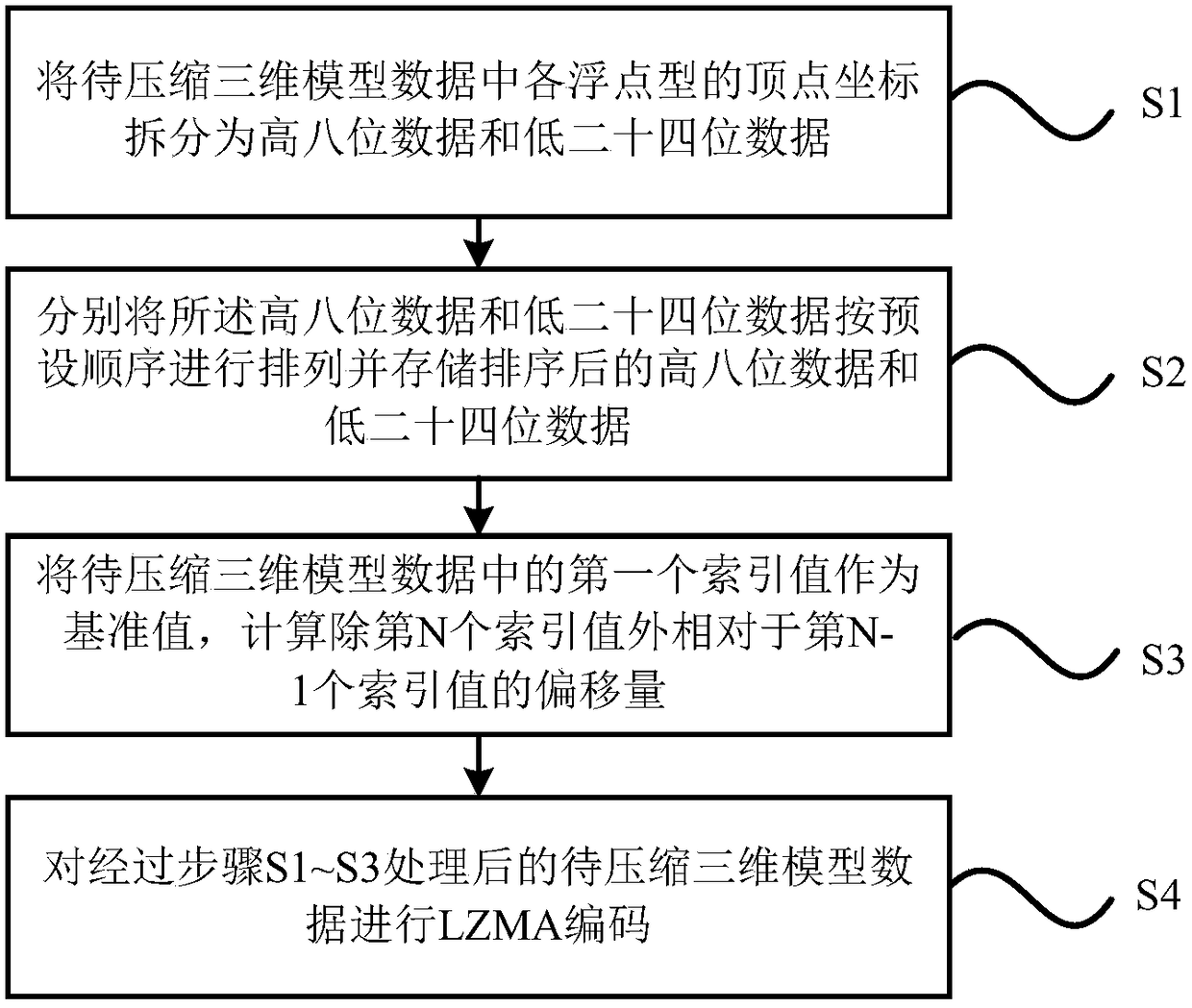

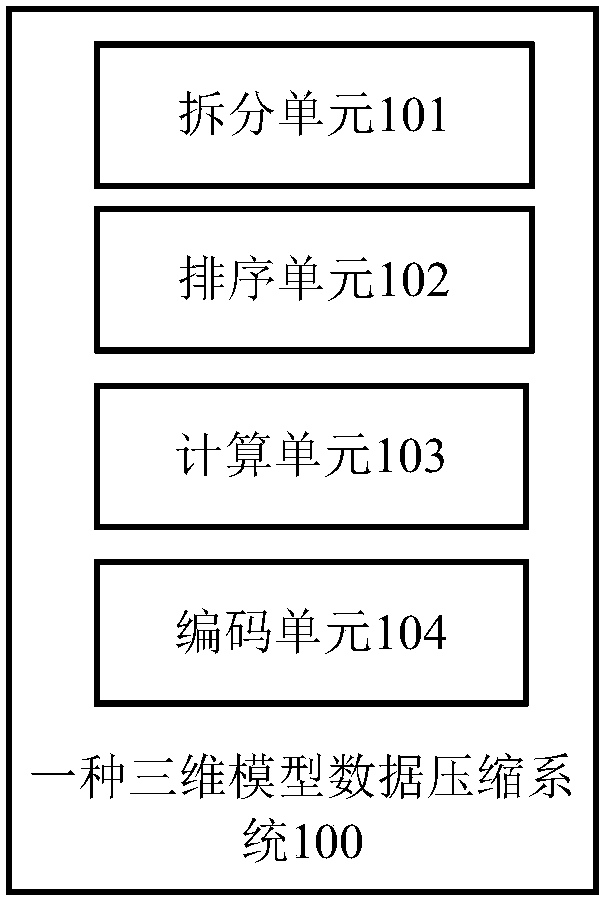

Three-dimensional model data compression method and system

ActiveCN105931279AIncrease the compression ratioIncrease compression rateImage coding3D modellingData compression24-bit

The invention specifically relates to a three-dimensional model data compression method and system, and the method comprises the steps: enabling each floating-type top coordinate in to-be-compressed three-dimensional model data to be divided into high 8-bit data and low 24-bit data; respectively arranging the high 8-bit data and low 24-bit data according to a preset sequence, and storing the ordered high 8-bit data and low 24-bit data; enabling a first index value in the to-be-compressed three-dimensional model data to serve as a reference value, and calculating the offset relative to an (N-1)-th index value except the N-th index value, wherein the index value is an integer, the offset of the N-th index value relative to the (N-1)-th index value is equal to the difference between the N-th index value and the (N-1)-th index value, and N is not less than two; and carrying out the LZMA coding of the to-be-compressed three-dimensional model data processed through the above steps. Through the above technical scheme of the invention, the method can improve the compression rate of three-dimensional model data.

Owner:邱友龙

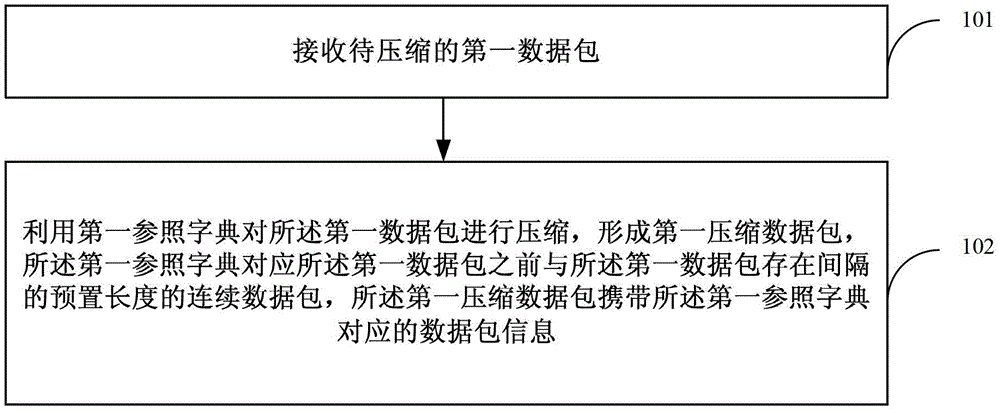

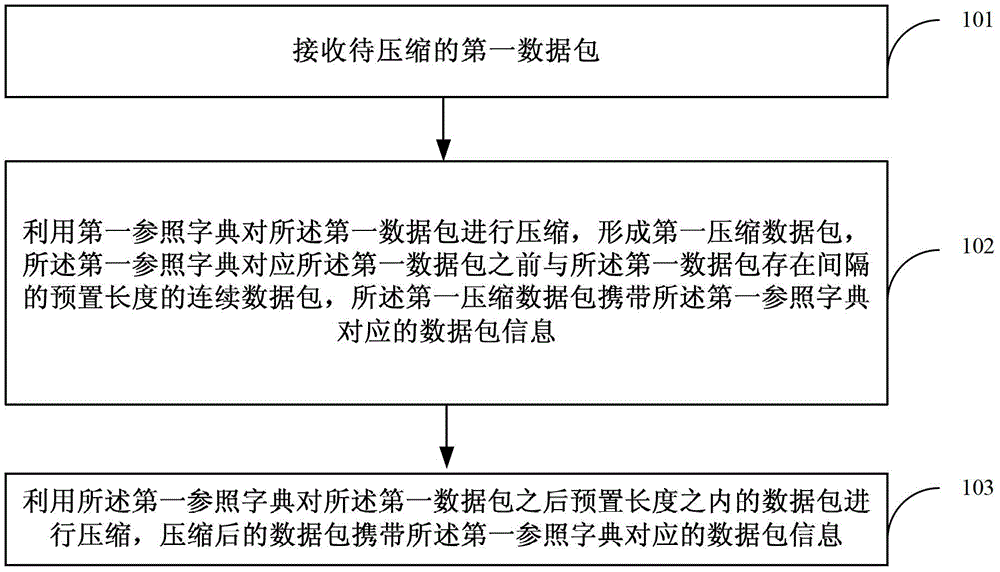

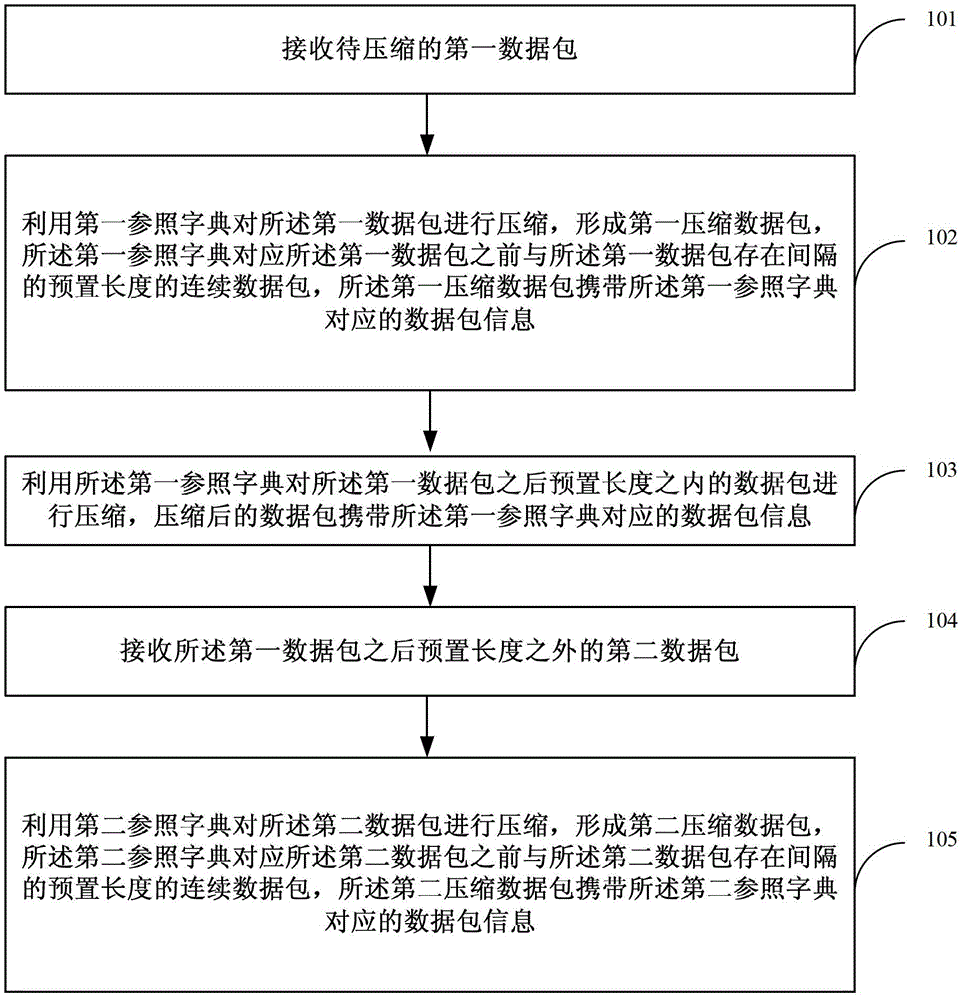

A data compression and decompression method and device

ActiveCN103281156BIncrease compression rateAvoid decompression waitError preventionData compressionNetwork packet

The embodiment of the invention discloses methods and devices for compressing and decompressing data. The method for compressing the data comprises the following steps of receiving a first data packet to be compressed; and compressing the first data packet by utilizing a first reference dictionary, so as to form a first compressed data packet, wherein spaced continuous data packets with preset length exist between the first reference dictionary and the first data packet before the first reference dictionary is corresponding to the first data packet, the first compressed data packet carries data packet information corresponding to the first reference dictionary. According to the methods and devices disclosed by the embodiment of the invention, the data compression efficiency and the data decompression efficiency can be improved.

Owner:NANTONG HANGDA ELECTRONICS TECH

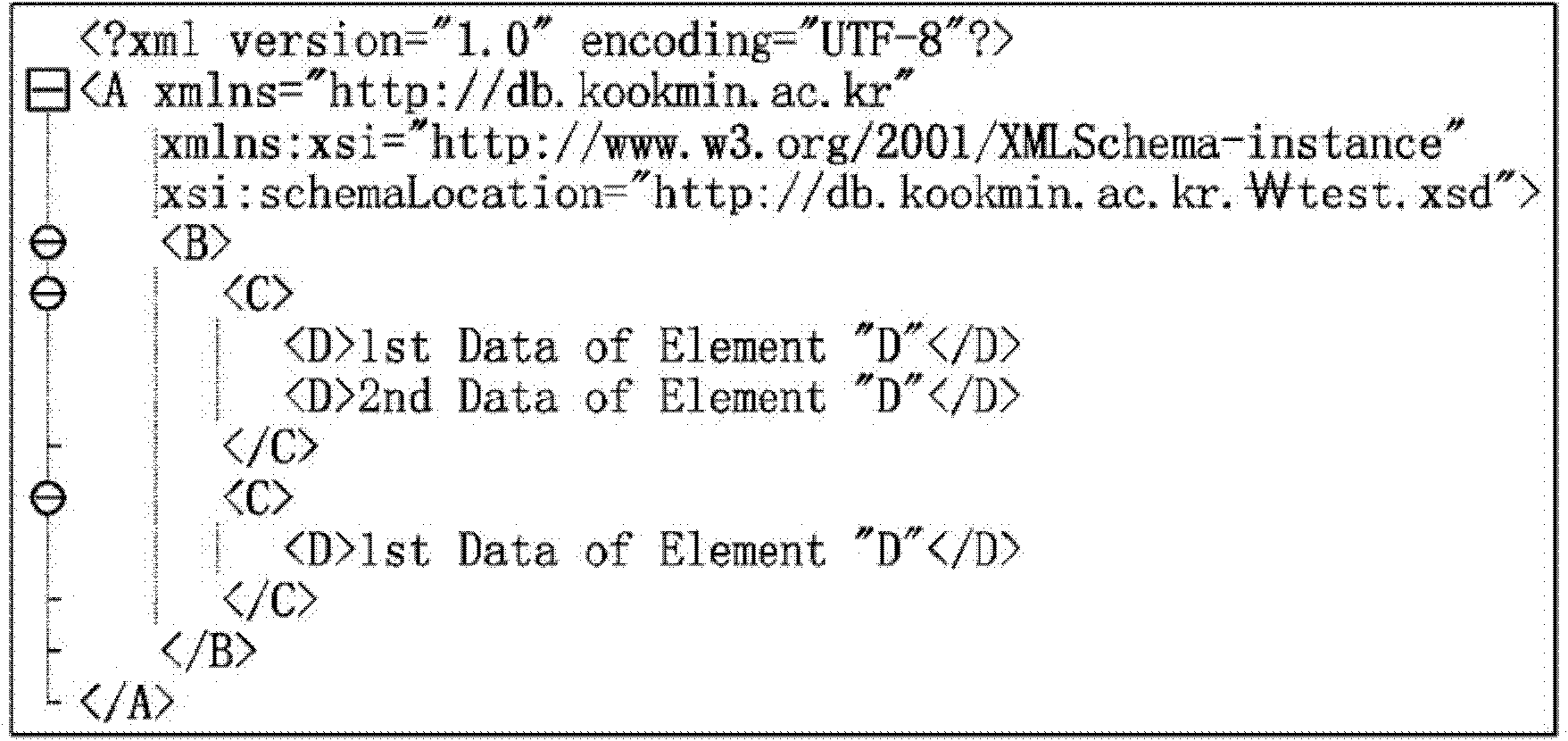

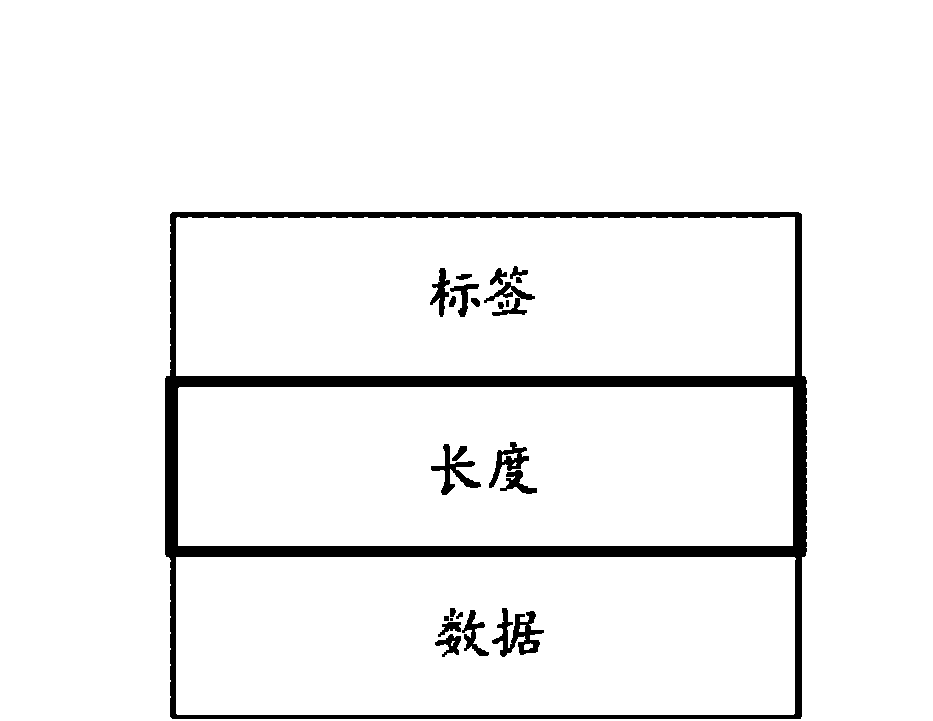

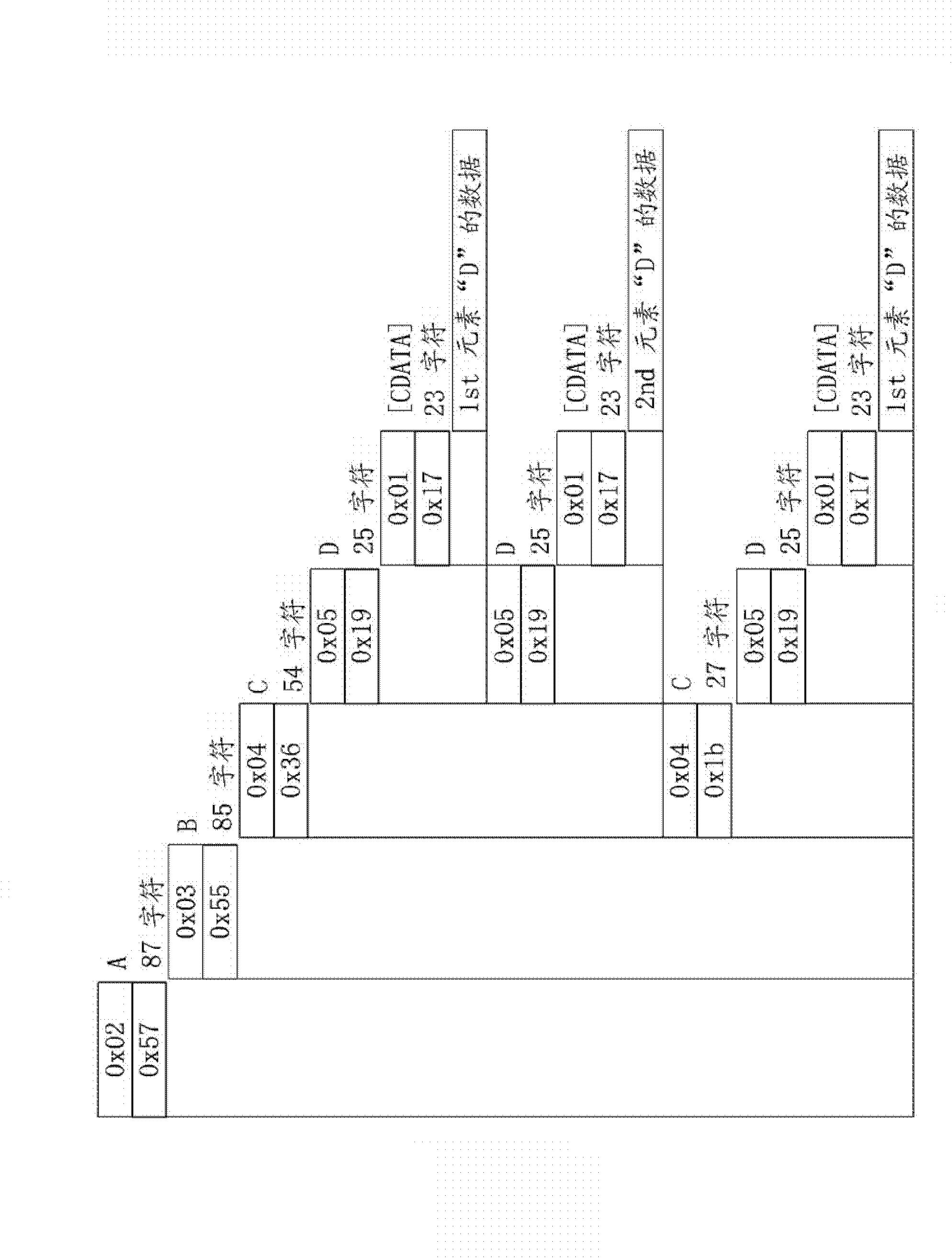

Method and apparatus for encoding and decoding xml documents using path code

InactiveCN102439589AReduce allocationIncrease compression rateCode conversionNatural language data processingXPathExtensible markup

A method and apparatus of encoding and decoding an Extensible Markup Language (XML) document using a path code is provided. A method of encoding an XML document, the method including: searching the XML document for all element tags and all attributes including character data; extracting an XPath of each of the retrieved element tags and attributes; converting the extracted XPath into a predetermined path code; and expressing an occurrence indicator of each of all element tags included in the converted XPath.

Owner:ELECTRONICS & TELECOMM RES INST

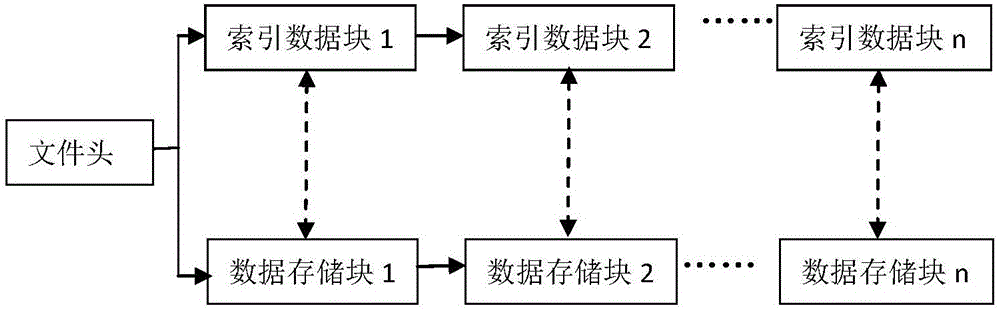

Itemized data compressing and packing method

InactiveCN106528801AEasy to debug and developImplementing Continuously Incrementing StorageComputer security arrangementsFile access structuresData compressionInode

An itemized data compressing and packing method comprises a packing process and a data reading process. The packed file includes a file header and an index chain and a data chain which are mutually independent and are connected with the file header. The index chain stores index data node information, and the data chain stores data storage node information. The index chain includes an index data block 1, an index data block 2, ..., and an index data block n (n>=2), and each index data block is corresponding to an index data node. The data chain includes a data storage block 1, a data storage block 2, ..., and a data storage block n (n>=2), and each data storage block is corresponding to a data storage node. The index data blocks are mapped to the data storage blocks one by one. The address of a next index node is stored at the end of each index data block, and the address of a next data node is stored at the end of each data storage block.

Owner:CHENGDU JUNQIAN INFORMATION TECH CO LTD

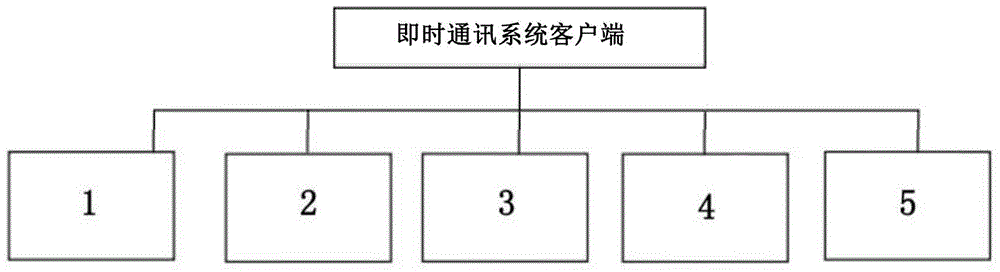

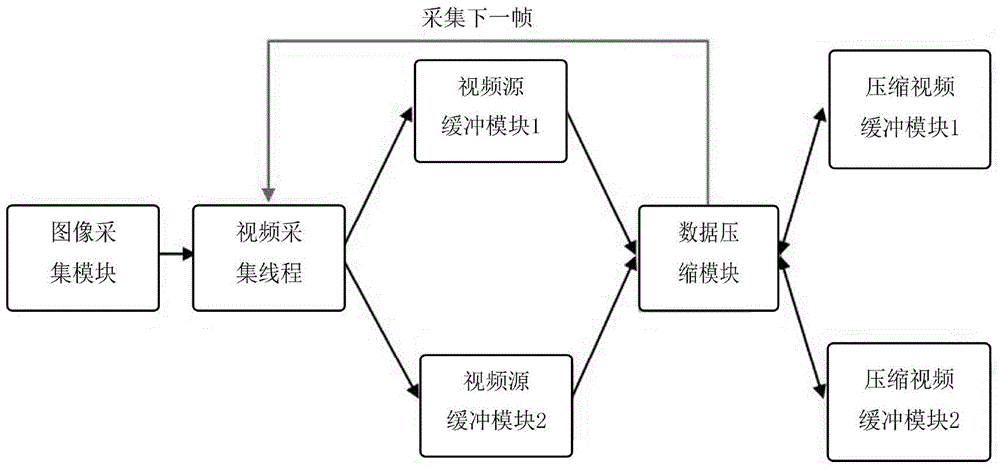

Teaching terminal based on internet instant communication technology

InactiveCN106331566AFacilitate instant interactionSimple structureTelevision conference systemsTwo-way working systemsTablet computerCodec2

A teaching terminal based on an internet instant communication technology is composed of an image acquisition module 1, a video encoder / decoder 2, an audio encoder / decoder 3, a communication protocol stack 4 and a file storage manager 5, wherein the video encoder / decoder and the audio encoder / decoder both adopt the X264 open source bases to encode, then are packaged into a data source for local calling, and then can be used by adding the corresponding configuration. The teaching terminal which realizes the interactive teaching via the internet instant communication technology satisfies the teaching demands and realizes the instant interaction and communication of the teachers and the students. Moreover, a system can realize the link sharing of the intelligent mobile terminals, such as the mobile phones, the tablet personal computers, etc., based on a mobile internet communication technology, thereby reducing the limits of a conventional remote teaching system. The teaching terminal is simple in structure, reasonable in design and stable in system, provides an instant communication channel for a remote teaching and learning companion system, saves the time, and is convenient for the instant interaction between the teachers and the students.

Owner:哈尔滨远卓科技开发有限公司

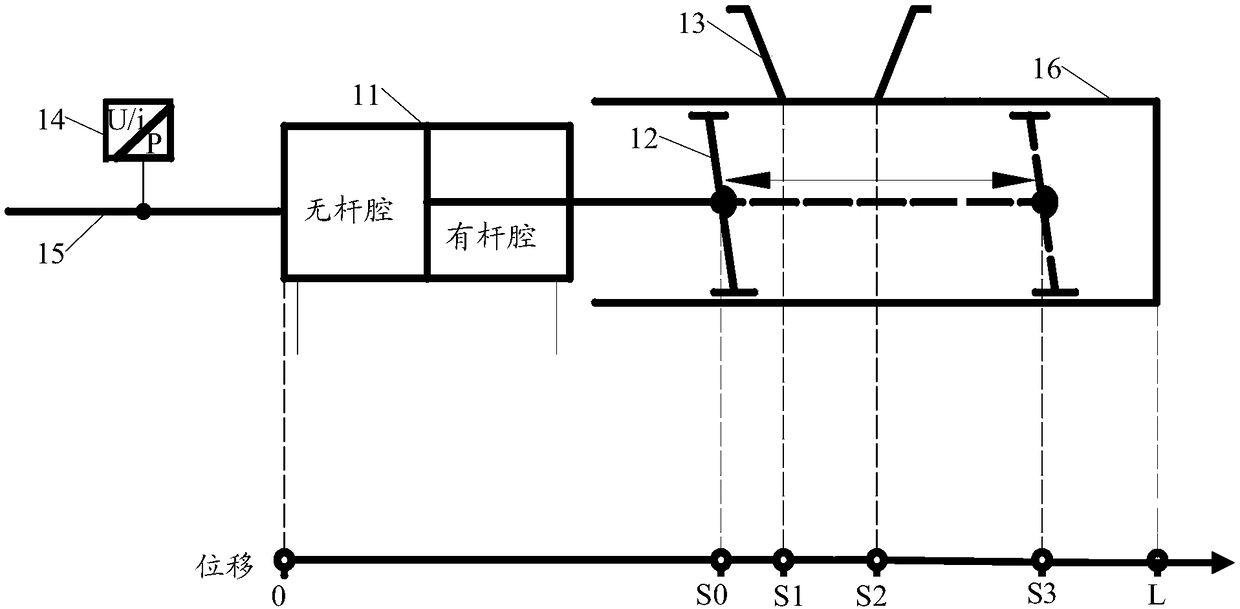

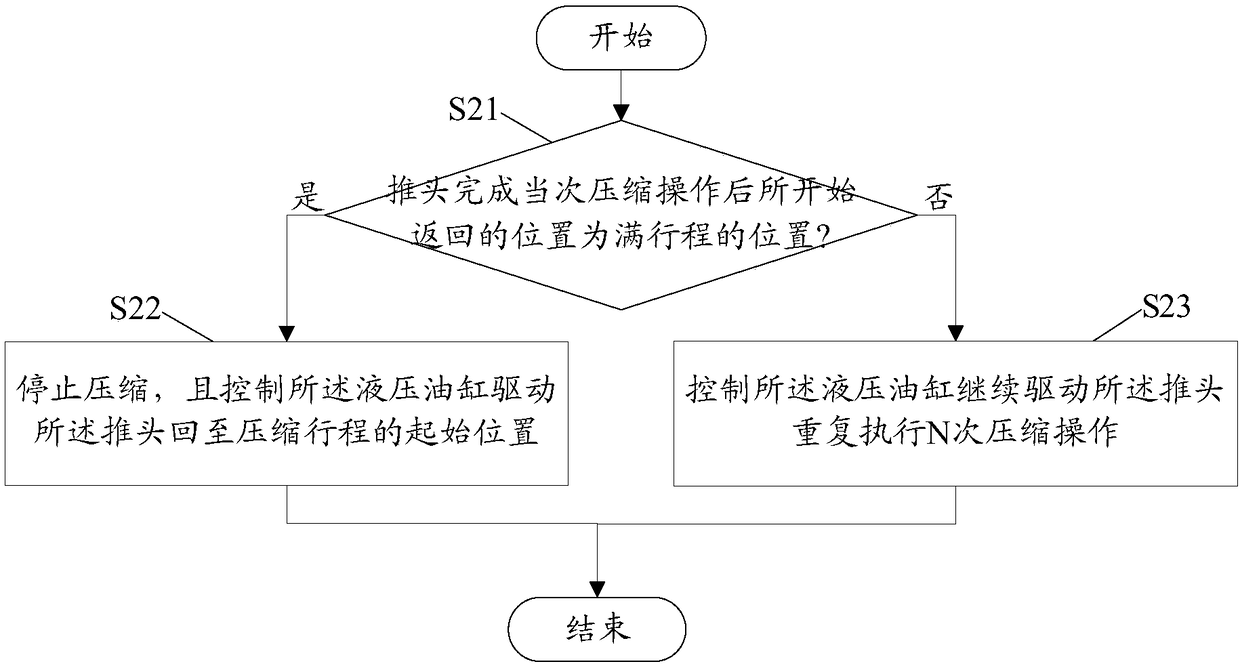

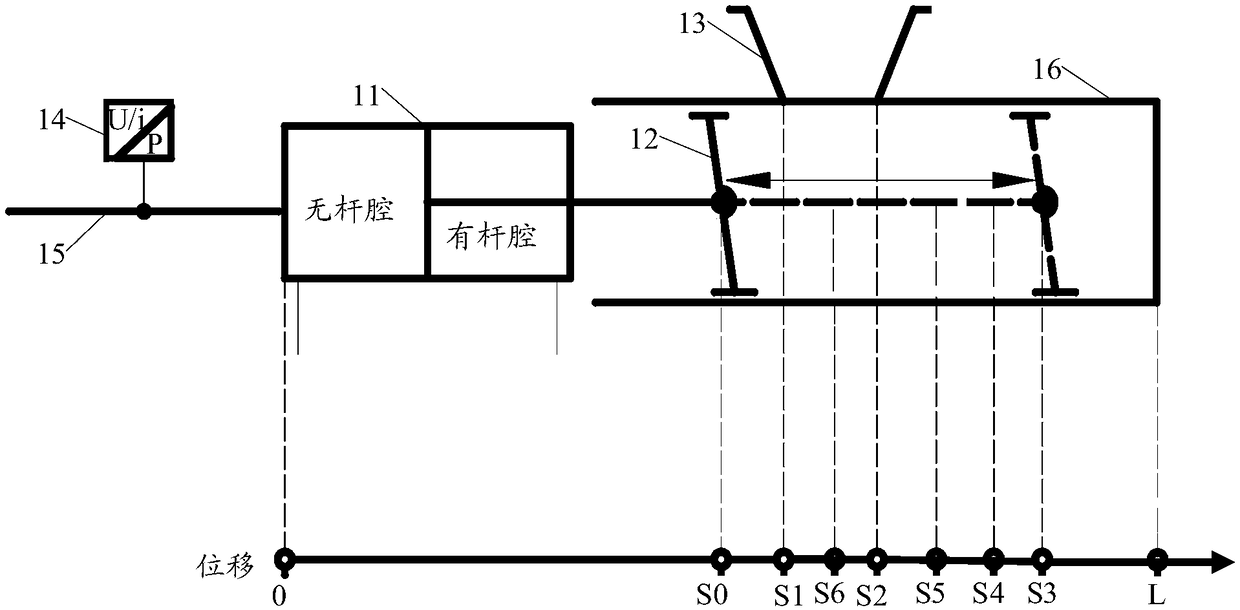

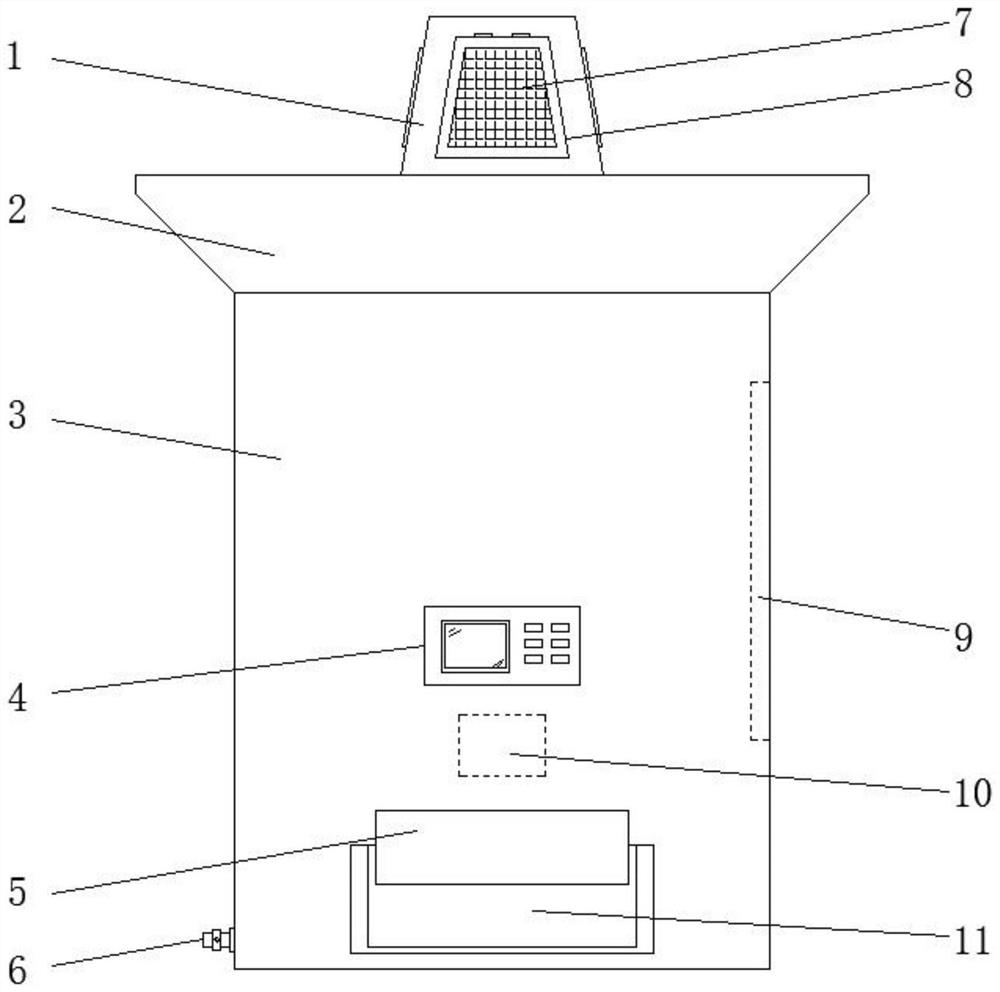

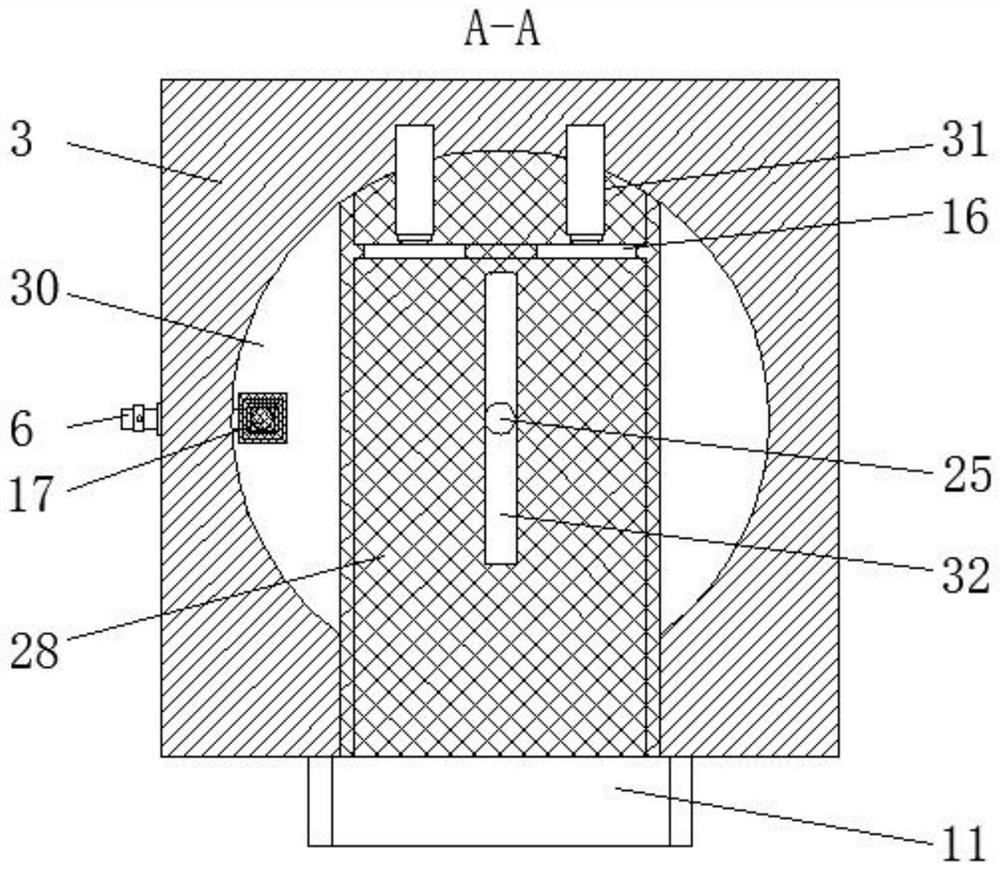

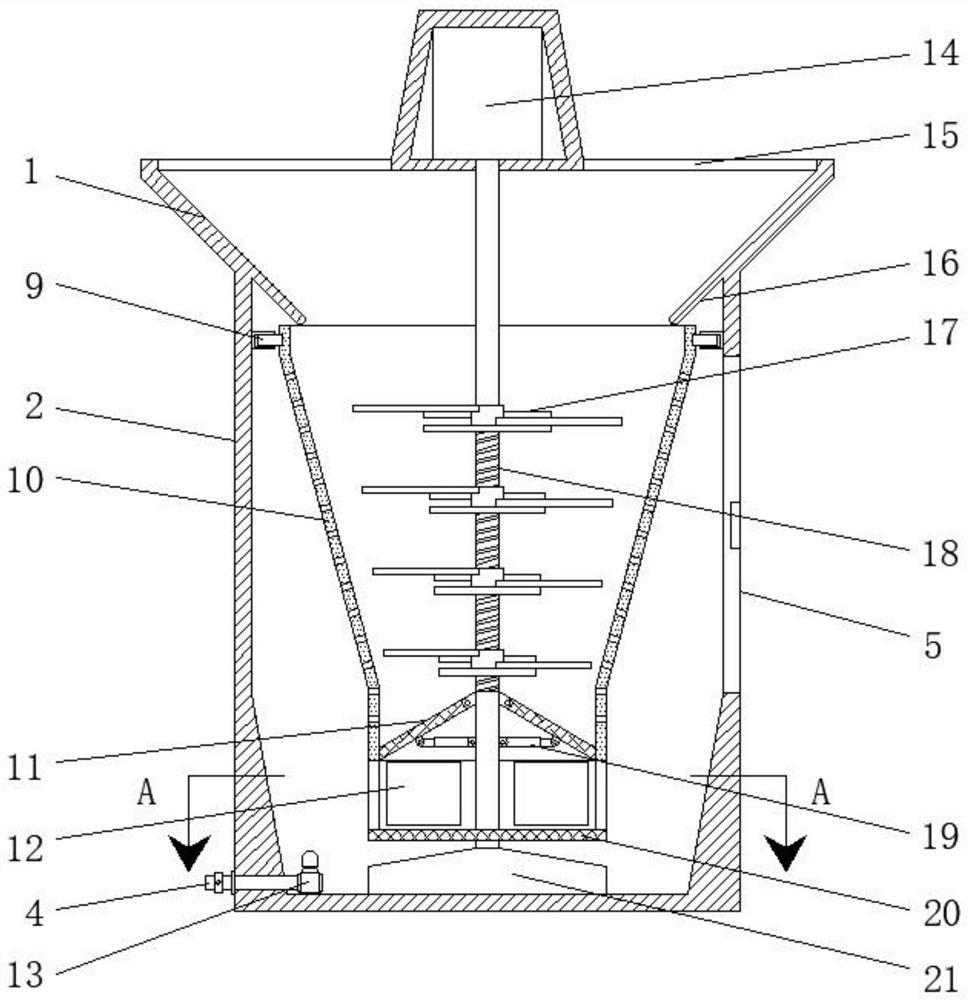

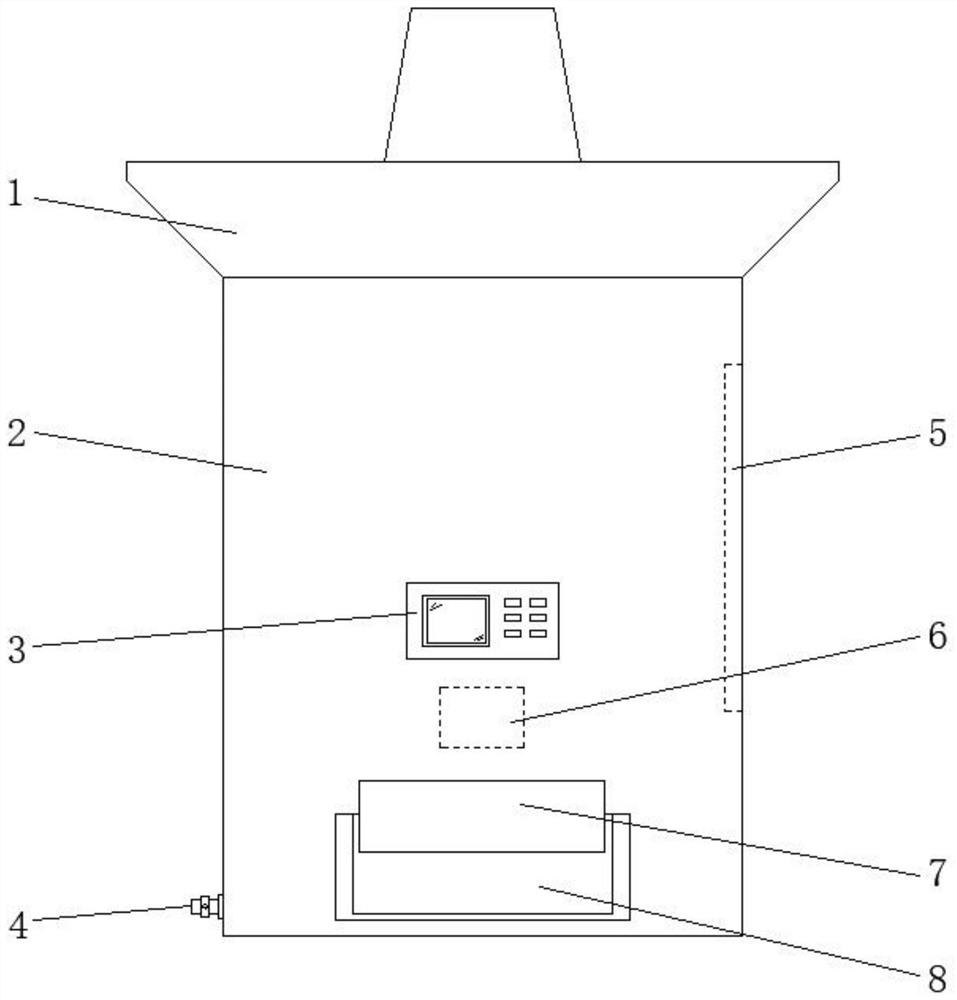

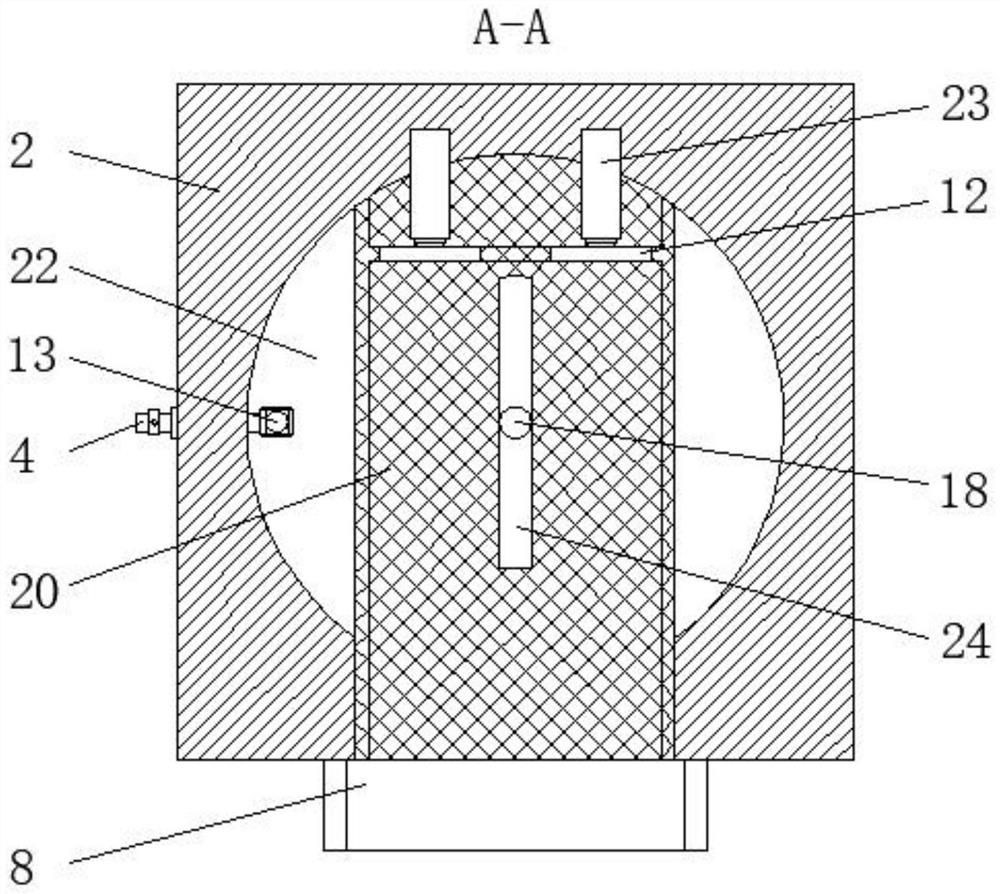

Compressor and control method and controller thereof

ActiveCN108068379AImprove energy efficiencyExtended service lifeRefuse transferringLoading/unloadingControl theoryHome position

The invention relates to a compressor and a control method and controller thereof. The compressor comprises a push head and a hydraulic oil cylinder which is suitable for driving the push head. The method includes the steps that whether the initial return position of the push head is a full-stroke position or not after the current compression operation is completed is determined, and the full-stroke position corresponds to the maximum elongation position of the push head; and when it is determined that the initial return position of the push head is the full-stroke position after the push headcompletes the current compression operation, compression is stopped, the hydraulic oil cylinder is controlled to drive the push head to return to the initial position of a compression stroke, and theinitial position corresponds to the minimum elongation position of the push head. According to the scheme, the energy efficiency of the compressor can be improved and the service life of the compressor can be prolonged.

Owner:SHANGHAI LUNLIAN ELECTROMECHANICAL EQUIP CO LTD

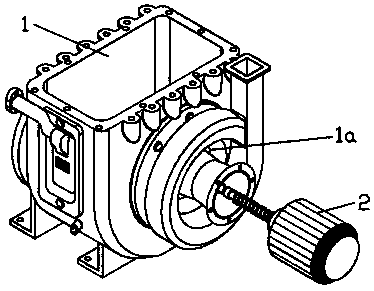

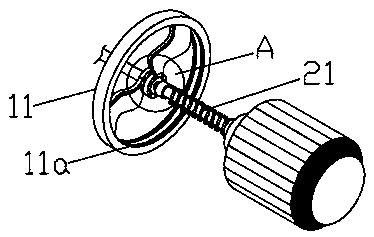

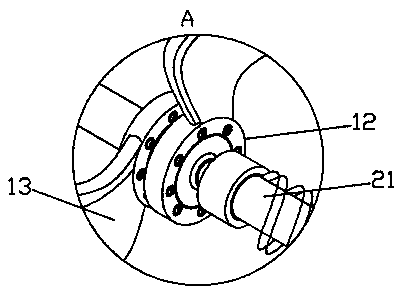

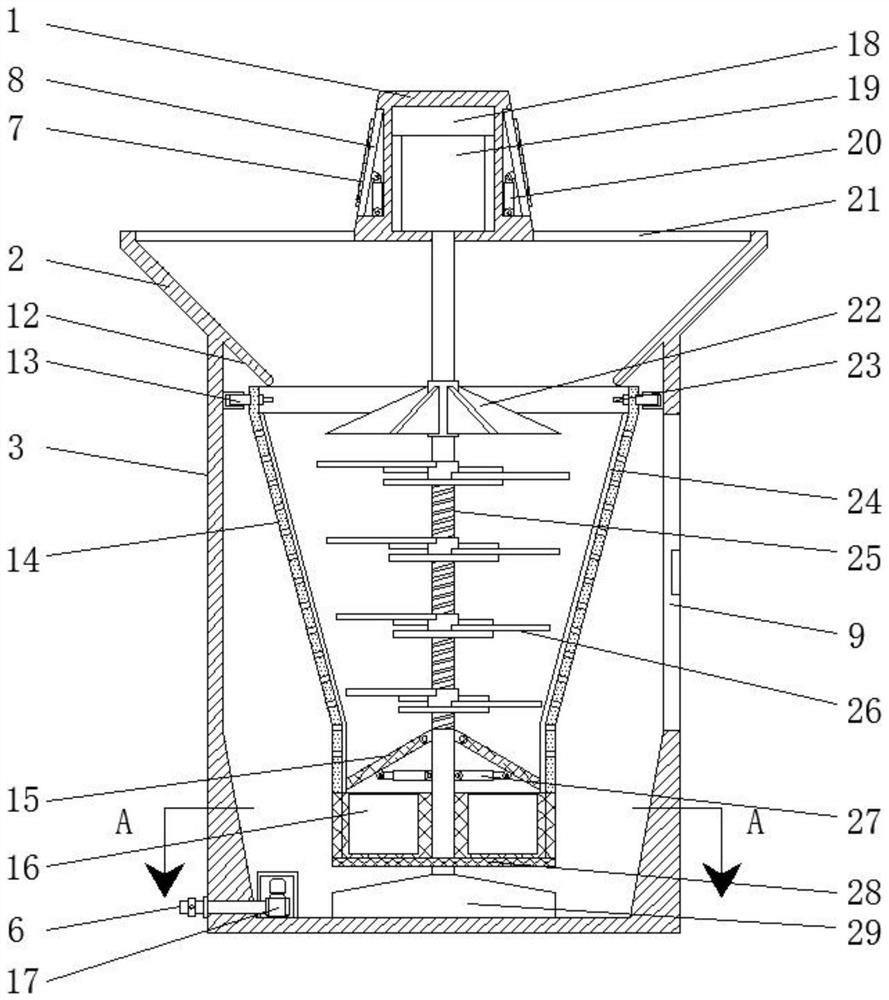

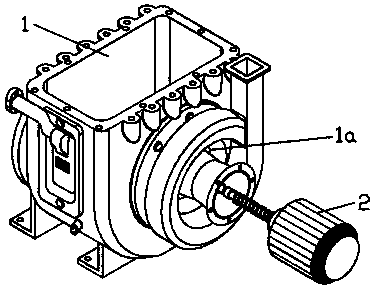

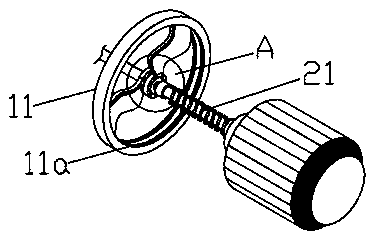

Novel axial-flow turbo-machine

ActiveCN110043451AReasonable structural designEasy to usePositive displacement pump componentsRotary piston pumpsDrive motorIndoor air

The invention discloses a novel axial-flow turbo-machine. The novel axial-flow turbo-machine comprises a shell and a driving motor, the output end of the driving motor is fixedly provided with a rotating shaft extending into the shell, a fan blade assembly is arranged on an air inlet of the shell, the fan blade assembly comprises a fixed ring plate, an annular groove is formed around the circumference of the inner wall of the fixed ring plate, an annular bearing is fixed to the rotating shaft, rotary cutting blades are fixed to the annular bearing, the bottoms of the ends, not making contact with the annular bearing, of the rotary cutting blades are fixedly provided with arc sliding blocks, the arc sliding blocks are located in the annular groove one by one, and the rotary cutting blades can do circumference motion between the annular bearing and the inner wall of the fixed ring plate. The machine is reasonable in structural design and convenient to use, the rotary cutting blades can do independent high-speed rotation, the rotary cutting rate of the air is improved, and the rate of air compression in a compression room can be improved.

Owner:JIANGSU MARITIME INST

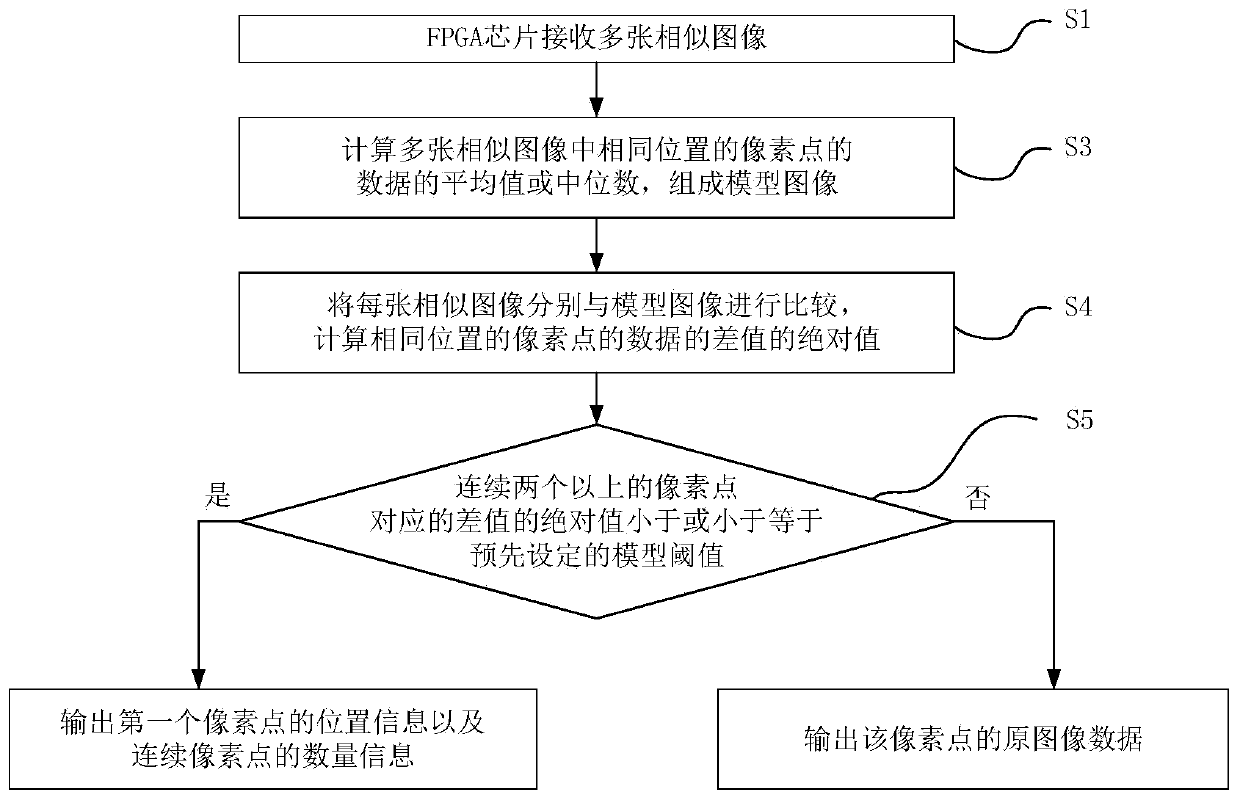

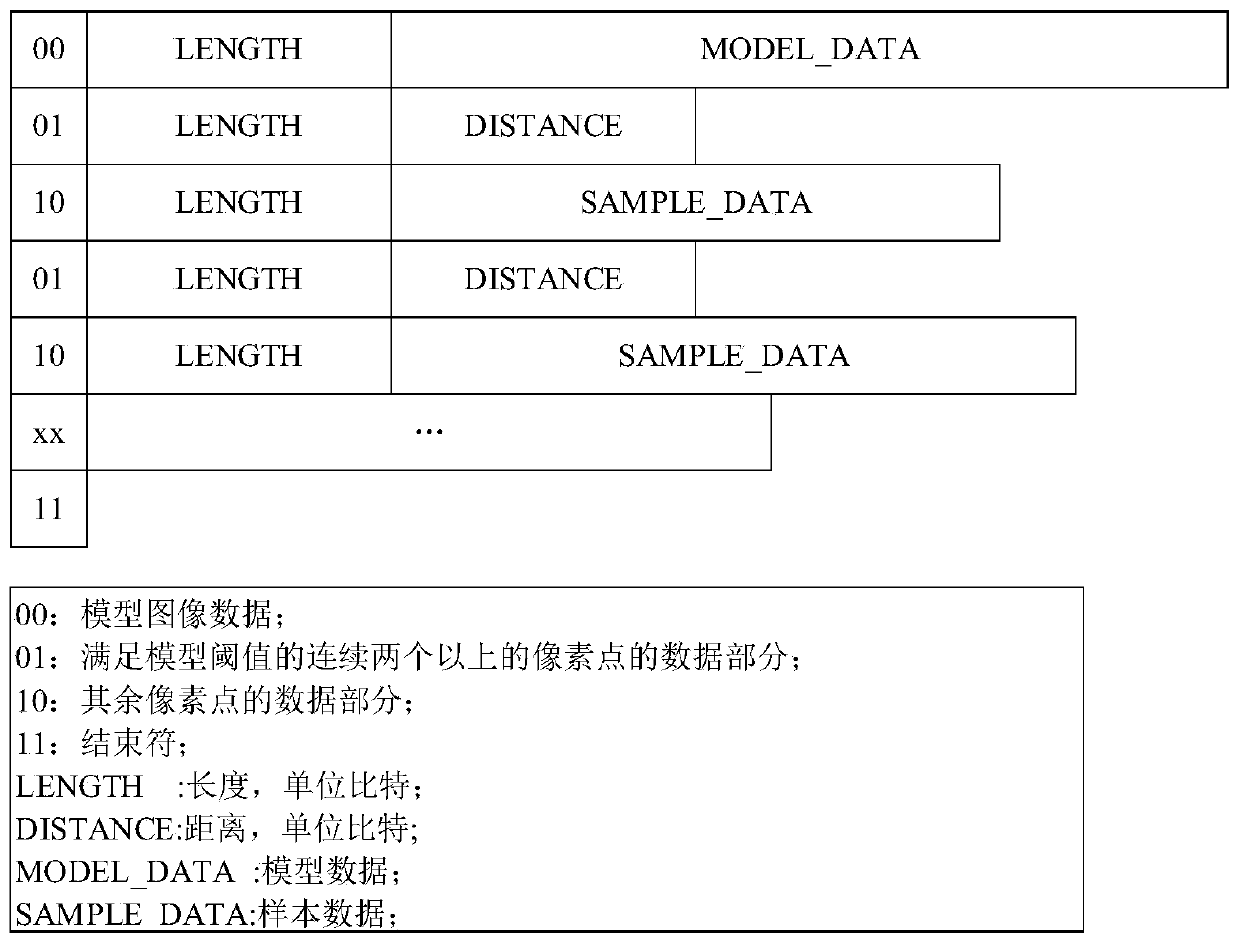

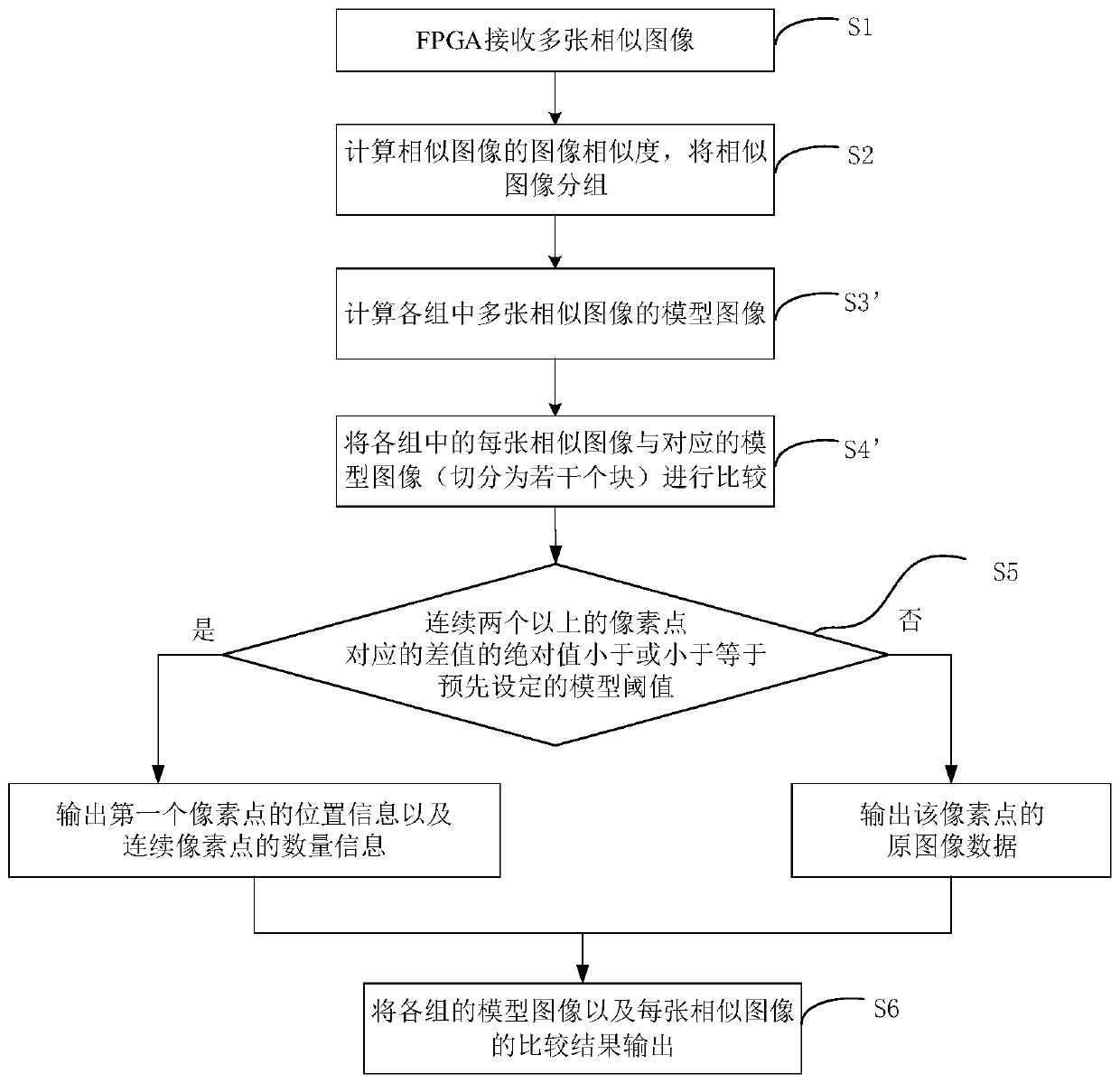

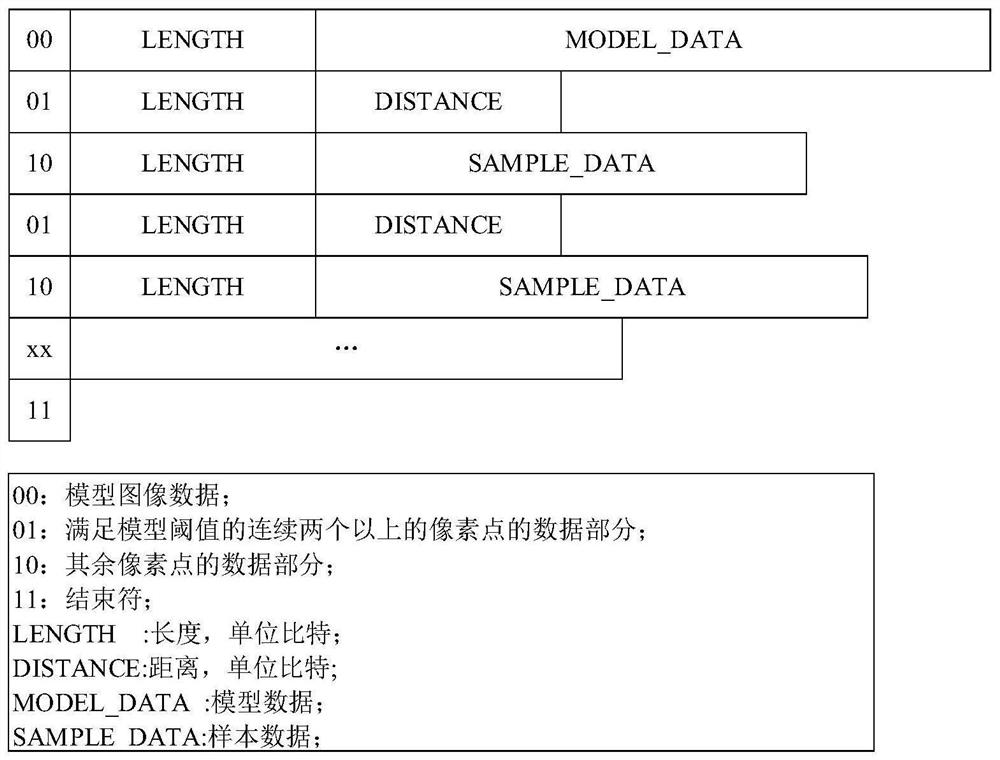

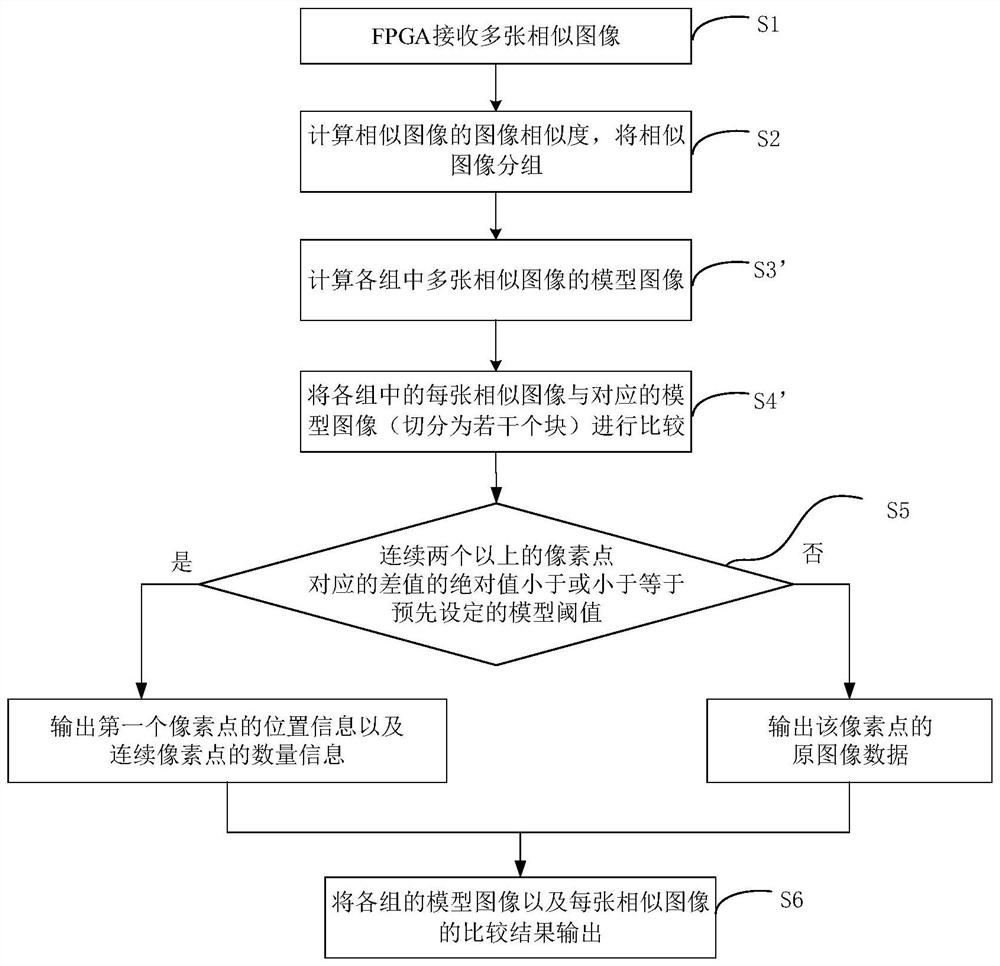

Preprocessing method and system for realizing similar image compression based on FPGA

ActiveCN111327905AImprove compression ratioImprove computing speedDigital video signal modificationImage compressionComputer graphics (images)

The invention provides a preprocessing method and system for achieving similar image compression based on an FPGA, and belongs to the technical field of image processing. Calculating the average valueor median of the data of the pixel points at the same position in the plurality of similar images to form a model image; comparing each similar image with the model image, and calculating an absolutevalue of a difference value of data of pixel points at the same position; if the absolute value of the difference value corresponding to more than two continuous pixel points is less than or equal toa preset model threshold, outputting the position information of the first pixel point and the quantity information of the continuous pixel points; and if not, outputting the original image data. Anexternal FPGA chip is used for processing, the compression rate is high, the compression time is short, a computer can be released for other processing, compressed data can be further compressed through a traditional compression method, and the image compression rate is increased.

Owner:WUHAN ZHONGYUAN HUADIAN SOFTWARE

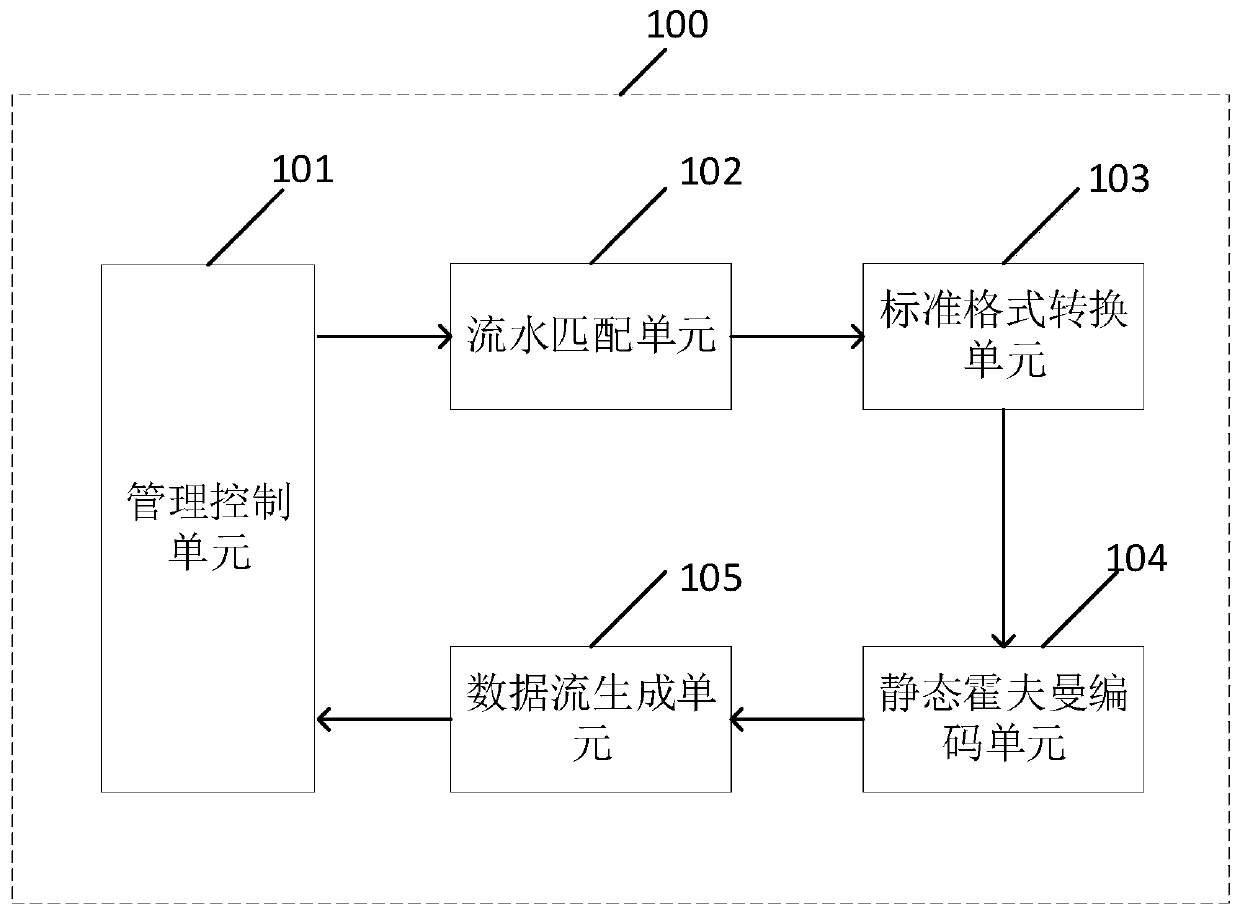

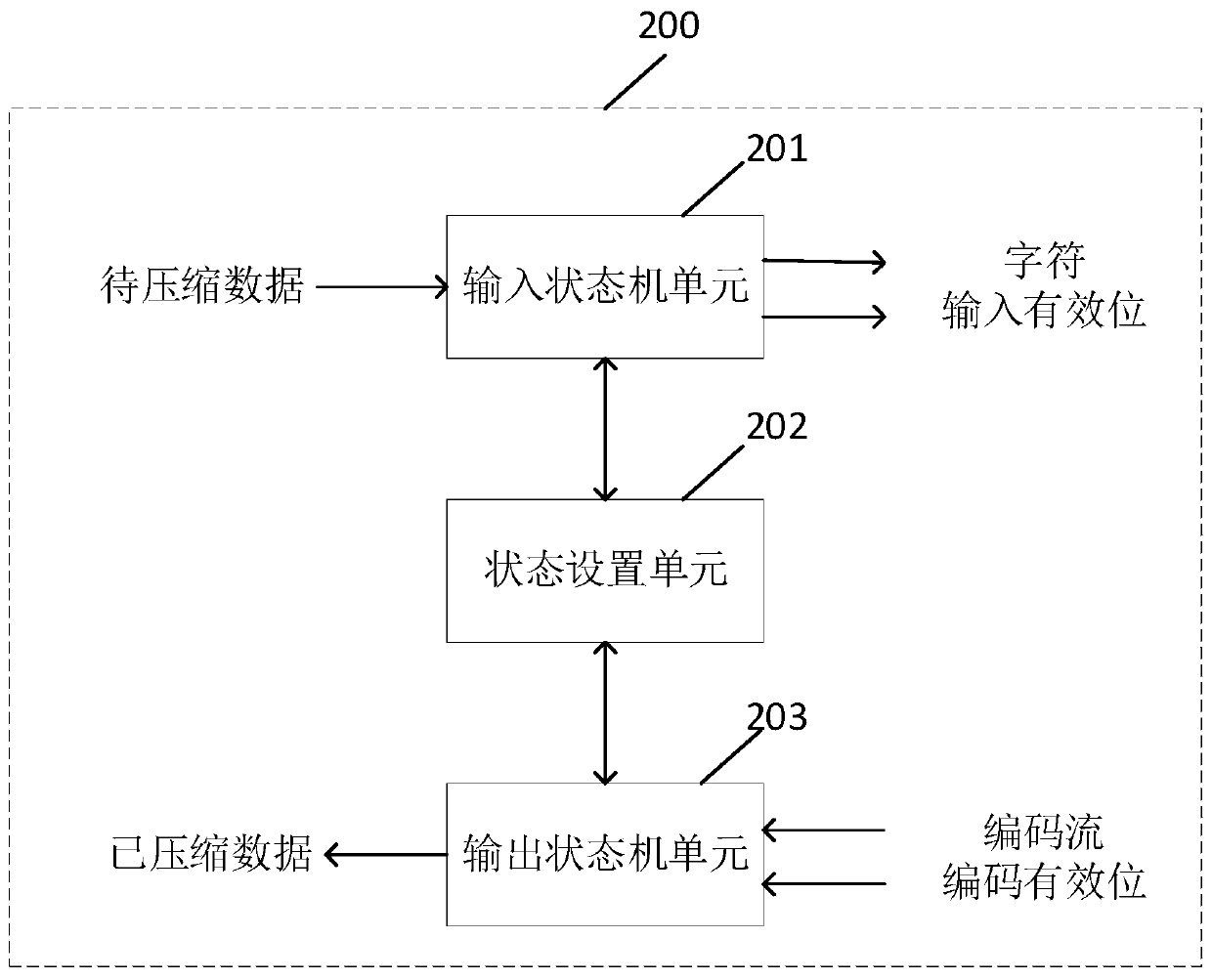

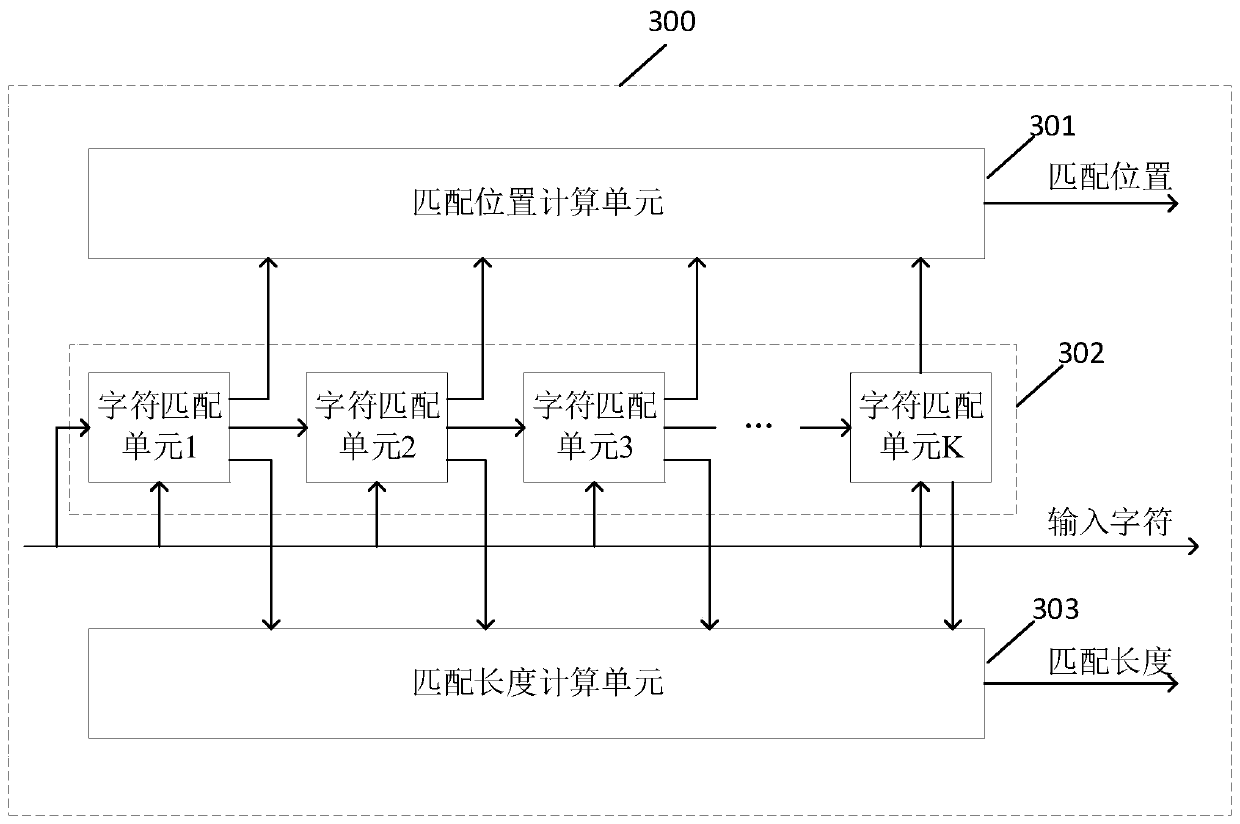

Hardware compression system and method based on pipeline mode

ActiveCN110233627AIncrease compression rateImprove matching efficiencyCode conversionData streamTechnical standard

The invention provides a hardware compression system and method based on a pipeline mode. The hardware compression system based on the pipeline mode comprises a management control unit, a pipeline matching unit, a standard format conversion unit, a static Huffman coding unit and a data stream generation unit, and the management control unit is used for controlling and coordinating data transmission of other units, obtaining to-be-compressed data and outputting compressed data. The pipeline matching unit is used for calculating the same matching position of the current input character and the previous input character, and the current input character is continuously matched with the same length. The standard format conversion unit is used for converting the input characters into a standard data format. The static Huffman coding unit is used for coding the data in the standard data format into a Huffman coding stream. The data stream generation unit is used for converting the non-fixed-length code stream into a fixed-length code stream and outputting the fixed-length code stream. According to the technical scheme provided by the embodiment of the invention, the data compression rate is improved, and the time for occupying the central processing unit and the memory resources are reduced.

Owner:SHENZHEN UNIV

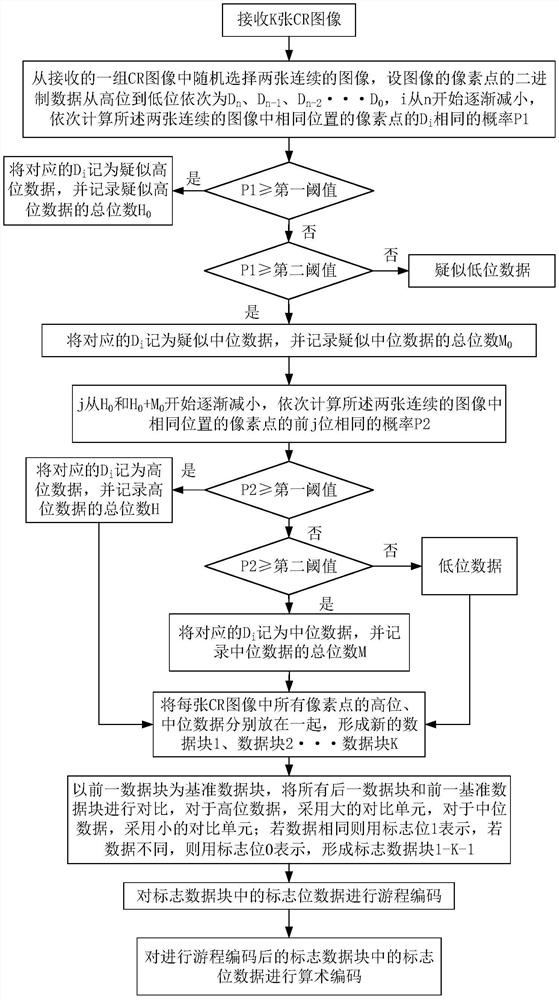

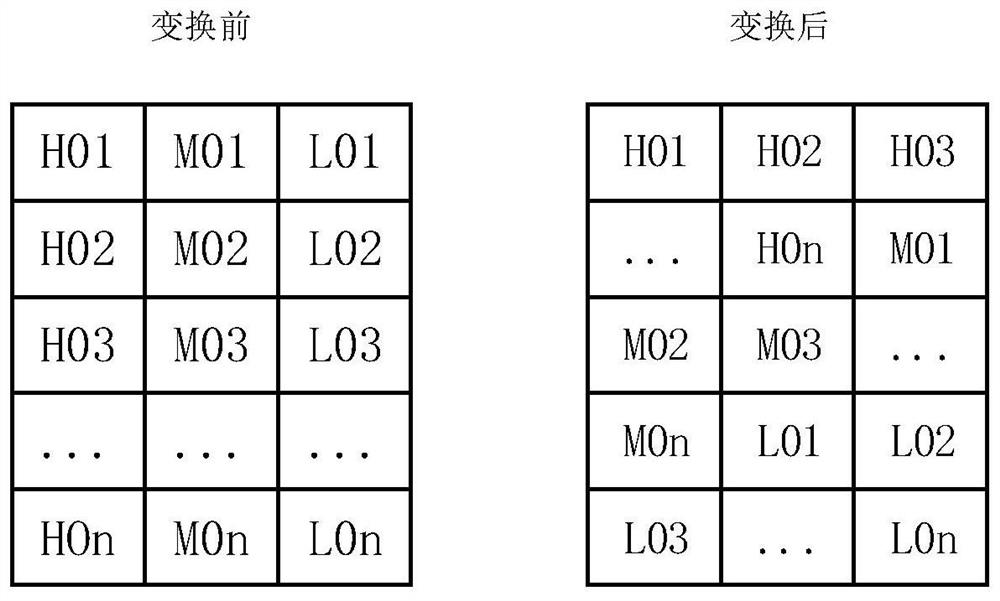

A method and system for compressing cr images with equal resolution

ActiveCN111263155BReduce the amount requiredReduce redundancyDigital video signal modificationAlgorithmImage resolution

Owner:WUHAN ZHONGYUAN HUADIAN SCI & TECH

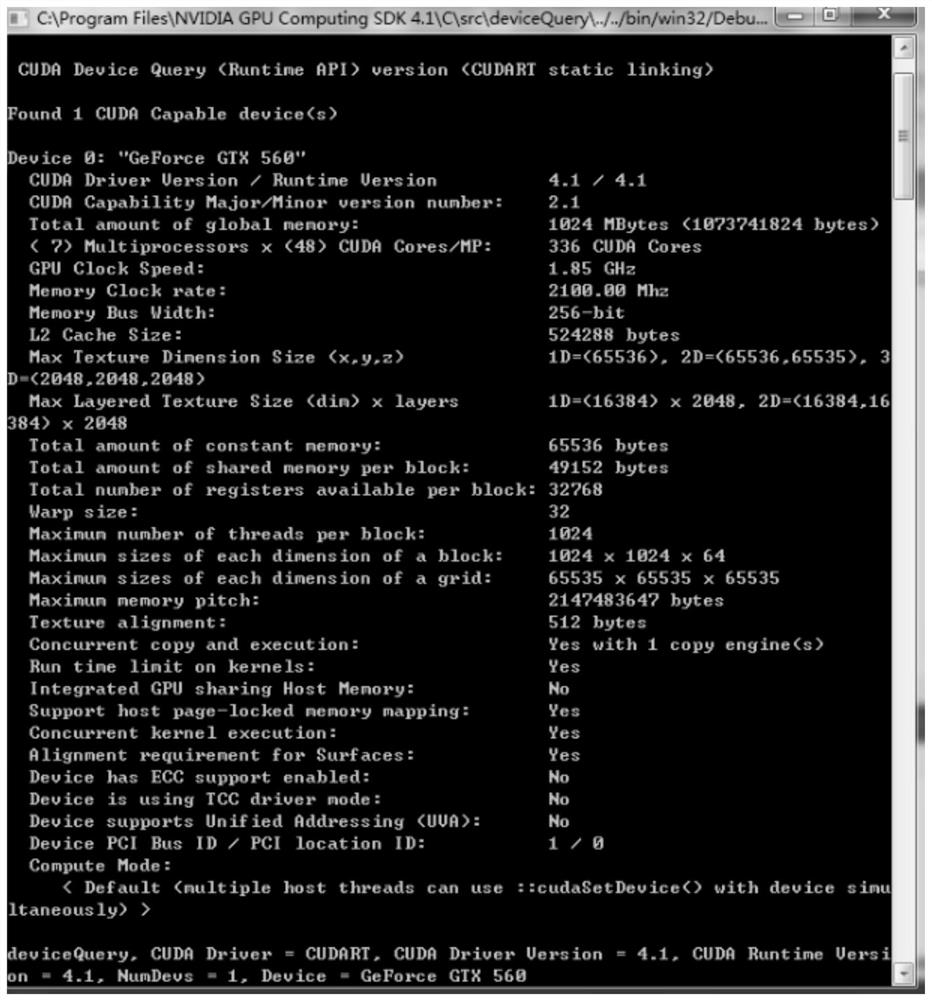

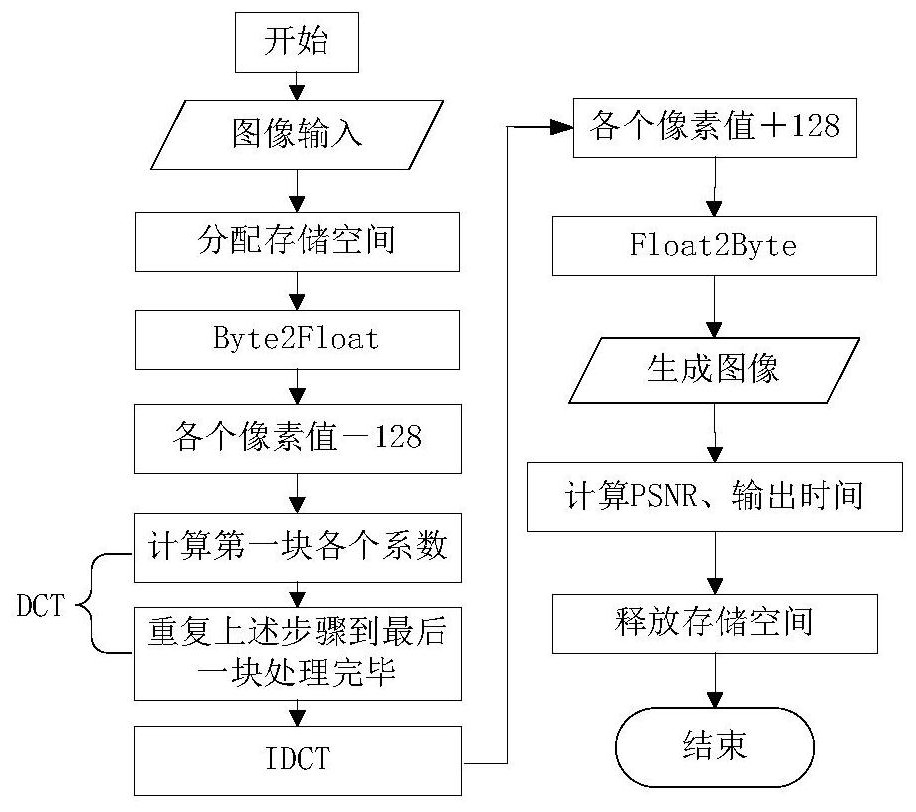

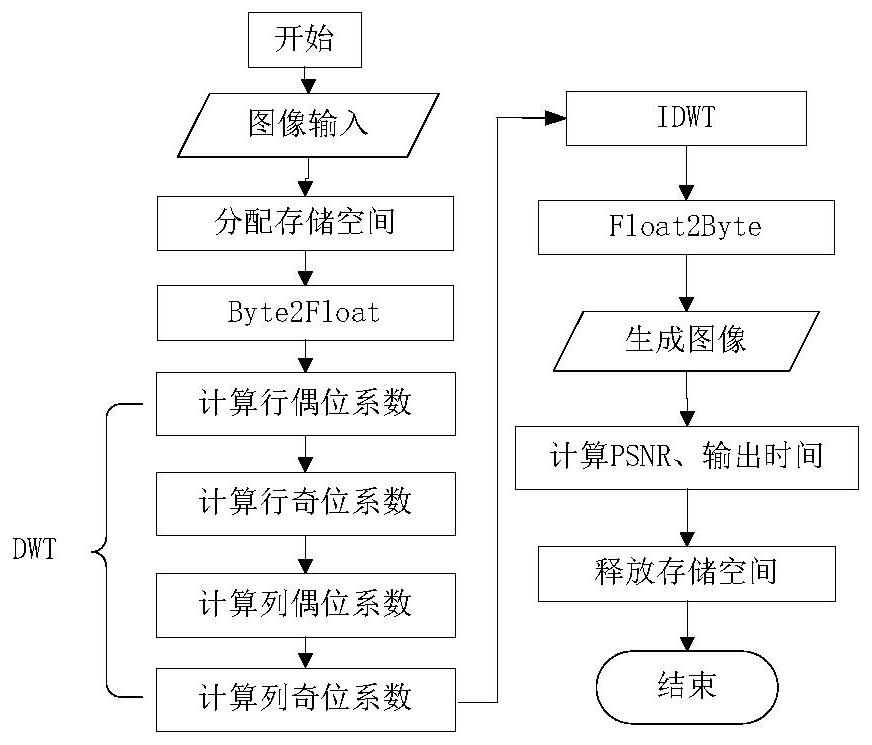

Accelerated implementation method of dct algorithm and dwt algorithm based on cuda architecture for image compression

ActiveCN109451322BParallel Execution High SpeedIncrease compression rateDigital video signal modificationImaging processingAlgorithm

The invention relates to an accelerated realization method of DCT algorithm and DWT algorithm based on CUDA framework for image compression, belonging to the field of image compression. The existing image processing methods have the problem of low compression rate. A DCT algorithm based on the DWT architecture and an accelerated implementation method of the DWT algorithm for image compression, analyzing the software system and hardware system of the CUDA platform, and building the CUDA platform based on VS2010 under the Windows operating system; the DCT algorithm and the DWT algorithm respectively Mapped to the kernel function of the two-layer CUDA execution model, the improved DCT algorithm and DWT algorithm are obtained, and the improved DCT algorithm and DWT algorithm are respectively implemented on the GPU side; the improved DCT algorithm is run on the CUDA platform. The invention is applicable to the realization of DCT algorithm and DWT algorithm on CUDA platform. Parallel execution of the calculation process can obtain a compression ratio of several tens of times relative to the CPU, thereby effectively improving the compression rate of digital image compression.

Owner:BEIJING INST OF AEROSPACE CONTROL DEVICES +1

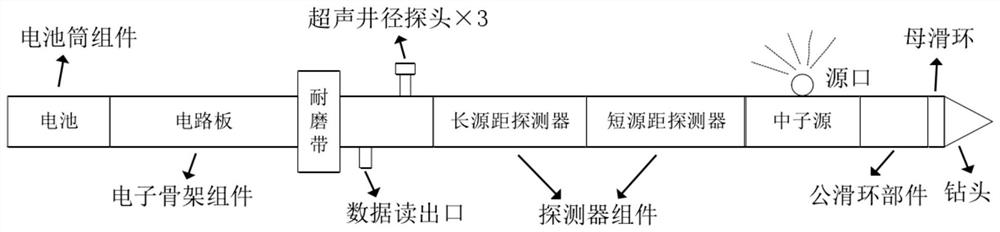

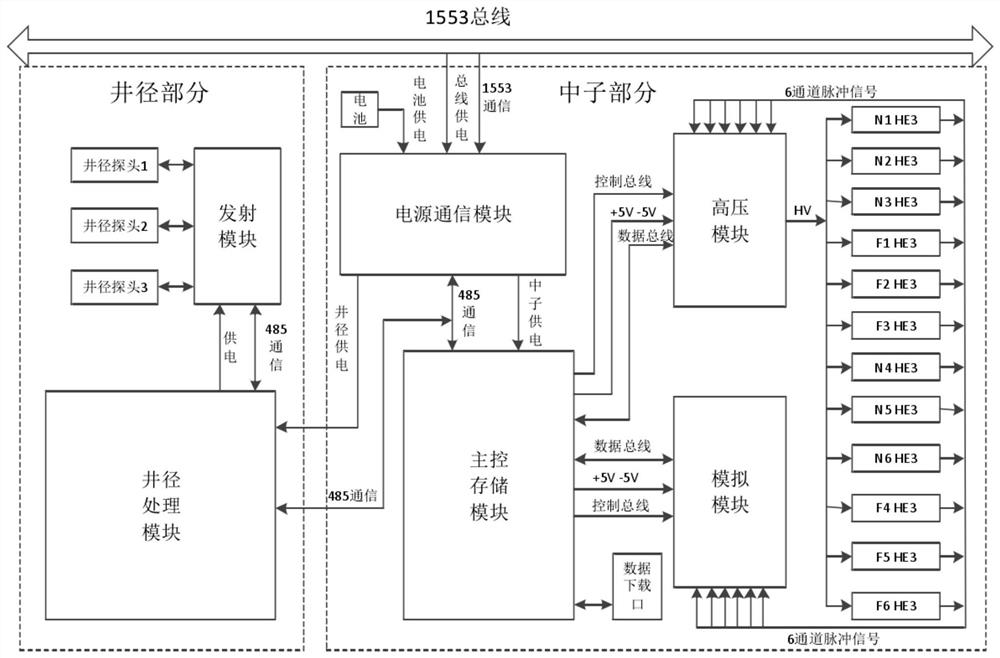

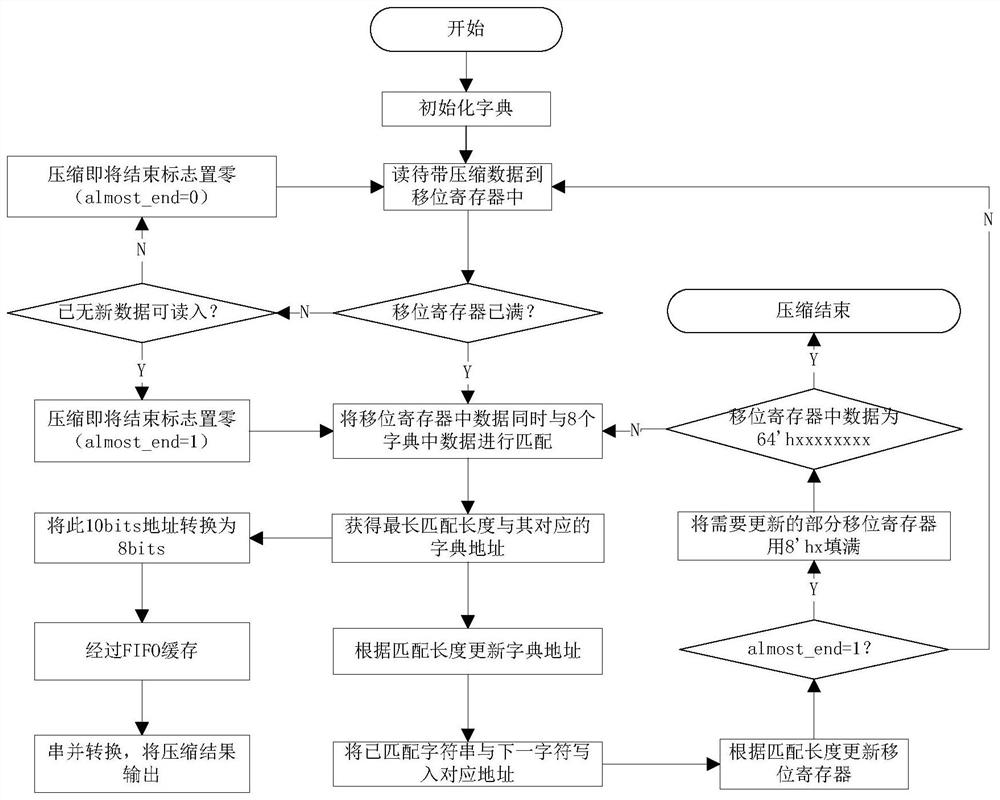

Downhole high-speed real-time compression method of neutron logging tool while drilling based on small dictionary

ActiveCN108494409BReduce storage pressureSave spaceSurveyConstructionsShift registerParallel computing

The invention discloses a high-speed real-time downhole compression method of a neutron logging tool while drilling based on a small dictionary. The dictionary is initialized when the power is turned on, and then the original downhole data is cached; the compression is started after the 8-byte shift register is full. , 8-byte data is searched in 8 small dictionaries at the same time, and the matching length and matching address can be output in one clock cycle. If there are multiple dictionaries matching at the same time, select the 10bits address corresponding to the dictionary with the longest matching length as compression code output; convert the 10bits compressed code into 8bits data and then serially convert and store it in Flash; at the same time update the address of the small dictionary and write the matched character string and the next character into this address; update the shift register; and so on until Compression ends.

Owner:UNIV OF ELECTRONICS SCI & TECH OF CHINA

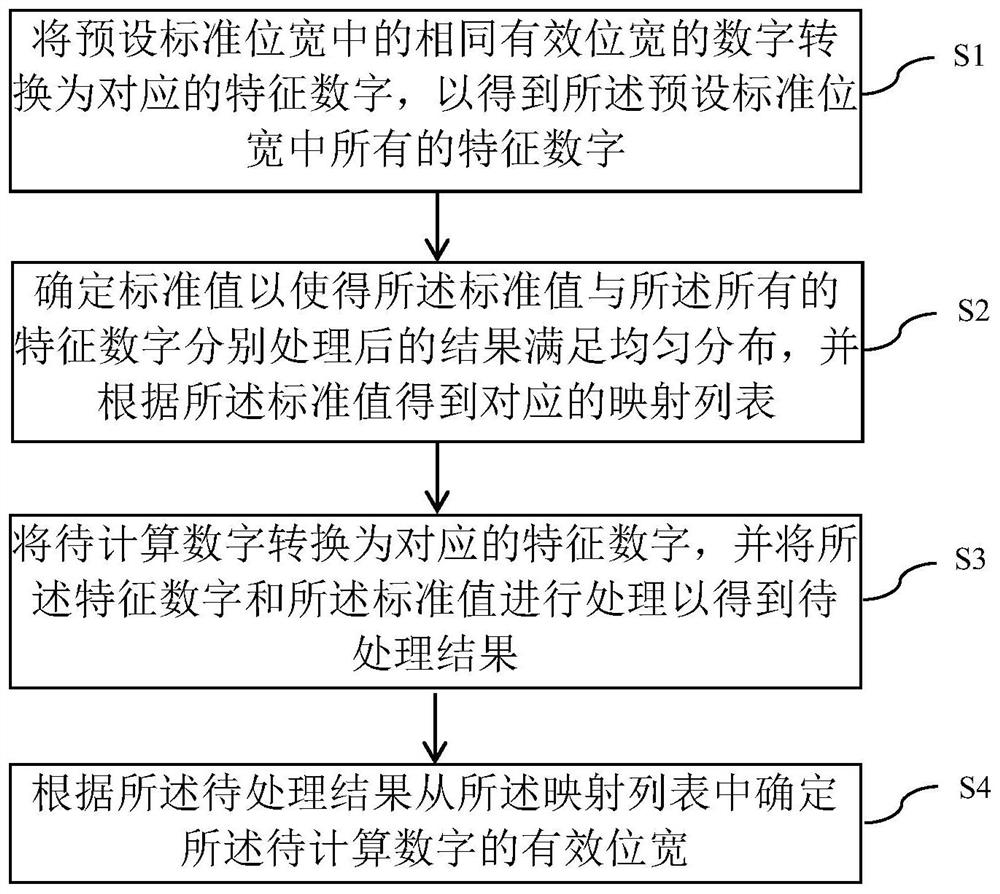

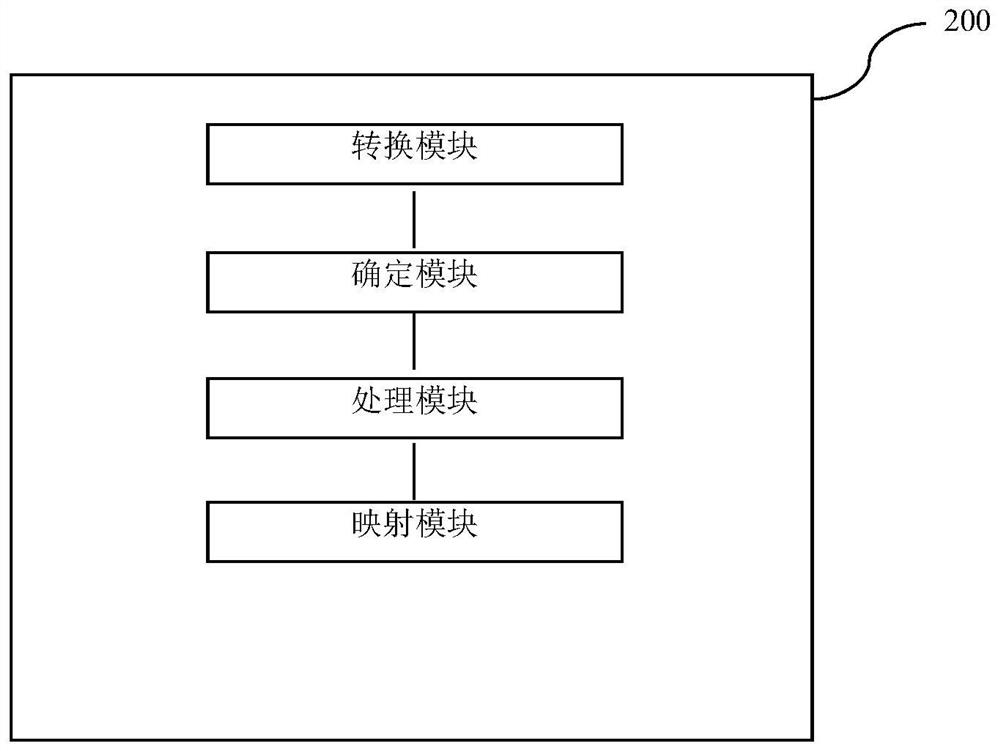

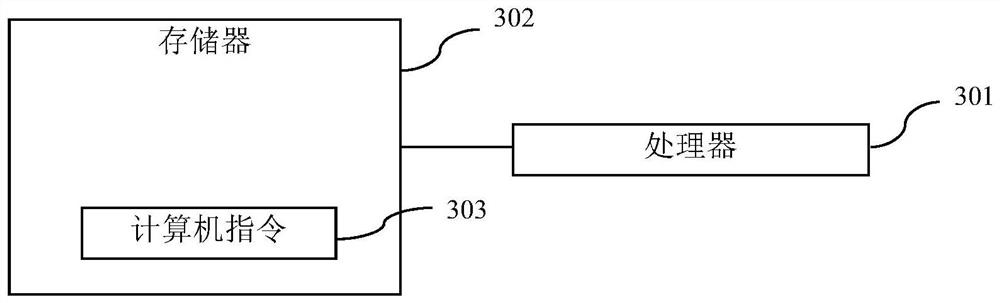

Method, system and equipment for calculating digital effective bit width and storage medium

PendingCN114268322ABit wide fastQuickly get the bit widthCode conversionAlgorithmHardware implementations

The invention provides a method, system and device for calculating the effective bit width of digits and a storage medium, and the method comprises the steps: converting the digits with the same effective bit width in a preset standard bit width into corresponding feature digits, so as to obtain all feature digits in the preset standard bit width; determining a standard value so as to enable the standard value and a result obtained by processing all the feature numbers to meet uniform distribution, and obtaining a corresponding mapping list according to the standard value; converting a to-be-calculated number into a corresponding feature number, and processing the feature number and the standard value to obtain a to-be-processed result; and determining the effective bit width of the number to be calculated from the mapping list according to the result to be processed. Compared with a current bit-by-bit comparison method, the method has the advantages that the calculation times can be greatly reduced, and hardware implementation is easy; not only can the effective bit width of the number be quickly obtained, but also the solving time is fixed.

Owner:SHANDONG YUNHAI GUOCHUANG CLOUD COMPUTING EQUIP IND INNOVATION CENT CO LTD

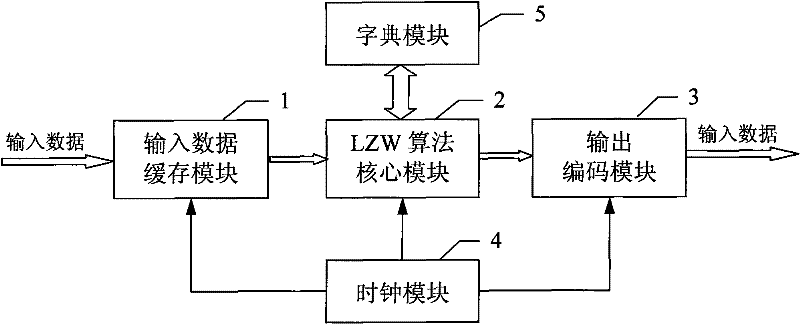

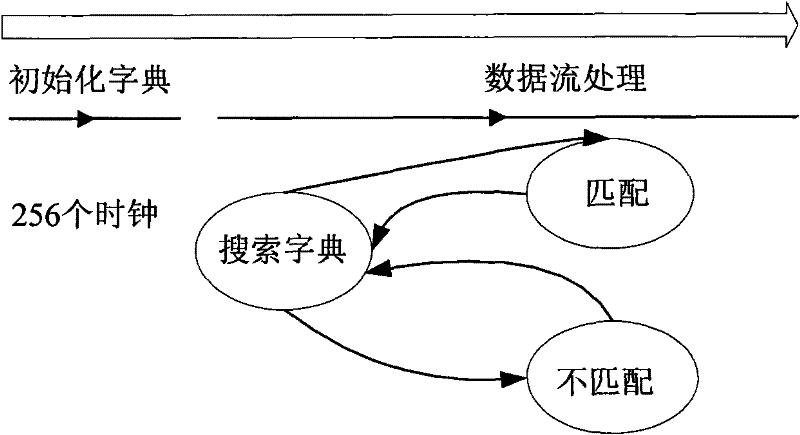

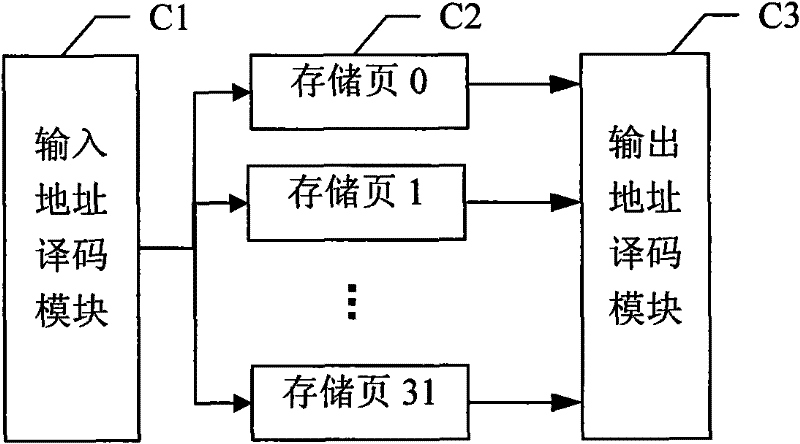

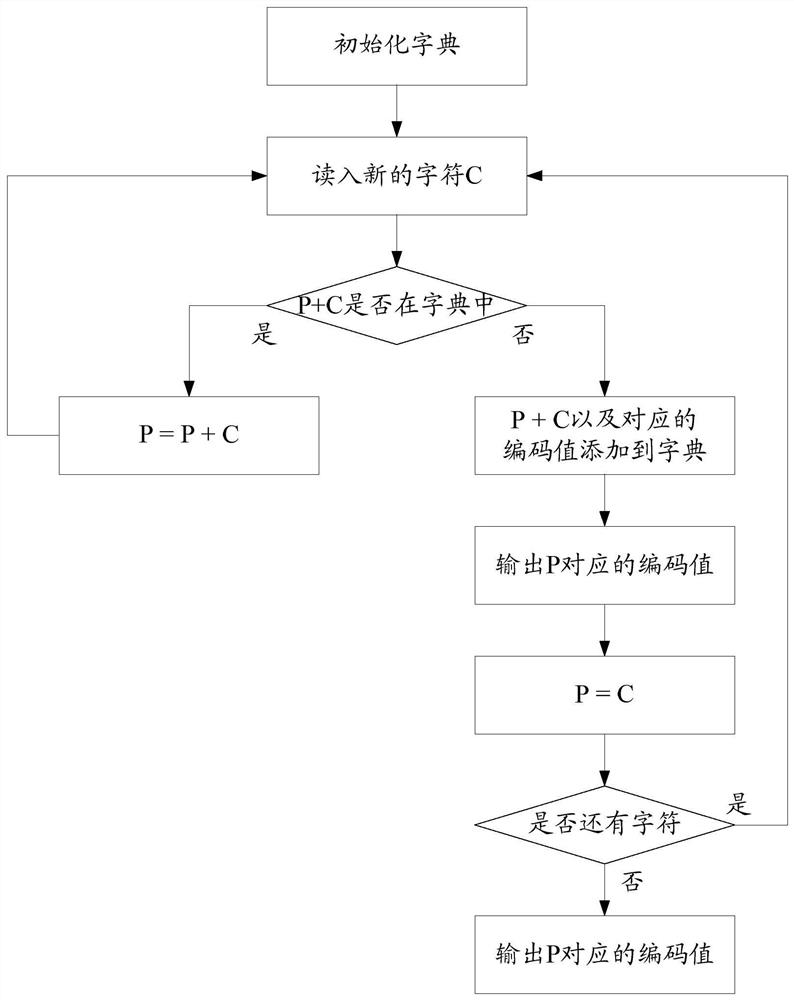

High-speed lossless data compression system based on content addressable memory

InactiveCN101572552BSolve the speed problemIncrease compression rateMemory adressing/allocation/relocationCode conversionData compressionComputer module

The invention provides a high-speed lossless data compression system based on a content addressable memory, which relates to the technical field of the data compression of a hardware system. The invention solves the problems of low compression rate, heavy consumption of limited RAM resources in a hardware chip, indefinite search cycle, and the like, and solves the problem that address conflict exists in the dictionary searching which is realized by adopting a hash table address module. The invention comprises a clock module, an input data buffer module, a dictionary module, an LZW algorithm kernel module and an output encoding module, wherein, the dictionary module is constructed by the CAM inside an FPGA, the bit width of the CAM is 17, and the depth of the CAM is 512; the address of thememory in the CAM corresponds to the code of the LZW algorithm in the LZW algorithm kernel module, and the memory comprises a comparator and a trigger; the trigger is used for storing data, and the comparator is used for comparing input data with the data in the trigger and outputting a matching signal. The data compression system realizes the high-speed lossless data compression based on the FPGAand enlarges the range of application.

Owner:HARBIN INST OF TECH

Recording data processing method and device

ActiveCN107102220BReduce data volumeWithout breaking integrityElectrical testingCode conversionPower qualityComputer science

The invention discloses a recorded waveform data processing method and a recorded waveform data processing device, wherein the recorded waveform data processing method comprises the steps of acquiring the number of periodical sampling points of recorded waveform data, wherein the recorded waveform data are electric energy quality monitoring data; and performing inter-cycle differential calculation on the sampling point data at the same position between the cycles for obtaining differential data, so that advantages of low subsequent processing data volume, high processing speed in compression or transmission, and the like are realized. The recorded waveform data processing method and the recorded waveform data processing device can reduce data volume of to-be-compressed data or to-be-transmitted data, thereby reducing compression calculation amount and data volume after compression, and improving compression rate. Furthermore the recorded waveform data processing method and the recorded waveform data processing device can relatively effectively reduce storage and / or transmission load of the mass recorded waveform data of an electric energy quality monitoring terminal.

Owner:GLOBAL ENERGY INTERCONNECTION RES INST CO LTD +1

Method, device and system for data transmission

ActiveCN109756536BIncrease compression rateAvoid consumptionTransmissionComputer hardwareData compression

The invention discloses a data transmission method. The method comprises the following steps: dividing data to be transmitted into data blocks with preset data block sizes; and sequentially sending the target data block message obtained by compressing and packaging each data block to a receiving end. Therefore, the data can be partitioned before data transmission, compressed and packaged one by one, and then sent to a receiver one by one, so that the one-time calculation amount and transmission amount are effectively reduced, consumption of a large number of calculation resources is avoided, and the transmission speed can be effectively increased. Meanwhile, each data block can be judged, if the current data block does not need to be compressed, computing resources are not wasted to compress the current data block, the data compression rate is further increased, and therefore the data transmission rate is increased. The embodiment of the invention further provides a data transmission device and system, and the above technical effects can also be achieved.

Owner:ZHUZHOU CSR TIMES ELECTRIC CO LTD

An energy-saving landfill leachate treatment device

ActiveCN110293113BEasy to stretchEasy to use with power supplyWaste processingTransportation and packagingEnvironmental engineeringSolar battery

The invention discloses an energy-saving garbage leachate treatment device, which comprises a driving seat, a feed end, a treatment box, a garbage discharge port and a liquid separation cylinder. One side of the treatment box is hinged with an inspection door, and the other side of the treatment box is The bottom of the side is equipped with a liquid outlet pipe, and the top of the treatment box is connected with a feed end, and the center of the top of the feed end is connected with a drive seat, and the top of the feed end on both sides of the drive seat is provided with a feed port. The outer side of the tank is uniformly hinged with an adjustment plate, and solar panels are installed on the adjustment plates. A liquid guide seat is installed at the center of the inner bottom of the treatment box, and a blanking seat is installed inside the treatment box above the liquid guide seat. A liquid separation cylinder is arranged inside the treatment box above the unloading seat. The invention can effectively crush the garbage, and carry out bag-breaking treatment on the bagged garbage, avoid leachate remaining in the garbage, fully separate the garbage and the leachate, improve the separation rate of the garbage and the leachate, and increase the compression rate of the garbage.

Owner:ANHUI LANDING ENVIRONMENTAL PROTECTION ENERGY TECH

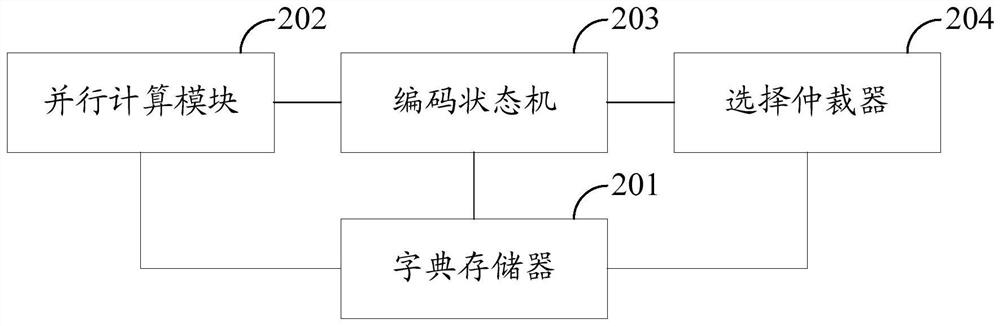

Data compression system and method

ActiveCN113630123AIncrease compression rateImprove matching efficiencyCode conversionEnergy efficient computingConcurrent computationTheoretical computer science

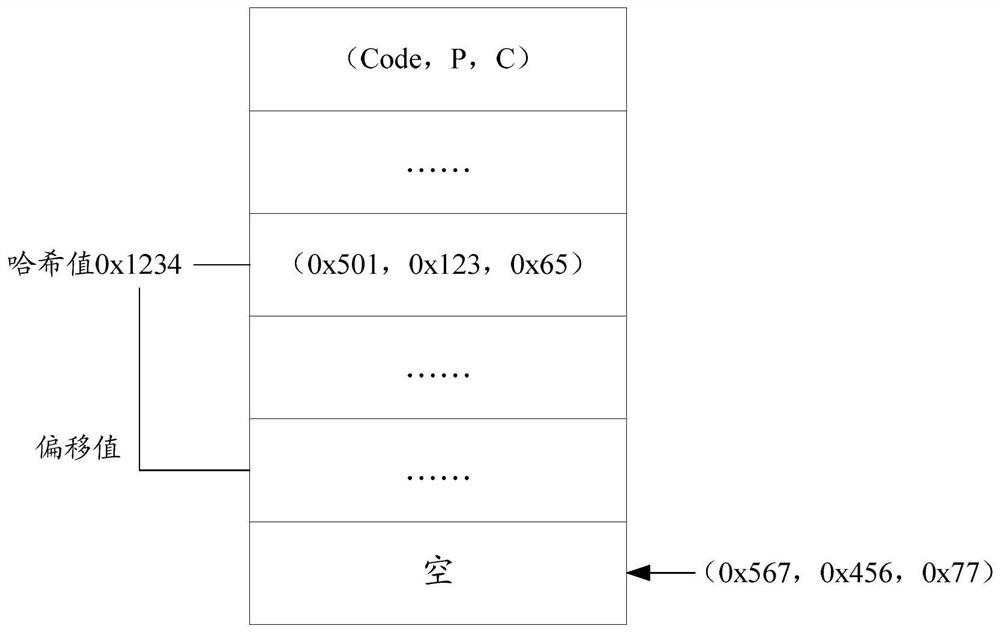

The embodiment of the invention discloses a data compression system and method which are used for improving the compression rate of an LZW compression algorithm. The system comprises: a dictionary memory for storing a first number of sub-dictionaries, each sub-dictionary comprising a second number of storage areas, each storage area corresponding to a hash value; a parallel computing module used for acquiring to-be-compressed data, obtaining a current character and a prefix character string corresponding to the to-be-compressed data, and performing XOR calculation on the current character and the prefix character string according to bits to obtain a first hash value, and adding the offset to the first hash value to obtain a second hash value, and finally obtaining index contents from the storage areas corresponding to the first hash value and the second hash value in parallel; a coding state machine, which is used for determining the matching condition of the current character, the prefix character string and the index content; a selection arbiter which is used for determining the storage area to be written and the content written into the storage area to be written according to the matching condition, or determining the output content according to the matching condition.

Owner:SHANDONG YUNHAI GUOCHUANG CLOUD COMPUTING EQUIP IND INNOVATION CENT CO LTD

Preprocessing method and system for similar image compression based on FPGA

ActiveCN111327905BIncrease the compression ratioImprove computing speedDigital video signal modificationImaging processingComputer graphics (images)

The present invention provides a preprocessing method and system for realizing similar image compression based on FPGA, which belongs to the technical field of image processing. The method of the present invention receives multiple similar images by using an external FPGA chip; calculates pixels at the same position in multiple similar images The average or median of the point data constitutes a model image; each similar image is compared with the model image respectively, and the absolute value of the difference between the data of the pixel points at the same position is calculated; if more than two consecutive If the absolute value of the difference corresponding to the pixel is less than or equal to the preset model threshold, the position information of the first pixel and the number of consecutive pixels are output; otherwise, the original image data is output. The invention utilizes an external FPGA chip for processing, has high compression rate and short compression time, and can release the computer to do other processing, and the compressed data can be further compressed by traditional compression methods to improve image compression rate.

Owner:WUHAN ZHONGYUAN HUADIAN SOFTWARE

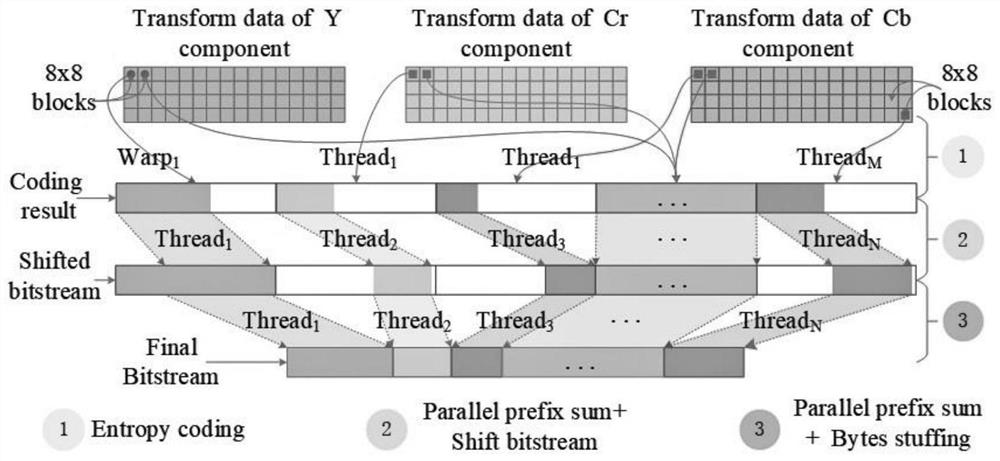

JPEG parallel entropy coding method based on GPU

ActiveCN114765684AIncrease compression rateDigital video signal modificationEnergy efficient computingAlgorithmBlock transform

The invention provides a GPU (Graphics Processing Unit)-based JPEG (Joint Photographic Experts Group) entropy coding parallel processing method aiming at the rate problem of traditional JPEG entropy coding. The method mainly comprises the following three parallel processing steps: firstly, aiming at all 8 * 8 DCT (Discrete Cosine Transform) data of a to-be-processed image, designing an efficient parallel strategy to code and generate respective binary code streams; then, proper shifting operation is carried out on each 8 * 8 block code stream to ensure that adjacent 8 * 8 block code streams are filled together without intervals; and finally, filling all 8 * 8 code streams together to obtain compressed image data. Experimental results show that compared with traditional JPEG entropy coding, the method disclosed by the invention has the advantage that the image compression rate is greatly improved on the premise of not influencing the quality of the compressed image.

Owner:SICHUAN UNIV

A New Axial Turbine

ActiveCN110043451BHigh speed rotationIncrease the speed of rotary cuttingPositive displacement pump componentsRotary piston pumpsAir compressionRotational axis

The invention discloses a novel axial-flow turbo-machine. The novel axial-flow turbo-machine comprises a shell and a driving motor, the output end of the driving motor is fixedly provided with a rotating shaft extending into the shell, a fan blade assembly is arranged on an air inlet of the shell, the fan blade assembly comprises a fixed ring plate, an annular groove is formed around the circumference of the inner wall of the fixed ring plate, an annular bearing is fixed to the rotating shaft, rotary cutting blades are fixed to the annular bearing, the bottoms of the ends, not making contact with the annular bearing, of the rotary cutting blades are fixedly provided with arc sliding blocks, the arc sliding blocks are located in the annular groove one by one, and the rotary cutting blades can do circumference motion between the annular bearing and the inner wall of the fixed ring plate. The machine is reasonable in structural design and convenient to use, the rotary cutting blades can do independent high-speed rotation, the rotary cutting rate of the air is improved, and the rate of air compression in a compression room can be improved.

Owner:JIANGSU MARITIME INST

A high-speed lossless data compression method based on a hybrid platform of GPU and CPU

ActiveCN103427844BImprove matching speedShorten the timeCode conversionData compressionArray data structure

Owner:HUAZHONG UNIV OF SCI & TECH

A 3D model data compression method and system

ActiveCN105931279BIncrease the compression ratioIncrease compression rateImage coding3D modellingData compression24-bit

The invention specifically relates to a three-dimensional model data compression method and system, and the method comprises the steps: enabling each floating-type top coordinate in to-be-compressed three-dimensional model data to be divided into high 8-bit data and low 24-bit data; respectively arranging the high 8-bit data and low 24-bit data according to a preset sequence, and storing the ordered high 8-bit data and low 24-bit data; enabling a first index value in the to-be-compressed three-dimensional model data to serve as a reference value, and calculating the offset relative to an (N-1)-th index value except the N-th index value, wherein the index value is an integer, the offset of the N-th index value relative to the (N-1)-th index value is equal to the difference between the N-th index value and the (N-1)-th index value, and N is not less than two; and carrying out the LZMA coding of the to-be-compressed three-dimensional model data processed through the above steps. Through the above technical scheme of the invention, the method can improve the compression rate of three-dimensional model data.

Owner:邱友龙

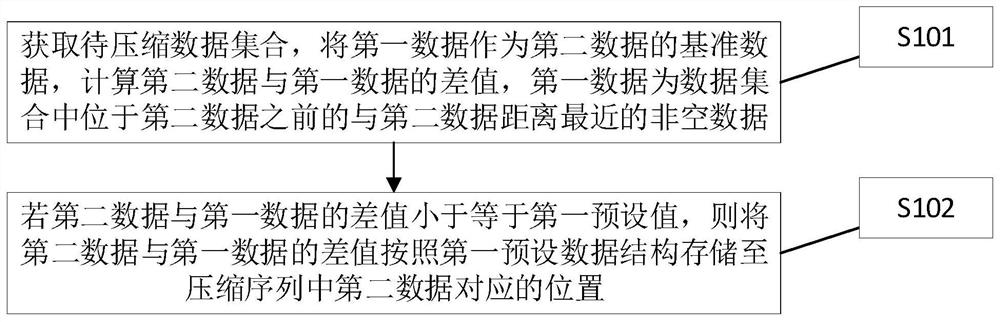

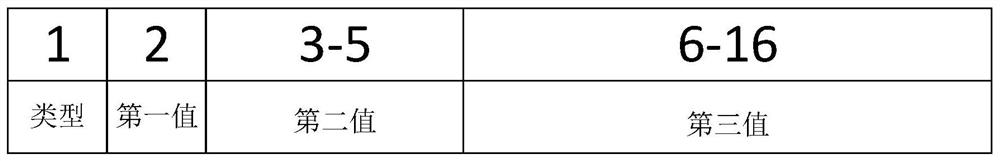

Power load data compression method and terminal

PendingCN113742303AReduce data storageReduce complexityData processing applicationsDigital data information retrievalEngineeringData compression

The invention provides a power load data compression method and a terminal. The method comprises the following steps that: a to-be-compressed data set is obtained; the first data is used as reference data of second data, and the difference value between the second data and the first data is calculated, wherein the first data is non-null data which is located in front of the second data in the data set and is closest to the second data; and if the difference value between the second data and the first data is smaller than or equal to a first preset value, the difference value between the second data and the first data is stored to the position, corresponding to the second data, in the compressed sequence according to a first preset data structure, the absolute value of the difference value is a * 10<n>, the first preset data structure comprises a first value, a second value and a third value, the first value is a * 10<n>, the first value is used for representing that the difference value is a positive number or a negative number, the second value is the value of an index n in 10n, the third value is the value of a, and n is a negative integer. The compression speed of the power data can be improved.

Owner:国网河北省电力有限公司营销服务中心 +1

A leachate treatment device for a garbage transfer station

ActiveCN110328212BEfficient collectionEasy to collectTransportation and packagingSolid waste disposalEnvironmental engineeringMechanical engineering

Owner:ANHUI LANDING ENVIRONMENTAL PROTECTION ENERGY TECH