Shallow trench isolation structure and forming method thereof

An isolation structure and shallow trench technology, which is applied in the manufacture of electrical components, electrical solid devices, semiconductor/solid devices, etc., can solve problems such as edge depressions and achieve the effect of improving yield

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

no. 1 example

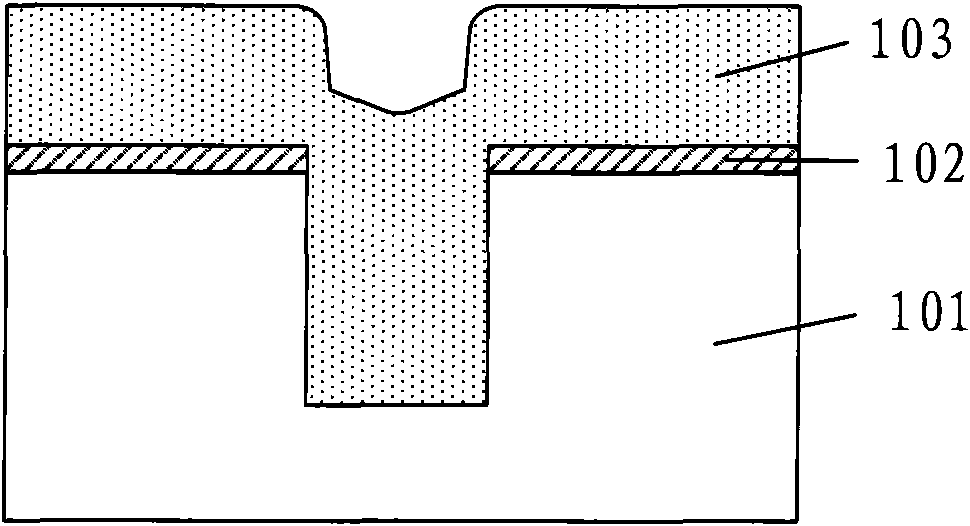

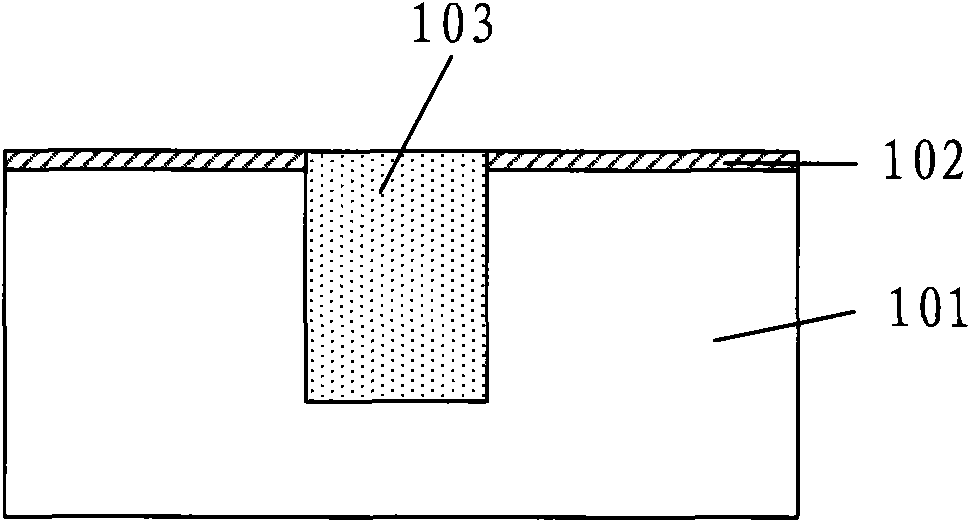

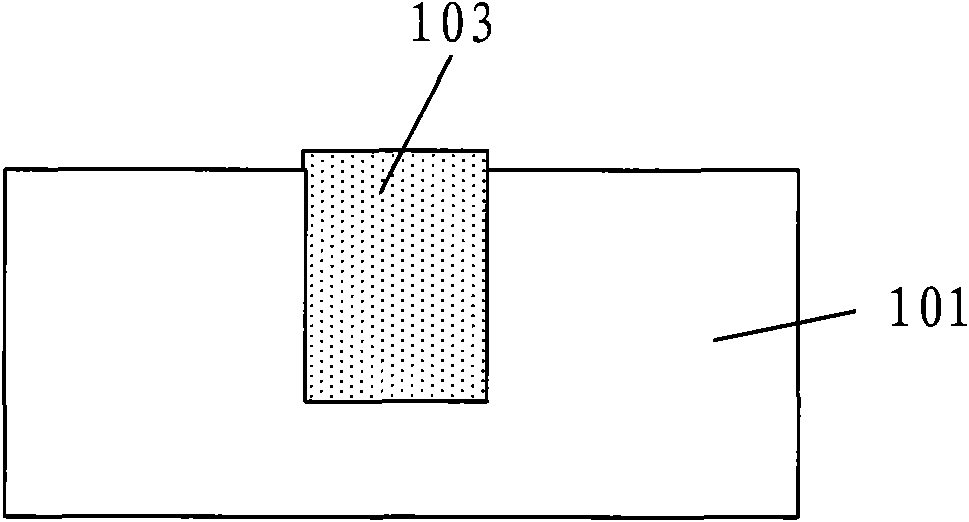

[0062] This embodiment introduces a method for forming a shallow trench isolation structure, Figure 5 A flowchart of a method for forming a shallow trench isolation structure according to the first embodiment of the present invention, Figure 6 to Figure 13 In order to illustrate the schematic cross-sectional view of the device of the method for forming the shallow trench isolation structure according to the first embodiment of the present invention, the following is combined with Figure 5 to Figure 13 The first embodiment of the present invention will be described in detail.

[0063] The method for forming a shallow trench isolation structure in this embodiment includes the steps of:

[0064] Step 501: Provide a substrate on which a stop layer has been formed.

[0065] Image 6 It is a schematic cross-sectional view of the substrate in the first embodiment of the present invention, such as Image 6 As shown, the substrate provided in this embodiment is a silicon substra...

no. 2 example

[0096] This embodiment introduces a shallow trench isolation structure, Figure 14 It is a schematic cross-sectional view of the shallow trench isolation structure in the second embodiment of the present invention. like Figure 14As shown, the shallow trench isolation structure in this embodiment has a trench formed in the substrate 1401, the trench has a filler 1404, and there is also a gap between the inner sidewall of the trench and the filler 1404. There is a protective medium layer 1410 .

[0097] In this embodiment, the filler is silicon oxide formed by a high-density plasma chemical vapor deposition method, the protective medium layer can be a silicon nitride layer or a silicon oxynitride layer, and the growth thickness of the protective medium layer can be exist to between, if Wait.

[0098] Considering that in the process of device formation, introducing a material layer with stress can improve device characteristics. For example, compressive strain along th...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More