Semiconductor element mounting structure and semiconductor element mounting method

A semiconductor and structure technology, which is applied in the fields of semiconductor/solid-state device parts, semiconductor devices, and semiconductor/solid-state device manufacturing, etc., can solve the problems of complicated manufacturing process and difficulty in configuring reinforcement members 711, etc., to reduce the area and reduce the thermal expansion difference. The effect of poor thermal shrinkage and prevention of internal breakage

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

no. 1 approach

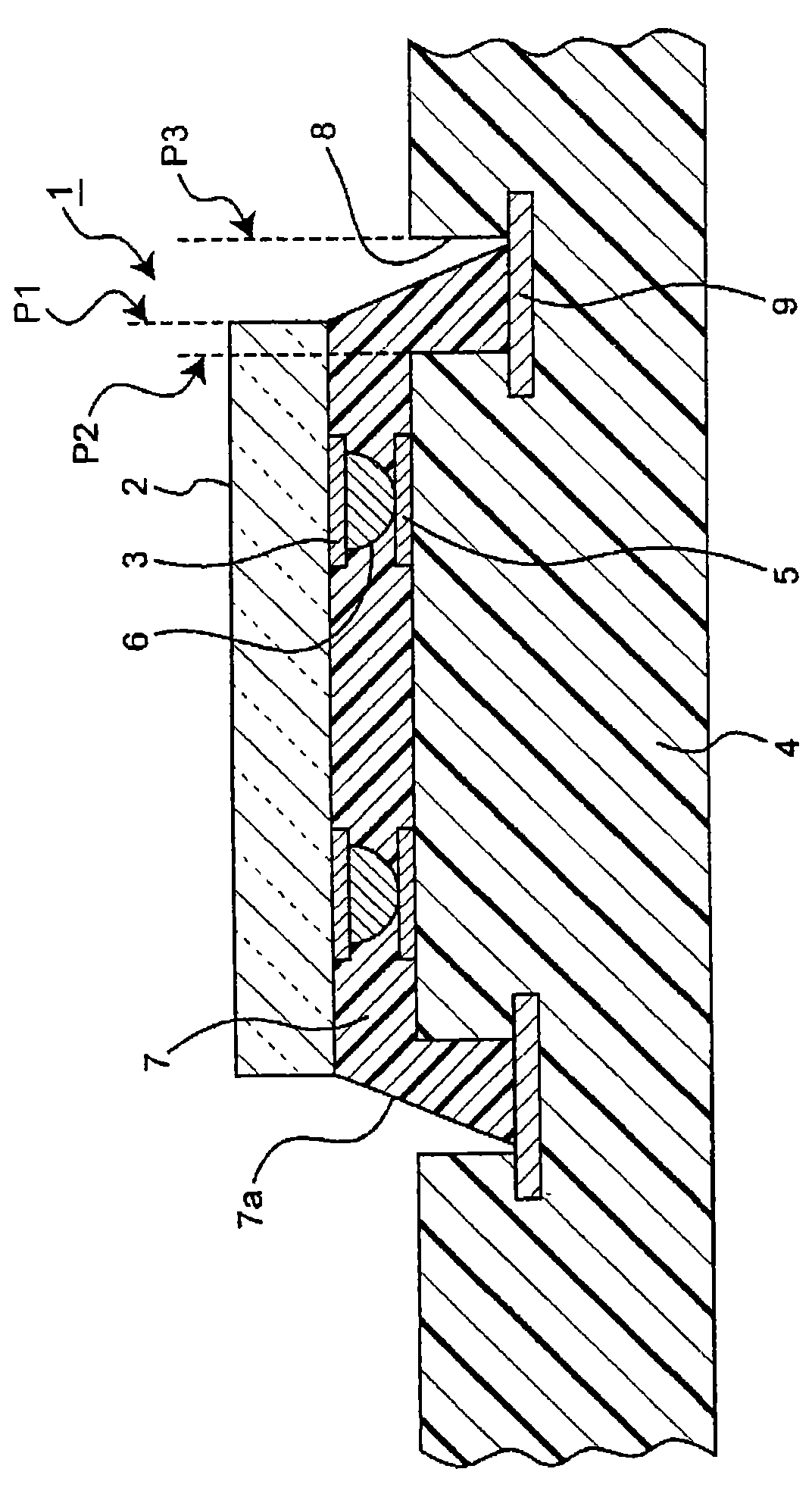

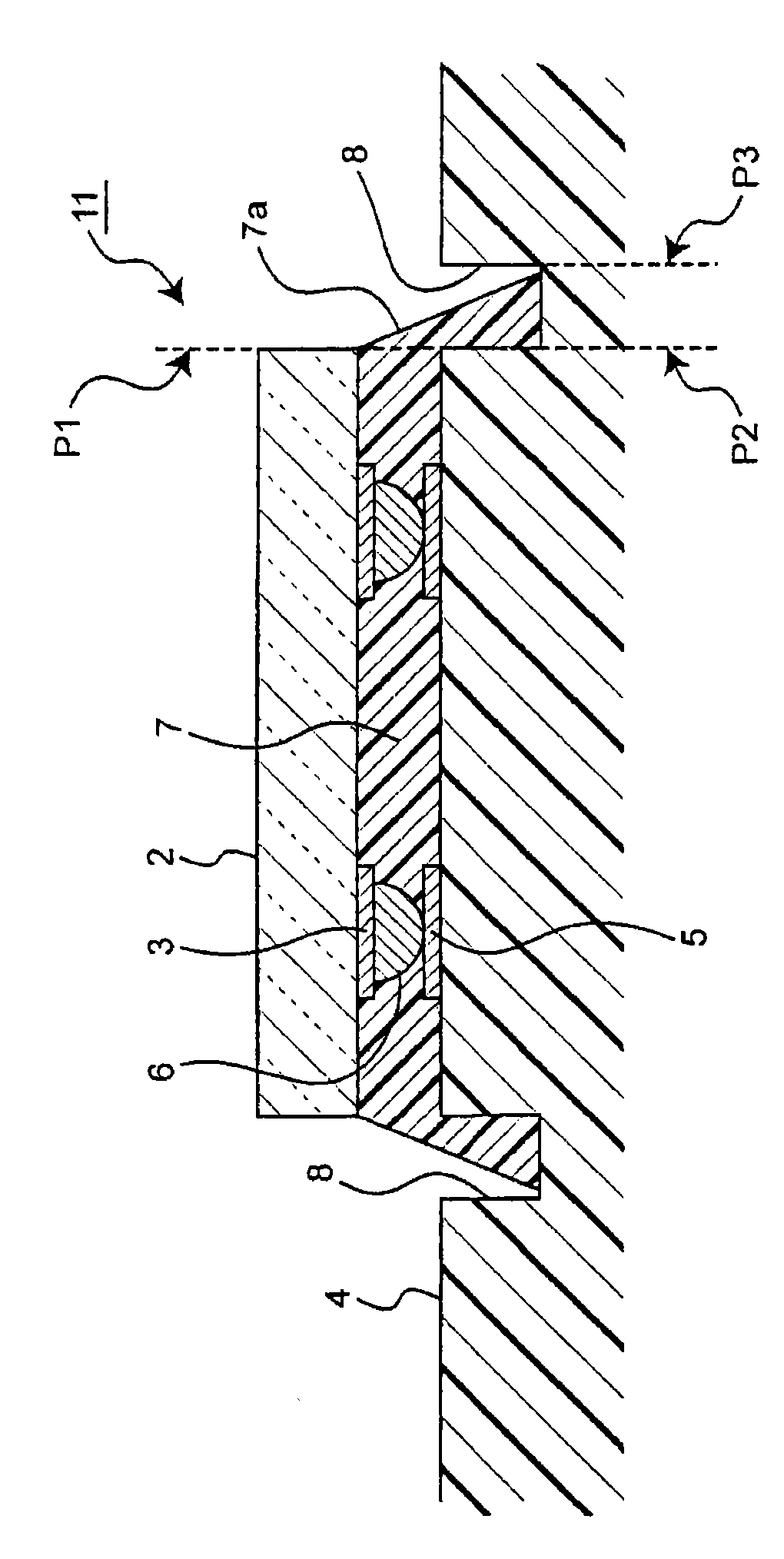

[0057] figure 1 A schematic cross-sectional view of a semiconductor chip mounting structure 1 as an example of the semiconductor element mounting structure according to the first embodiment of the present invention is shown in .

[0058] like figure 1 As shown, in the semiconductor chip mounting structure 1 of the first embodiment, a sheet-shaped underfill 7 as an example of a resin for sealing and bonding is disposed on a substrate 4, and a semiconductor chip 2 is mounted through the underfill 7. . A plurality of pads 3 as an example of element electrodes are formed on the lower surface side in the figure of the semiconductor chip 2, that is, on the circuit formation surface, and are formed on the upper surface side of the substrate 4 in a manner corresponding to the formation positions of these pads 3. That is, a plurality of substrate electrodes 5 are formed on the circuit formation surface (electrode formation surface), and each pad 3 and each substrate electrode 5 are...

no. 2 approach

[0079] In addition, this invention is not limited to the said embodiment, It can implement in other various forms. E.g, Image 6 A schematic cross-sectional view of a semiconductor chip mounting structure 31 as an example of a semiconductor element mounting structure according to the second embodiment of the present invention is shown in . In addition, in Image 6 In the semiconductor chip mounting structure 31, members having the same configuration as those of the mounting structure 1 of the first embodiment are denoted by the same reference numerals, and description thereof will be omitted.

[0080] like Image 6 As shown, the semiconductor chip mounting structure 31 of the second embodiment has a different structure from the semiconductor chip mounting structure 1 of the above-mentioned first embodiment in that the inner bottom 38a of the recess 38 is formed as an inclined surface. . Hereinafter, this different structure will be mainly described.

[0081] like Image ...

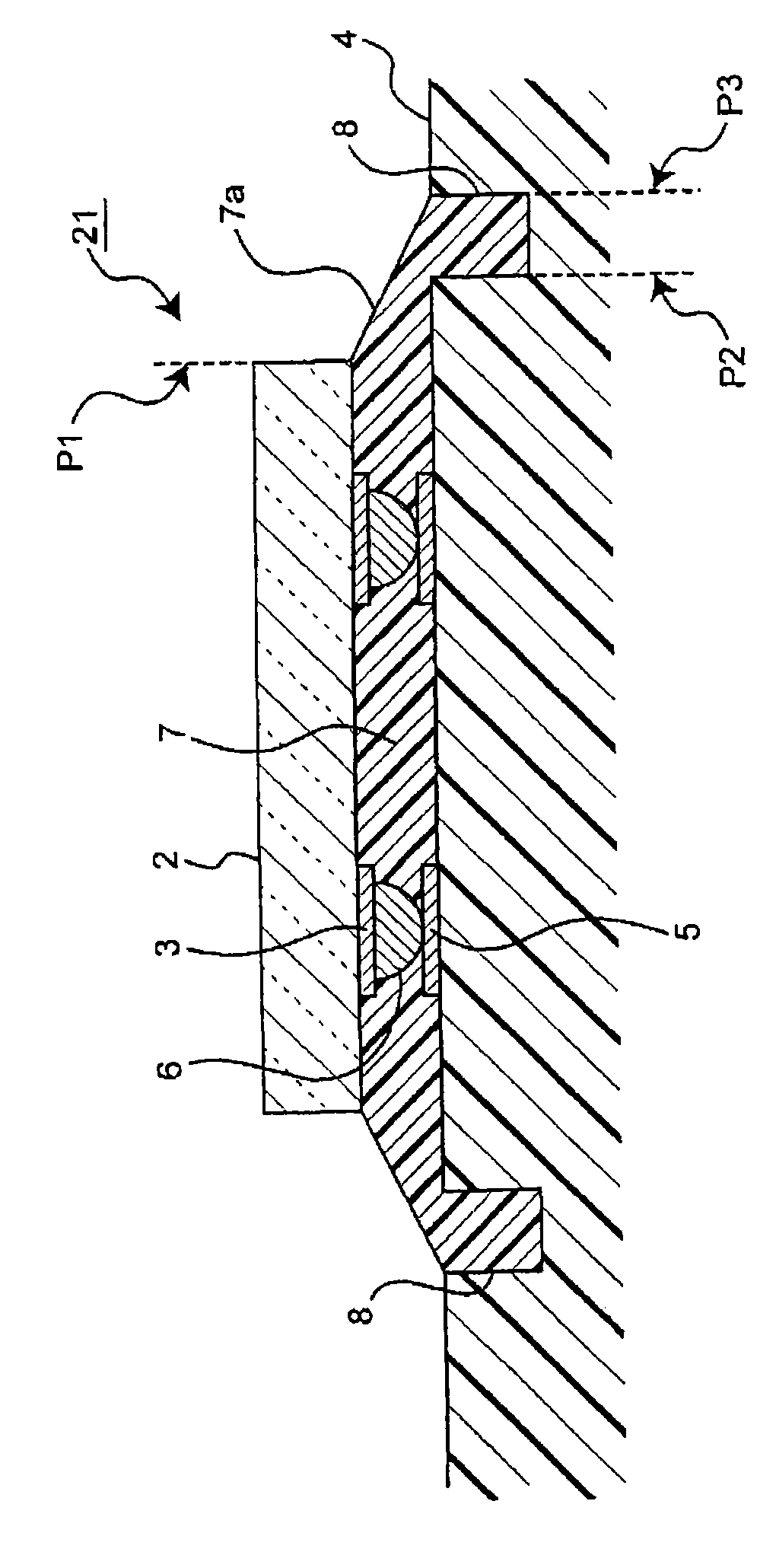

no. 3 approach

[0091] under, Figure 10 A schematic cross-sectional view of a semiconductor chip mounting structure 71 according to a third embodiment of the present invention is shown in . like Figure 10 As shown, the semiconductor chip mounting structure 71 of the third embodiment has the same Image 6 The mounting structure 31 of the above-mentioned second embodiment shown has the same arrangement structure of the recesses 38, but the fact that the protruding portion 79 is formed in the vicinity of the substantially center of the mounting area of the substrate 4 compared with other surfaces is the same as Image 6 structure is different.

[0092] like Figure 10 As shown, by forming the raised portion 79 approximately in the vicinity of the center of the mounting area, a gradient is formed from the top of the raised portion 79 to the deepest portion of the recessed portion 38 via the sloped inner bottom 38a in the recessed portion 38 . Such gradients may be formed radially from, fo...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More