Method for forming semiconductor interconnected structure

An interconnection structure and semiconductor technology, applied in semiconductor/solid-state device manufacturing, electrical components, circuits, etc., can solve problems such as electromigration, increased delay of semiconductor devices, and reduced clock frequency

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment Construction

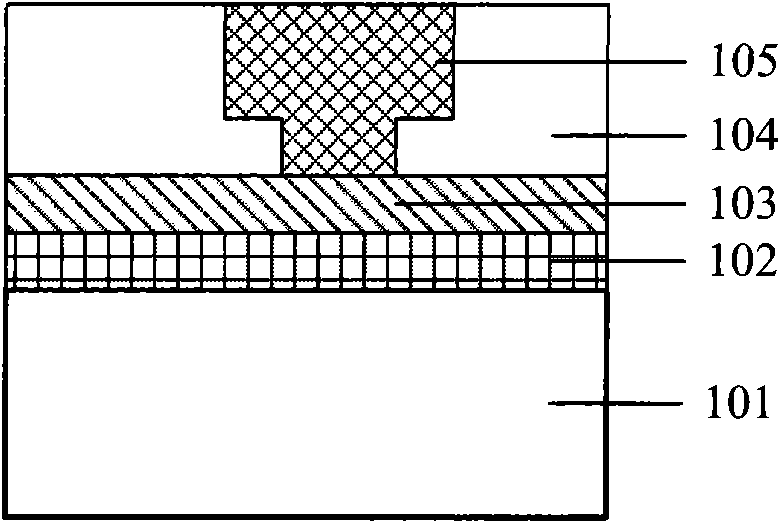

[0023] In this embodiment, by reducing the oxidized inner metal layer in the semiconductor metal interconnection structure, the acidic atmosphere in the subsequent process steps is prevented from corroding the inner metal layer, thereby improving the reliability of the manufactured semiconductor device, reducing delay and increasing Clock frequency.

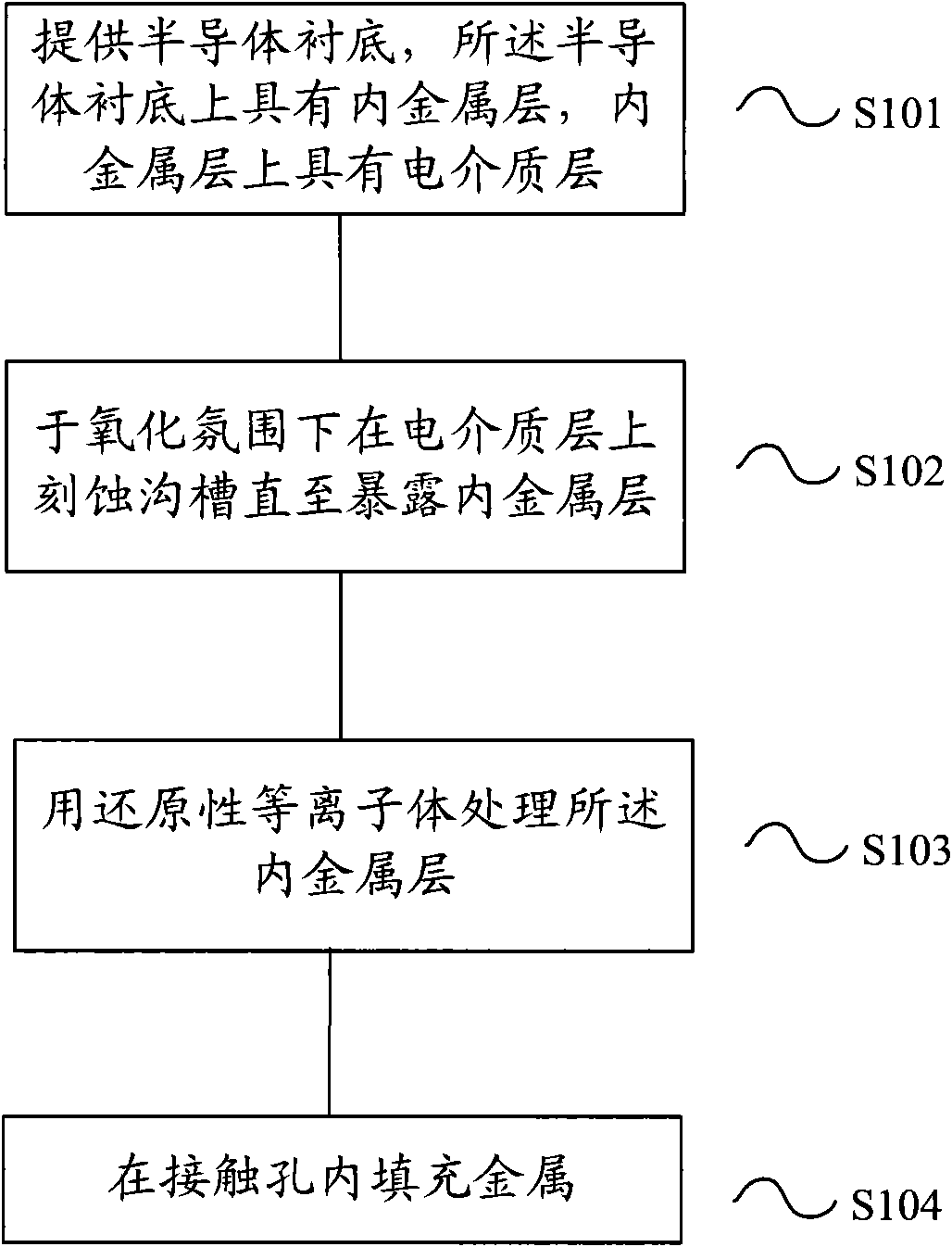

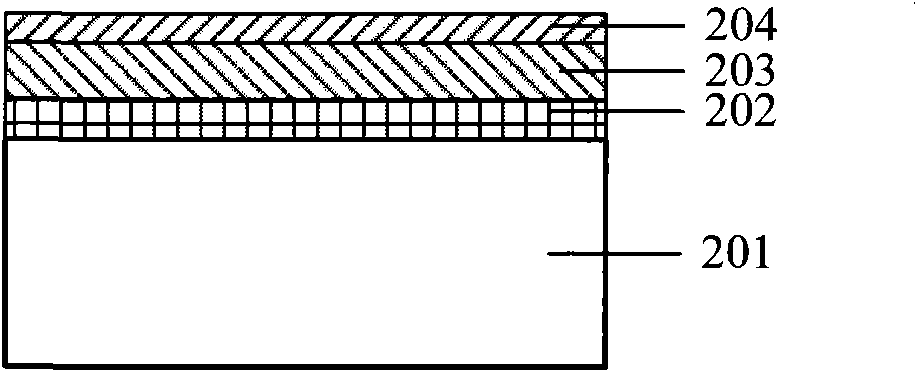

[0024] To this end, the present embodiment provides a method for forming a semiconductor interconnection structure, comprising the steps of: providing a semiconductor substrate, having an inner metal layer on the semiconductor substrate, and a dielectric layer on the inner metal layer; Etching a through hole until the inner metal layer is exposed; treating the inner metal layer with reducing plasma; filling the through hole with conductive material. Optionally, the reducing plasma is plasma containing hydrogen. Optionally, the process conditions for the hydrogen-containing plasma to treat the inner metal layer are hydrogen flow ...

PUM

| Property | Measurement | Unit |

|---|---|---|

| Etching power | aaaaa | aaaaa |

Abstract

Description

Claims

Application Information

Login to View More

Login to View More