Ion doping method of memory cell in dram

An ion doping, memory cell technology, applied in electrical components, semiconductor/solid-state device manufacturing, circuits, etc., can solve problems such as poor surface adhesion of silicon substrates

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment Construction

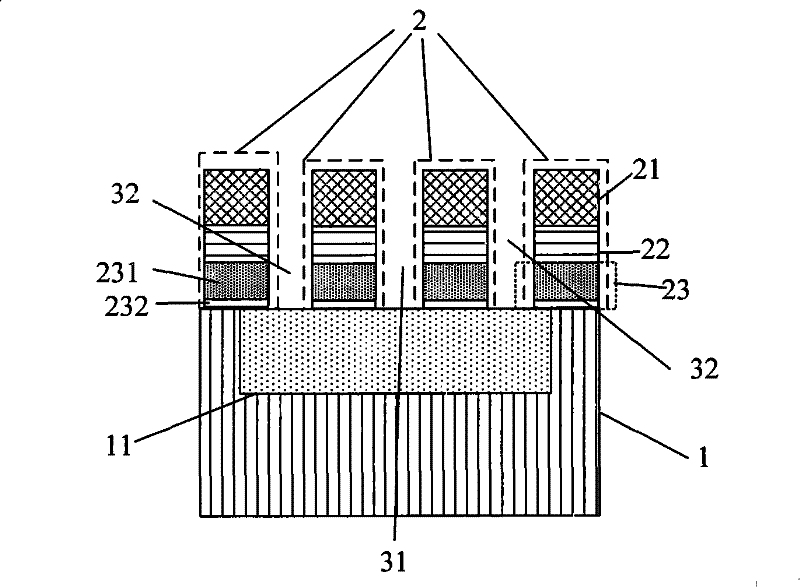

[0022] see figure 1 , the ion doping method of memory cell in DRAM of the present invention, wherein, memory cell has active region 11, and active region 11 is made in silicon substrate 1, and silicon substrate 1 is made with several word lines 2 of doping structure. Ion doping method of the present invention comprises the following steps:

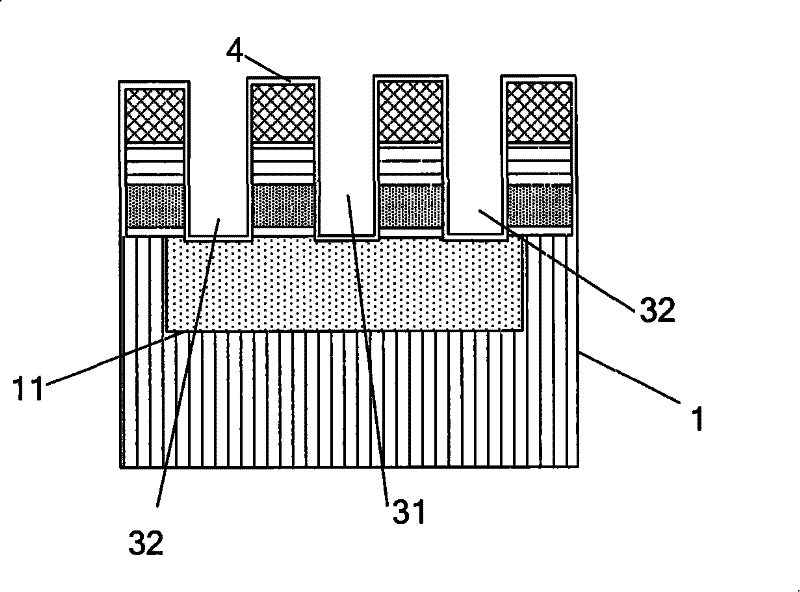

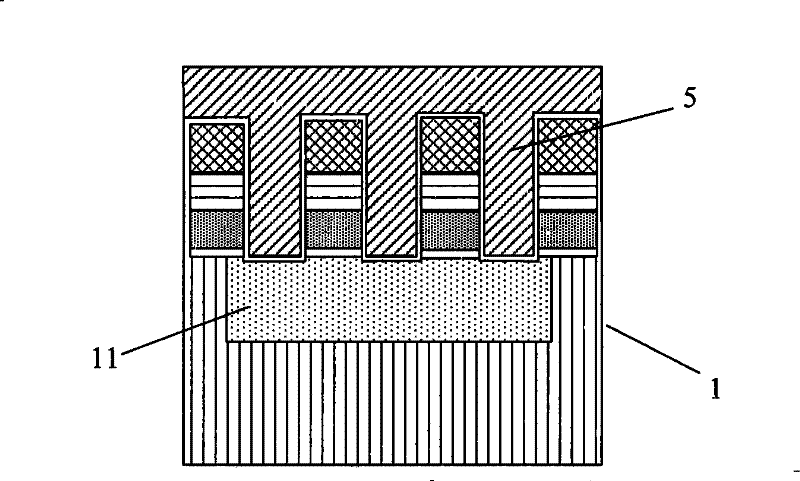

[0023] Step 1 see Figure 1~2 , oxidation figure 1 The surface and sidewall of the word line 2 with the doping structure shown, and the surface of the silicon substrate 1 between the word lines 2 with the doping structure. A thin layer of oxide 4 is formed on the entire surface of the memory cell device. see figure 1 The doped structure word line 2 includes a gate structure word line layer 23, a word line ohmic contact layer 22 and a word line mask layer 21 which are sequentially located on the surface of the active region of the silicon substrate 1; the gate structure word line layer 23 includes a layer which is sequentially located ...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More