Semiconductor device and bias generating circuit

A technology for generating circuits and semiconductors, which is applied in the manufacture of semiconductor devices, circuits, semiconductor/solid-state devices, etc., can solve the problems of increased circuit scale and increased circuit power consumption, and achieves improved degrees of freedom, low power consumption, and small circuits effect of scale

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment Construction

[0038] Hereinafter, embodiments of the present invention will be described with reference to the drawings.

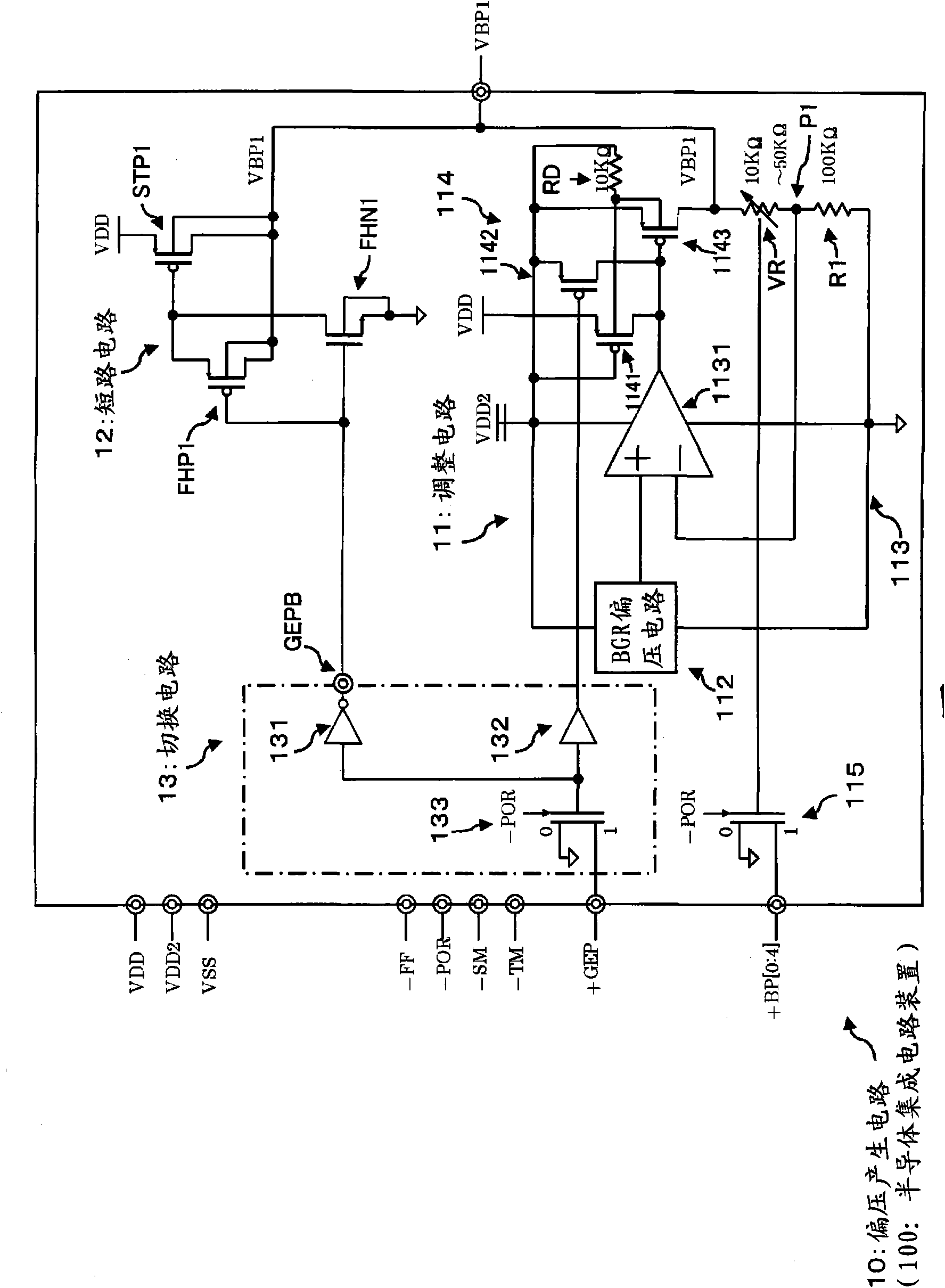

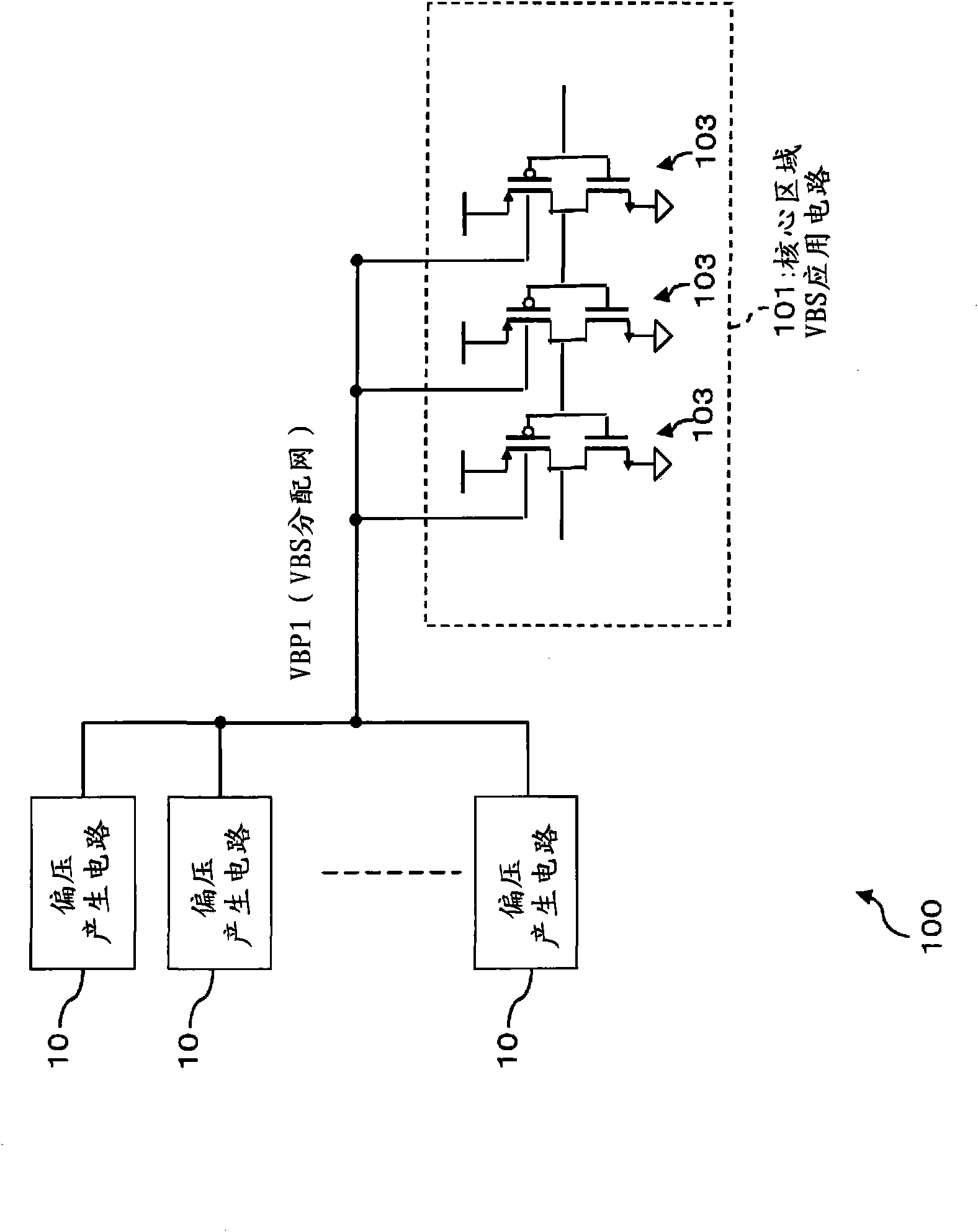

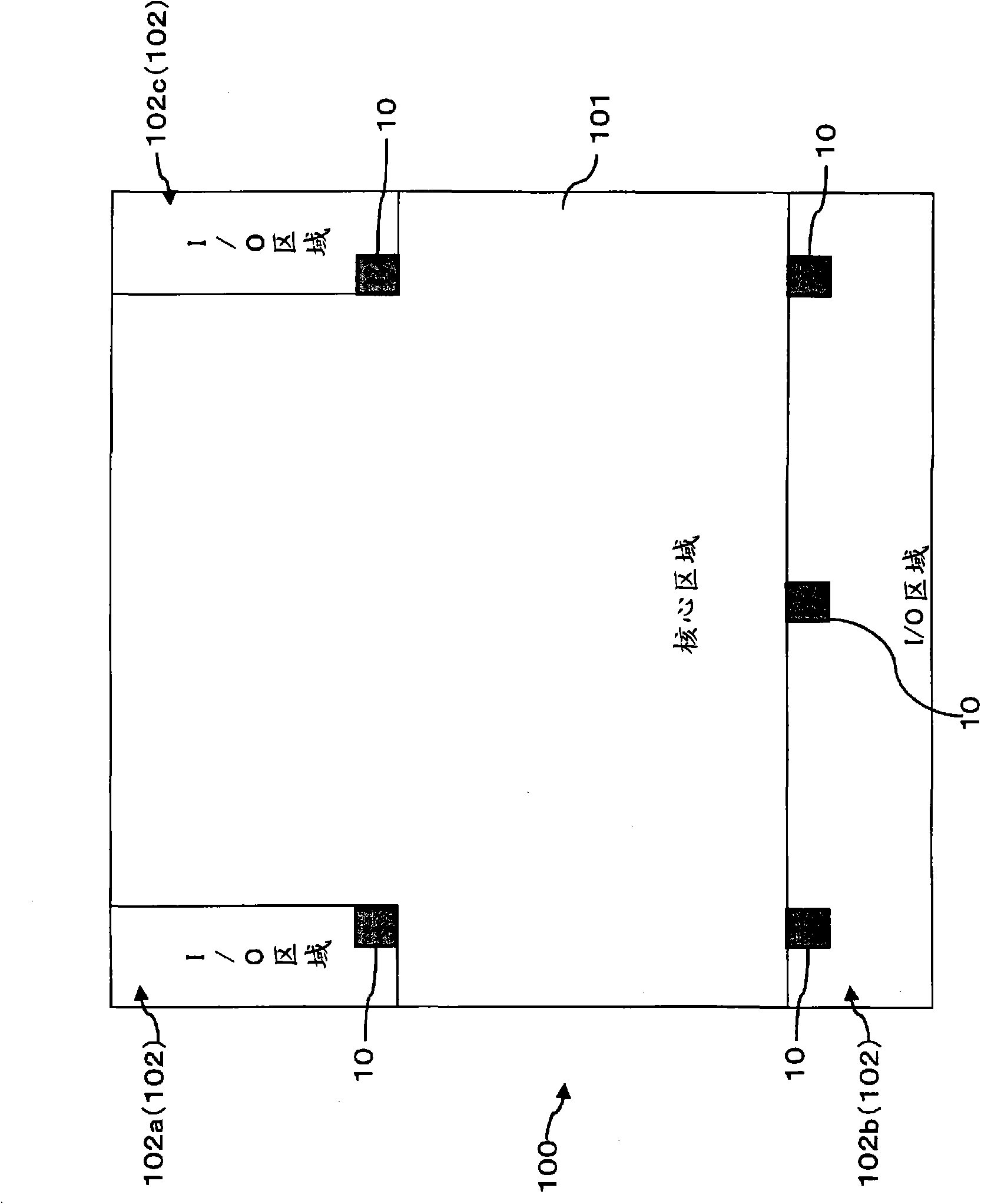

[0039] figure 1 is a circuit configuration diagram of a bias voltage generating circuit 10 according to an embodiment of the present invention, figure 2 It is a figure which shows the example of the output connection of the bias voltage generating circuit 10 in the semiconductor integrated circuit device 100, image 3 is a diagram showing an example of its arrangement, Figure 4 It is a figure showing the description of the terminals in a list.

[0040] Such as figure 2 As shown, the bias generating circuit 10 is provided in a semiconductor integrated circuit device (LSI: Large Scale Integration; semiconductor device) 100, and is connected to the core region 101 of the semiconductor integrated circuit device 100 (see figure 2 , image 3 ) used in the substrate of the PMOS transistor (transistor) 103 and generates a circuit for reverse bias voltage VBS (substrat...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More