System and method for recovering high-speed 8PSK clocks parallelly

A clock recovery, high-speed technology, applied in transmission systems, digital transmission systems, electrical components, etc., can solve problems such as large error jitter, no specific range of correction coefficients, and insufficient utilization

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment Construction

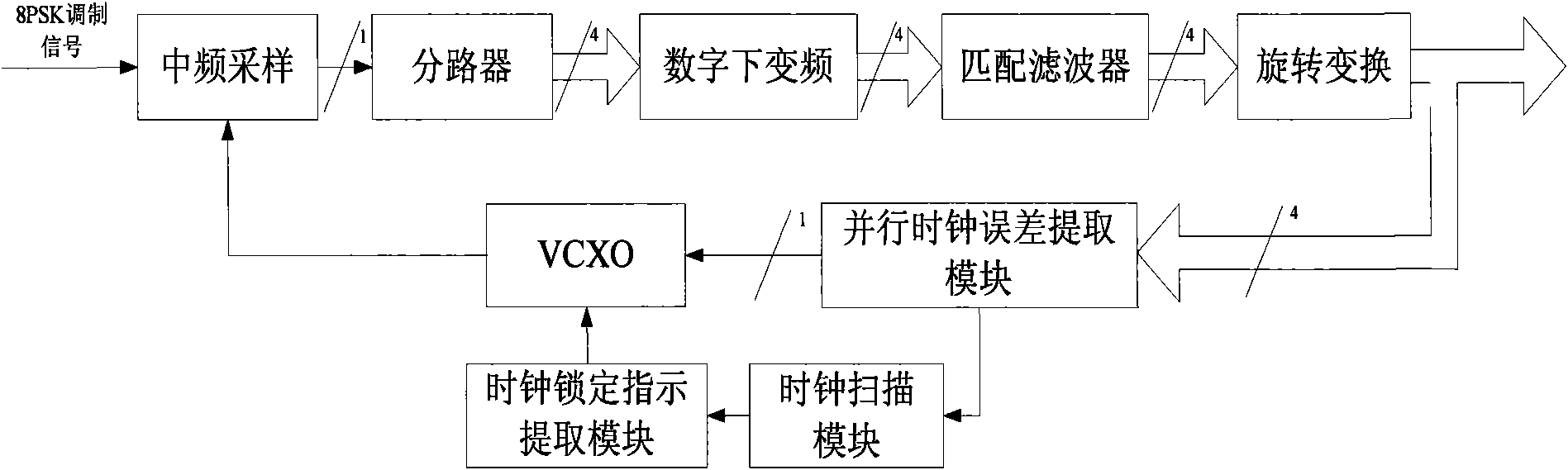

[0051] For the demodulation of high-speed 8PSK signals, limited by the internal processing clock of the device, a parallel clock recovery method is required. Under the condition that the highest frequency of the system remains unchanged, if the single channel data is processed in N channels in parallel, the demodulation code rate can be increased by N times. Of course, the resources required by the parallel structure compared with the single channel are also increased by N times accordingly. So this is actually a strategy of exchanging resources for speed.

[0052] The parallel clock recovery system and method of the present invention are introduced below through the system block diagram of the high-speed parallel digital receiver. The structural block diagram of the parallel clock loop applied by the parallel high-speed digital receiver is as follows figure 1 As shown, the 8PSK modulated signal of the radio frequency is demodulated and received by the method of coherent demod...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More