Compact semiconductor package with integrated bypass capacitor and method

A technology of semiconductors and capacitors, which is applied in the direction of semiconductor devices, semiconductor/solid-state device manufacturing, semiconductor/solid-state device components, etc. It can solve the problems of no large-scale top exposure and limited structural details of the input capacitor Cin

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

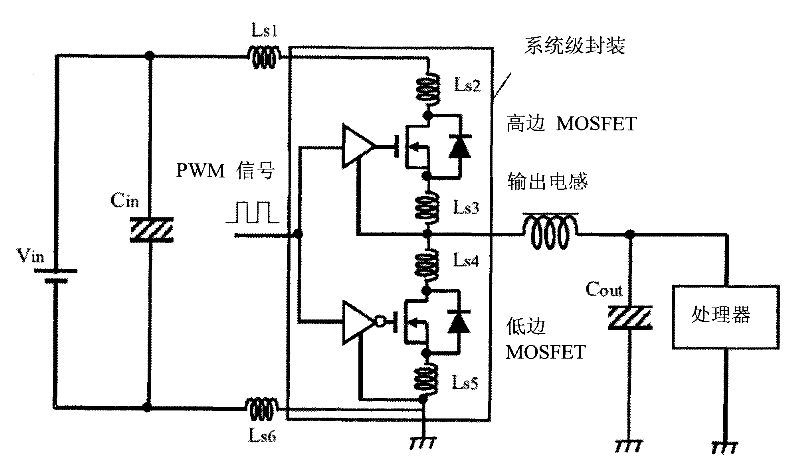

Problems solved by technology

Method used

Image

Examples

Embodiment Construction

[0058] The foregoing and following descriptions and drawings contained herein focus only on one or more presently preferred embodiments of the invention and illustrate some typical alternatives and / or alternative embodiments. Accordingly, the description and drawings are intended to be illustrative only and are not intended to limit the scope of the present invention. Various changes, modifications, and substitutions can be easily identified by those skilled in the art. These changes, modifications and substitutions should be considered to belong to the protection scope of the present invention.

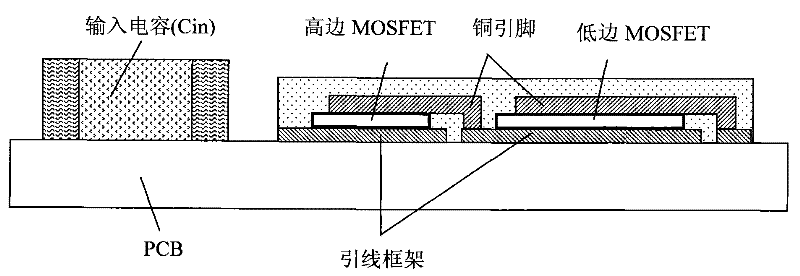

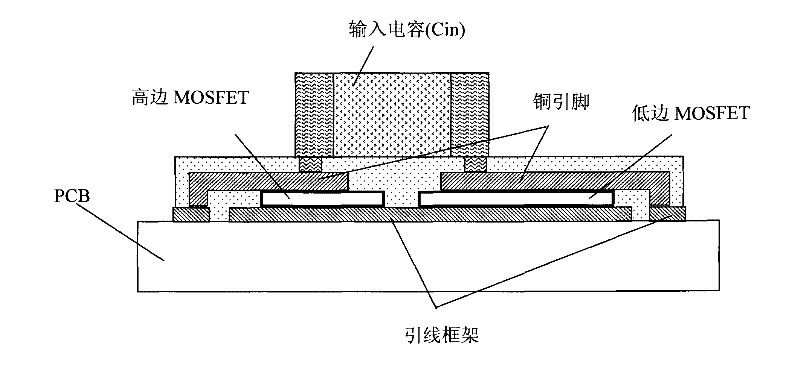

[0059] figure 2 A first part of semiconductor package 500 including semiconductor chip one 520a and semiconductor chip two 520b is shown in the present invention. The first part of the semiconductor package 500 includes:

[0060] A circuit substrate, i.e. lead frame 502 in this figure, contains several terminal leads 506a and 506b for external electrical connection;

[0061] The...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More