Multi-chip semiconductor package structure without outer leads and lead frame thereof

A technology of semiconductors and external pins, which is applied in the direction of semiconductor devices, semiconductor/solid-state device components, electric solid-state devices, etc., and can solve problems such as improving defective products, short-circuiting wires, and complexity

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

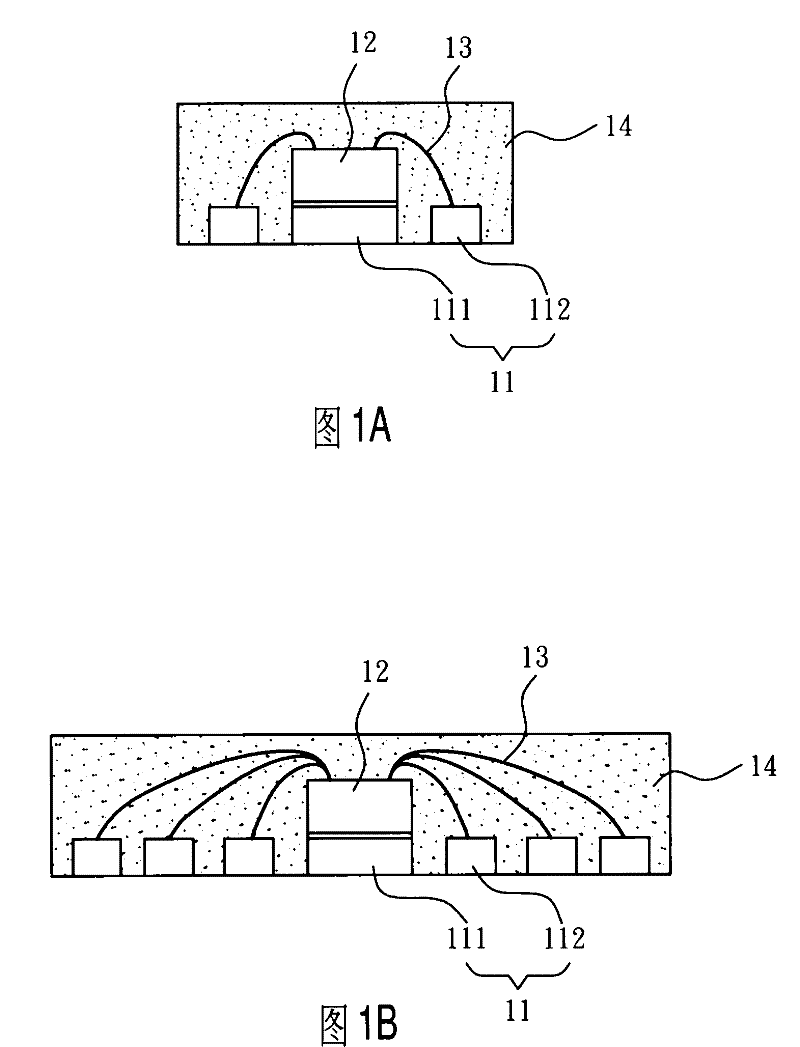

Image

Examples

Embodiment Construction

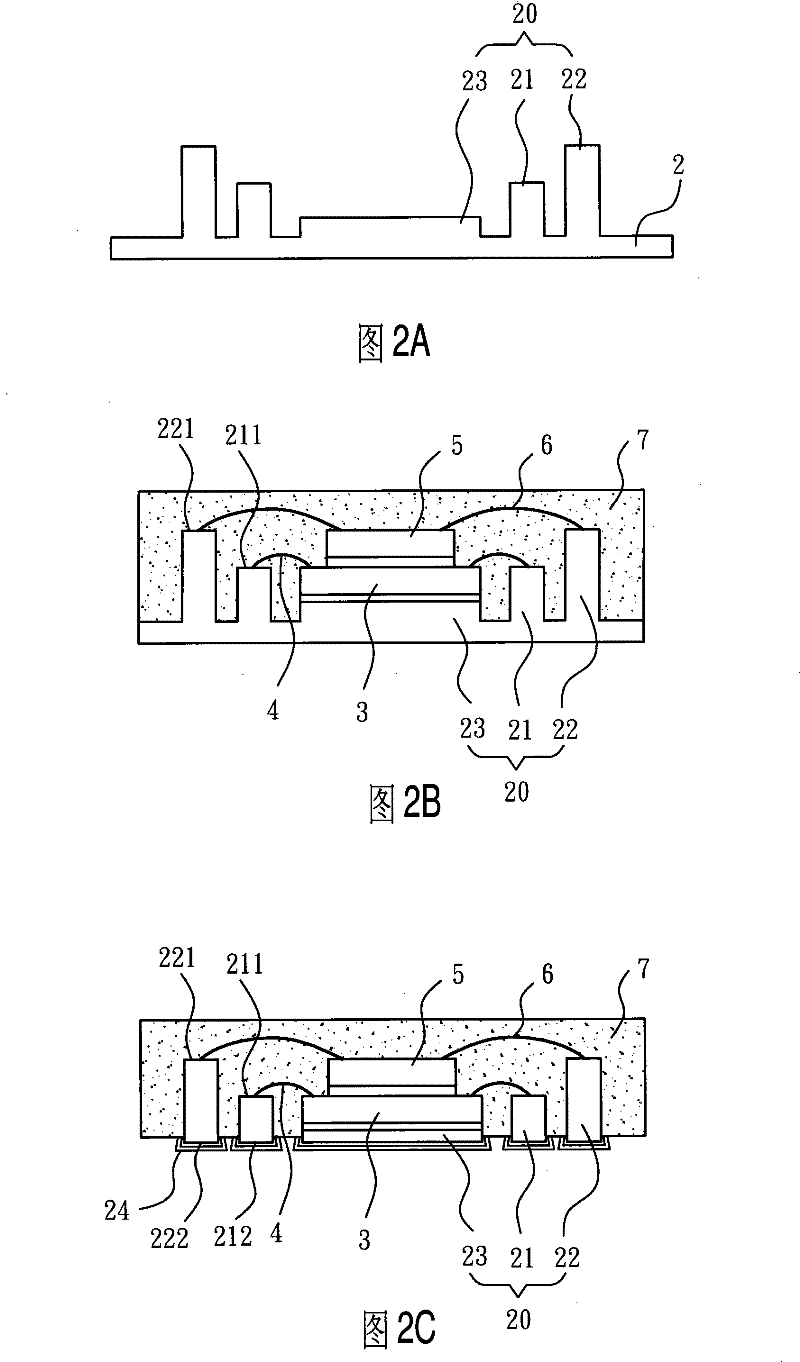

[0033] This embodiment will introduce the present invention in detail with reference to the drawings. The following descriptions of the various embodiments refer to the accompanying drawings to illustrate specific embodiments in which the present invention may be practiced. The direction terms mentioned in the present invention, such as "up", "down", "front", "rear", "left" or "right", etc., are only referring to the directions of the attached drawings. Therefore, the directional terms used are used to assist in explaining the relevant constructions, but not to limit the present invention.

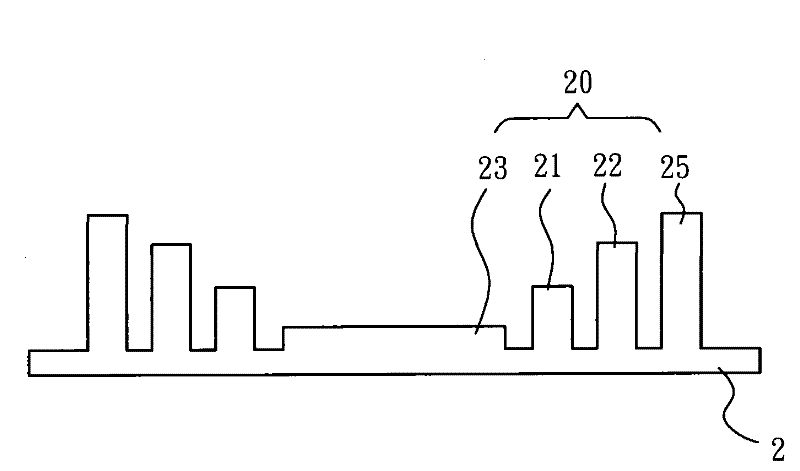

[0034] Please refer to Figure 2A , 2B As shown in and 2C, it discloses a schematic diagram of the manufacturing process of the multi-chip semiconductor package structure without external leads and the lead frame of the first embodiment of the present invention, which is used to illustrate the non-external leads of the first embodiment of the present invention Possible manufacturing met...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More