Method for improving IPS detection performance by adopting AMP architecture

A performance and data packet technology, applied in digital transmission systems, electrical components, transmission systems, etc., can solve the problems of powerless detection performance, insufficient flexibility and scalability, and inability to support functions, so as to reduce the number of data copies and improve processing Efficiency, the effect of reducing system calls

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment Construction

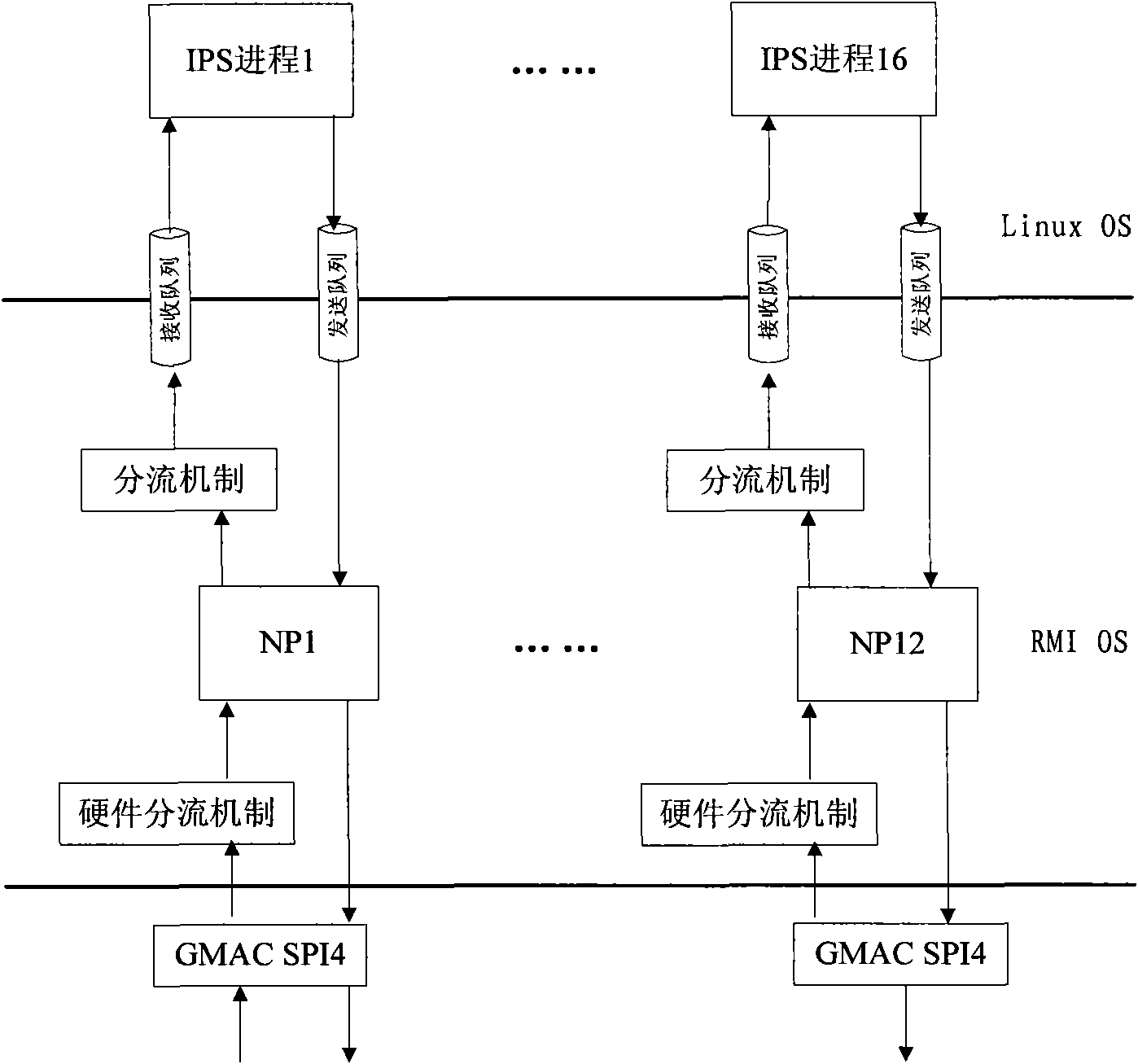

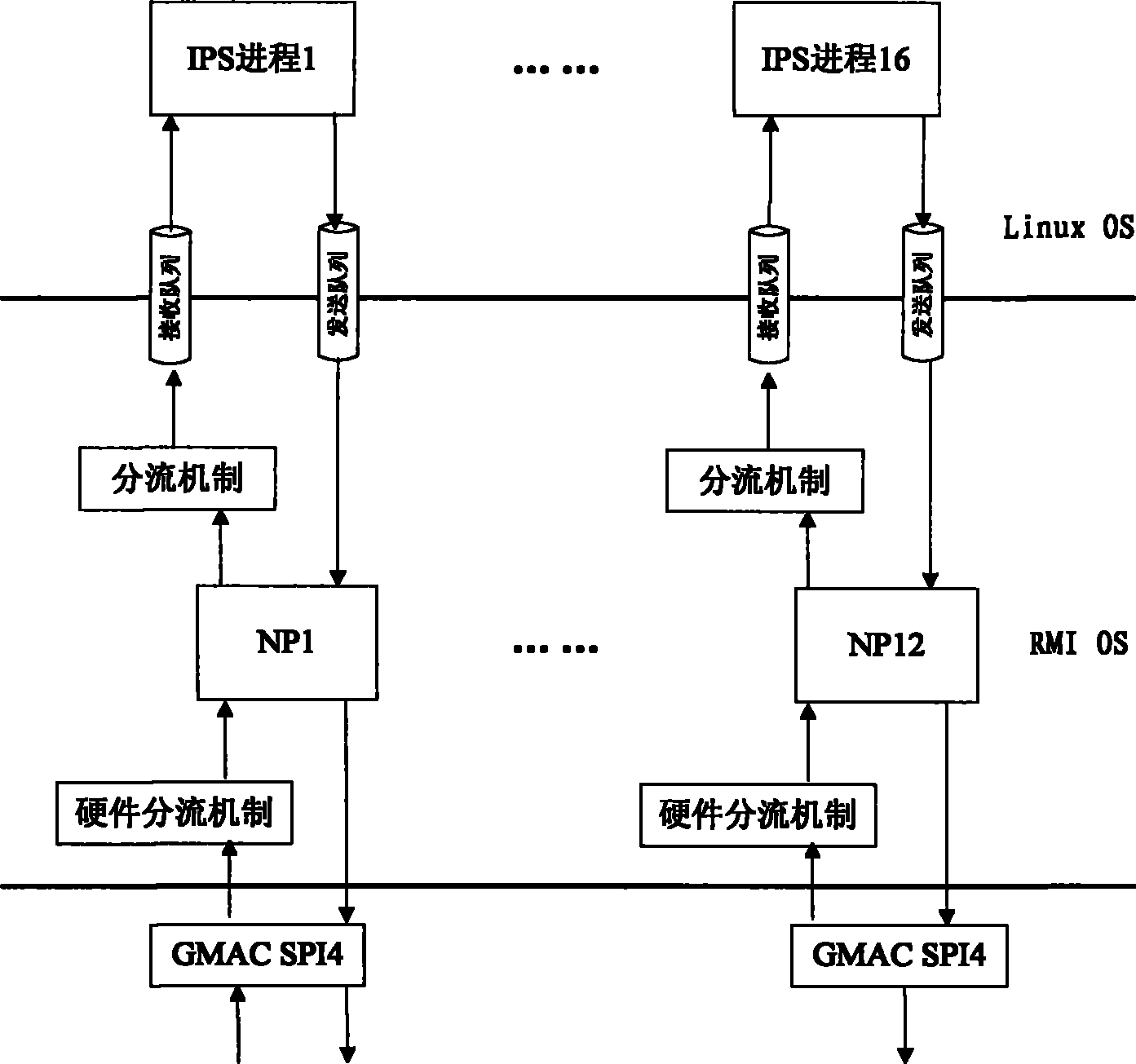

[0020] Below, refer to the attached Figure 1~2 The method for improving the detection performance of the IPS by using the AMP framework of the present invention is described in detail.

[0021] The core idea of the present invention is: to develop a multi-core based IPS system, the system adopts AMP architecture, so that the network processing of data packets and IPS detection are performed asynchronously, and the multiple processors inside the IPS detection process and network processing Parallel execution, so that multiple IPS detection processes are executed in parallel at any time, thus fundamentally solving the performance bottleneck of the IPS system.

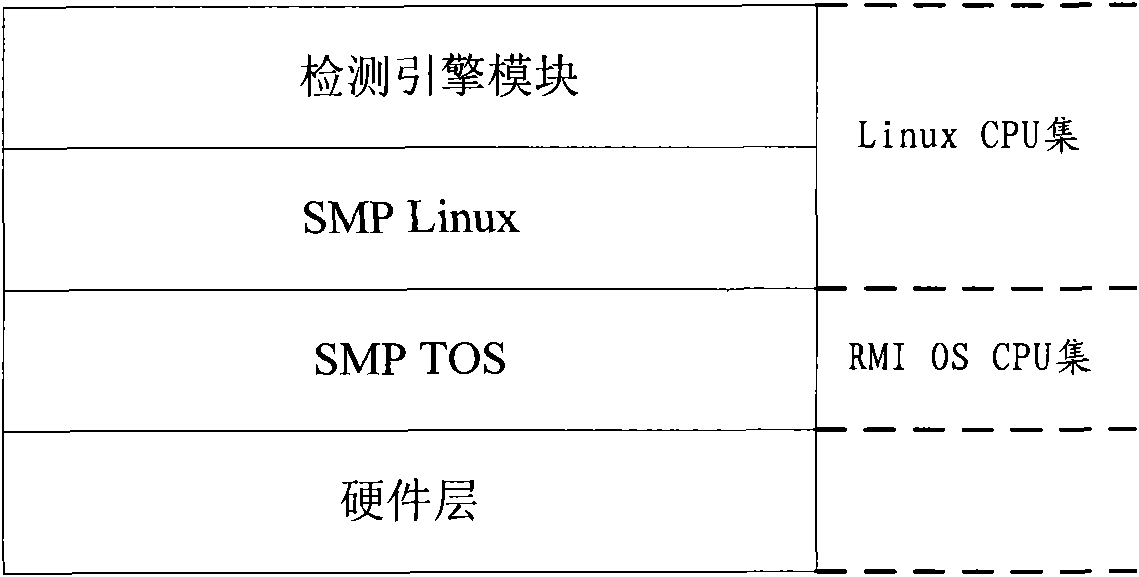

[0022] For multi-core processors, the CPU set (processor set) can be divided into a LinuxCPU set and an NP (network processor) set according to specific needs. The Linux CPU set is scheduled to execute the Linux operating system, and the IPS detection process is run on it; the NP set It is scheduled to execute the net...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More