Design and realization method of array multiplier based on reversible 'ZS' series gate

An implementation method and multiplier technology, applied in the field of quantum information, can solve problems such as difficult expansion, reduction of operating power consumption and design cost of computing components, and difficult multiplication of signed numbers.

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

specific Embodiment approach

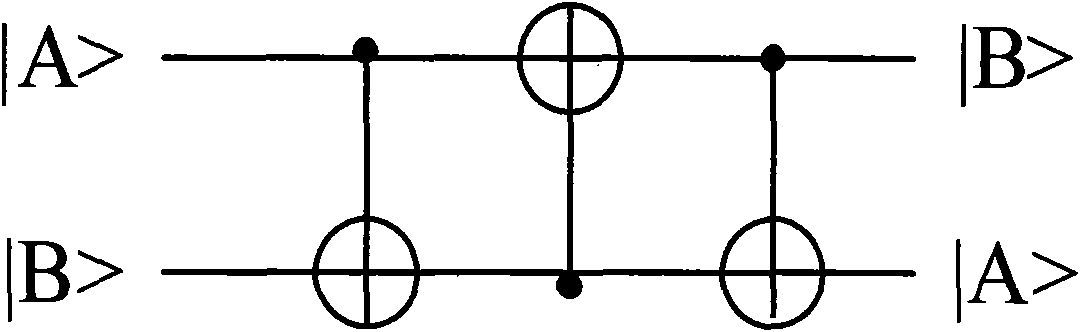

[0106] The "ZS1", "ZS2", and "ZS3" gate representations of the new reversible series "ZS" gates designed by the present invention are as follows Figure 7 , Figure 11 and Figure 15 is shown, and its corresponding truth table is given at the same time. In the truth table, there is a one-to-one relationship between input and output. Given the input, the output can be determined, and at the same time, the given output can get its only input. It can be verified that the series of "ZS" gates meet the reversible requirements.

[0107] The circuit design diagram of the reversible gate containing the double-qubit controlled gate and the single-qubit gate designed according to the series "ZS" gate of the present invention is as follows Figure 8 , Figure 12 and Figure 16 shown.

[0108] Figure 8 The corresponding modules are listed in, Figure 8 Among them, ①, ②, ③, and ④ are the modules required to form the "ZS1" gate, and 1, 2, 3, and 4 represent the output of No. 1, No. ...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More