Manufacturing method for reducing area of SONOS storage unit

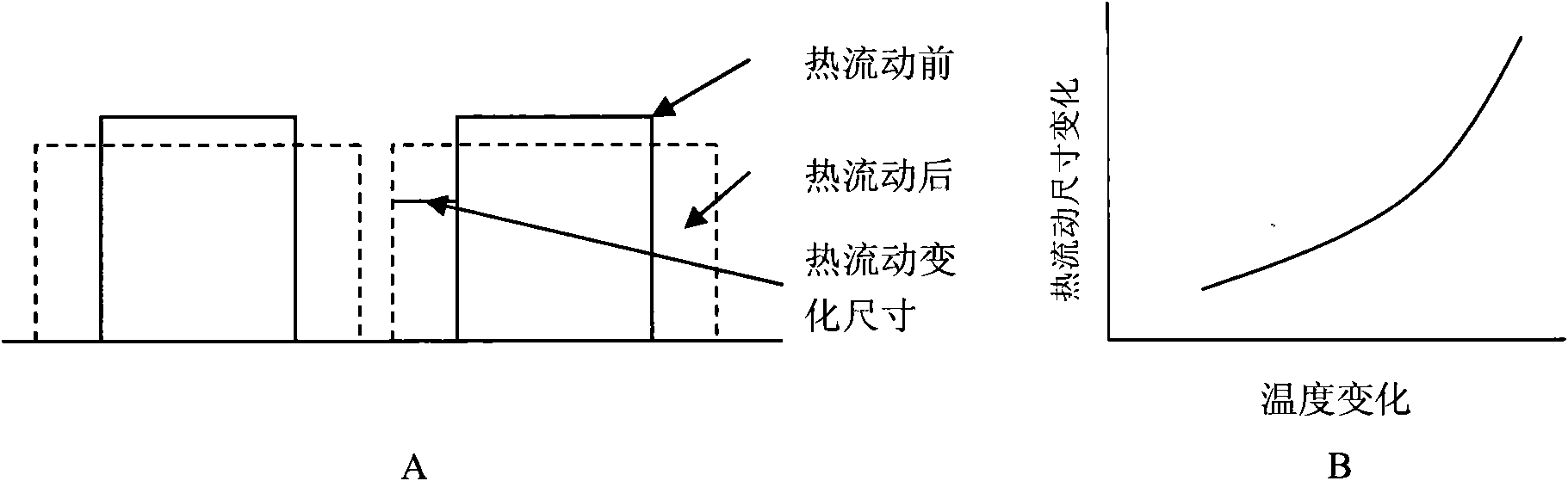

A technology for memory cells and manufacturing methods, which is applied in semiconductor/solid-state device manufacturing, electrical components, and photoplate-making process coating equipment, etc., and can solve problems such as minimum distance process limitations, breakdown failure, and lateral etching of the insulating oxide layer 2 , to achieve the effect of reducing lateral etching, shrinking spacing, and reducing unit area

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment Construction

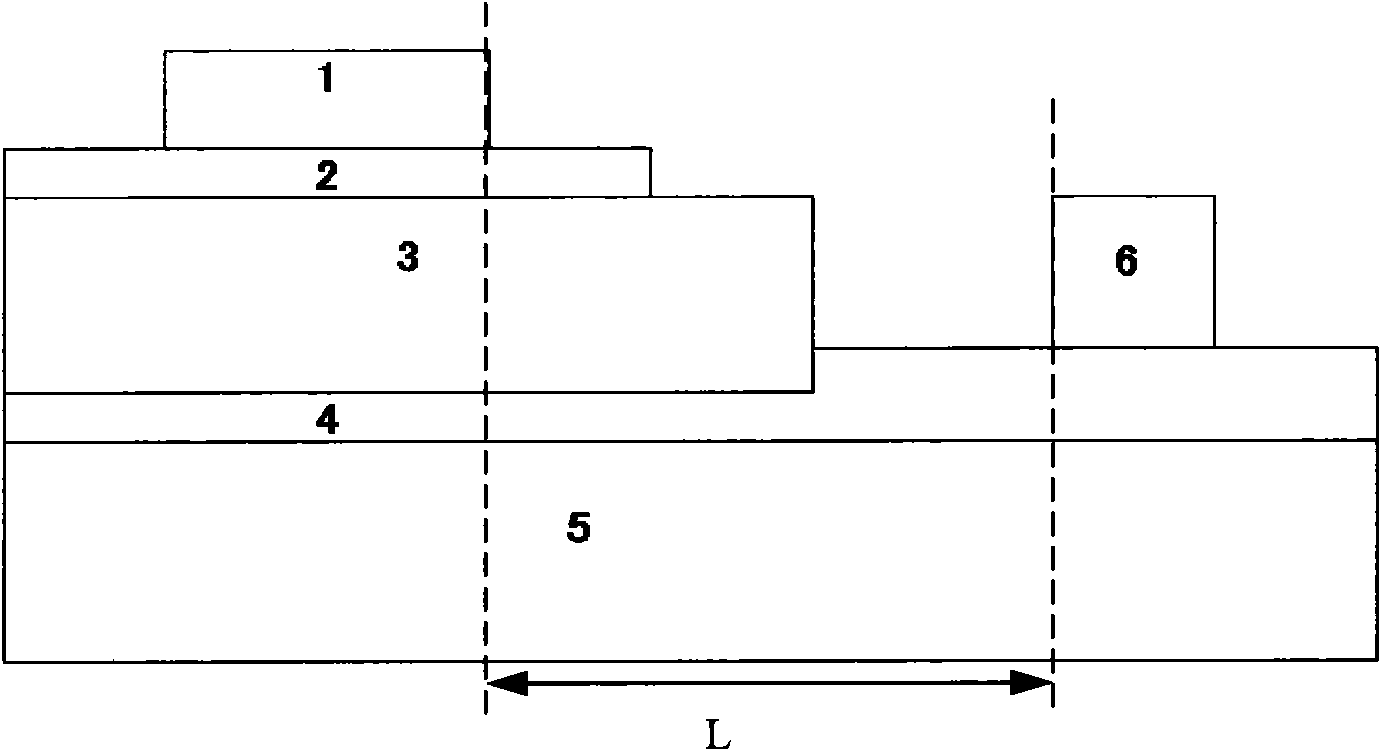

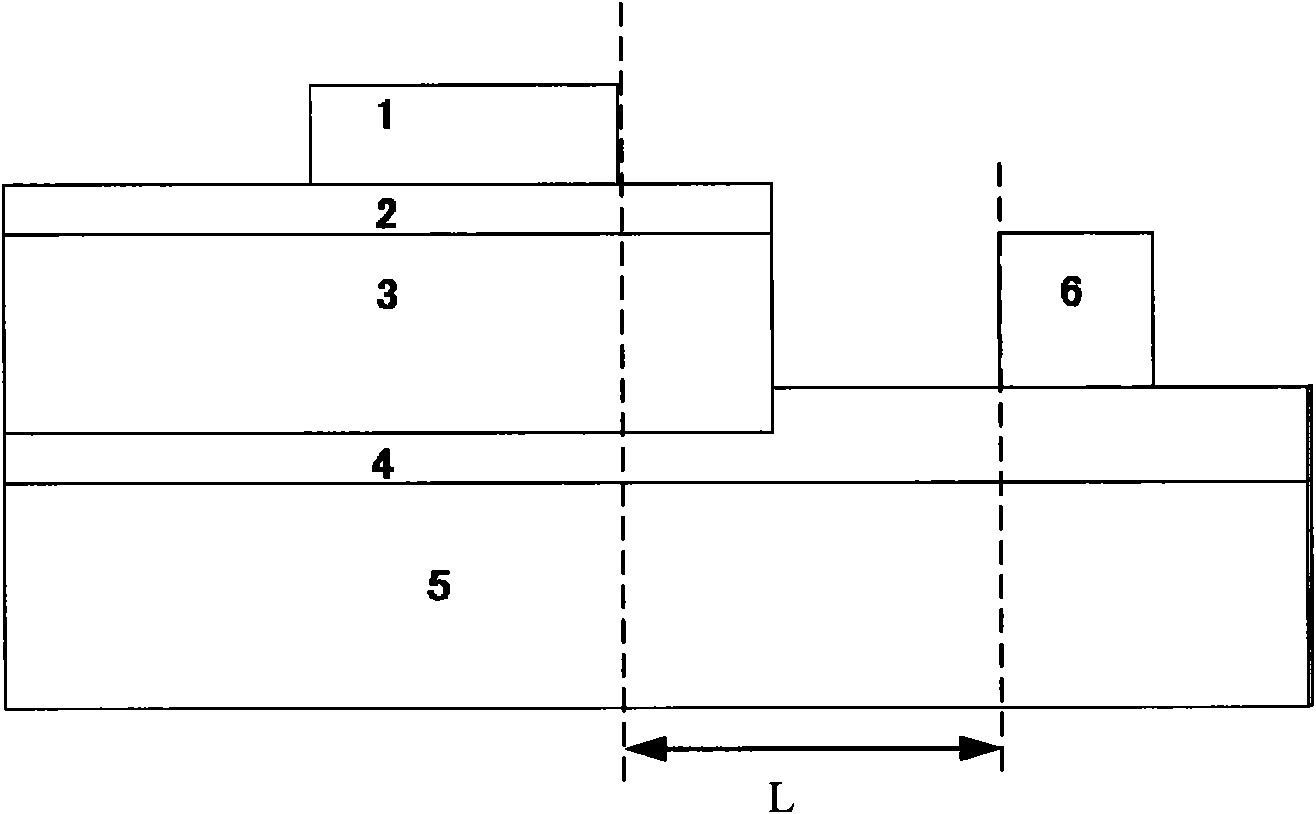

[0033] The present invention will be described in further detail below in conjunction with the accompanying drawings and embodiments.

[0034] As shown in Figure 5, the present invention provides a kind of manufacturing method of SONOS memory, and its processing step is:

[0035] 1) on silicon substrate 5, SiO2 is fully deposited to form SiO2 layer 4, see Figure 5A ; For devices with an operating voltage of less than 15V, the thickness is 50-250 angstroms, and the growth method is usually thermal growth or PVD, CVD deposition.

[0036] 2) Photolithography removes the SiO2 in the SONOS tube area, and forms a SiO2 protective layer (anti-reflection barrier layer 8 and photoresist 7) in other areas (ie, the common transistor area), see Figure 5B ; Etching generally uses wet etching containing HF liquid.

[0037] 3) Fully deposit ONO three-layer film (Oxide-Nitride-Oxide, insulating oxide layer 2-nitride layer 3-tunnel oxide layer 4), see Figure 5C ; For devices with an ope...

PUM

| Property | Measurement | Unit |

|---|---|---|

| thickness | aaaaa | aaaaa |

Abstract

Description

Claims

Application Information

Login to View More

Login to View More