Patents

Literature

76results about How to "Small unit area" patented technology

Efficacy Topic

Property

Owner

Technical Advancement

Application Domain

Technology Topic

Technology Field Word

Patent Country/Region

Patent Type

Patent Status

Application Year

Inventor

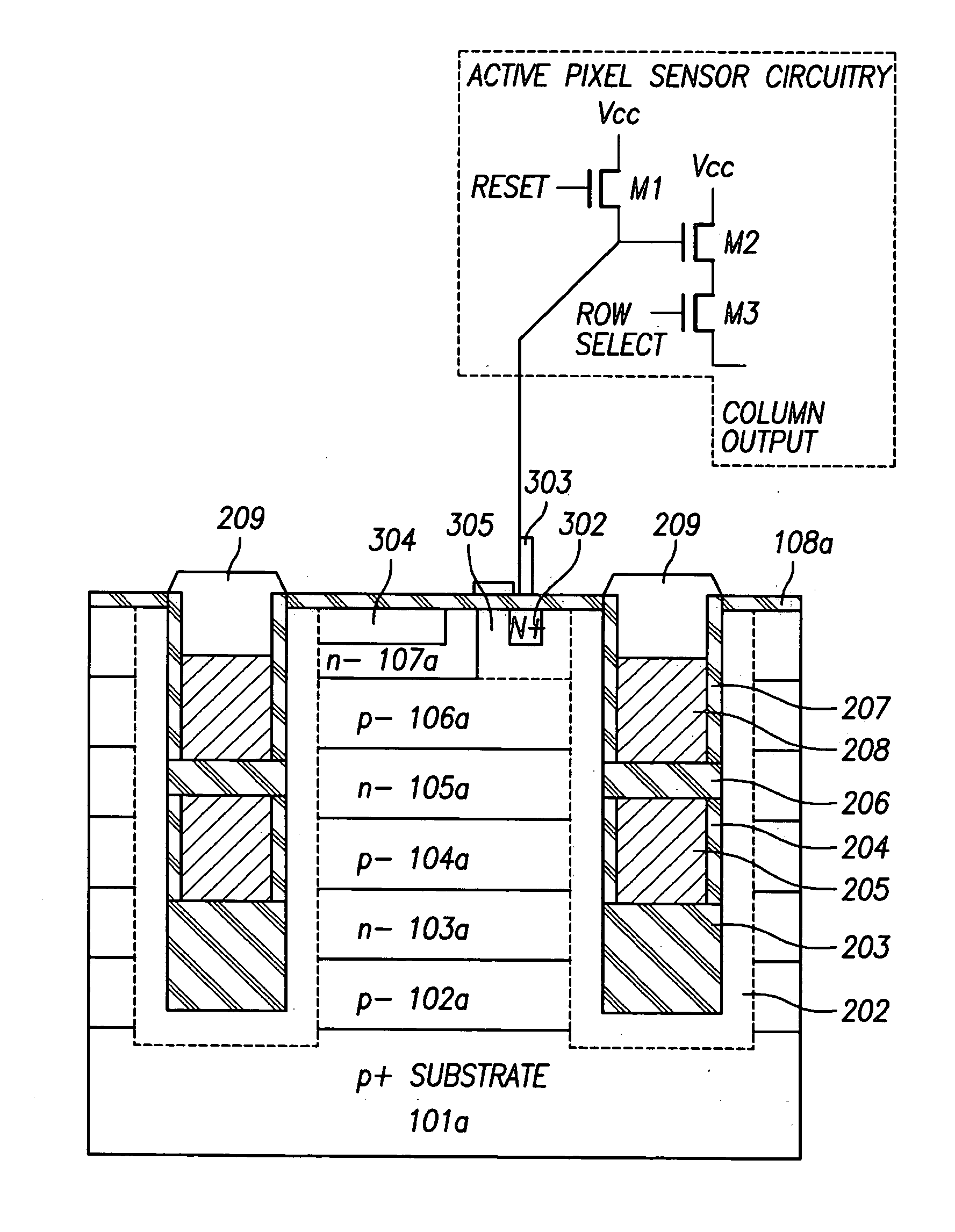

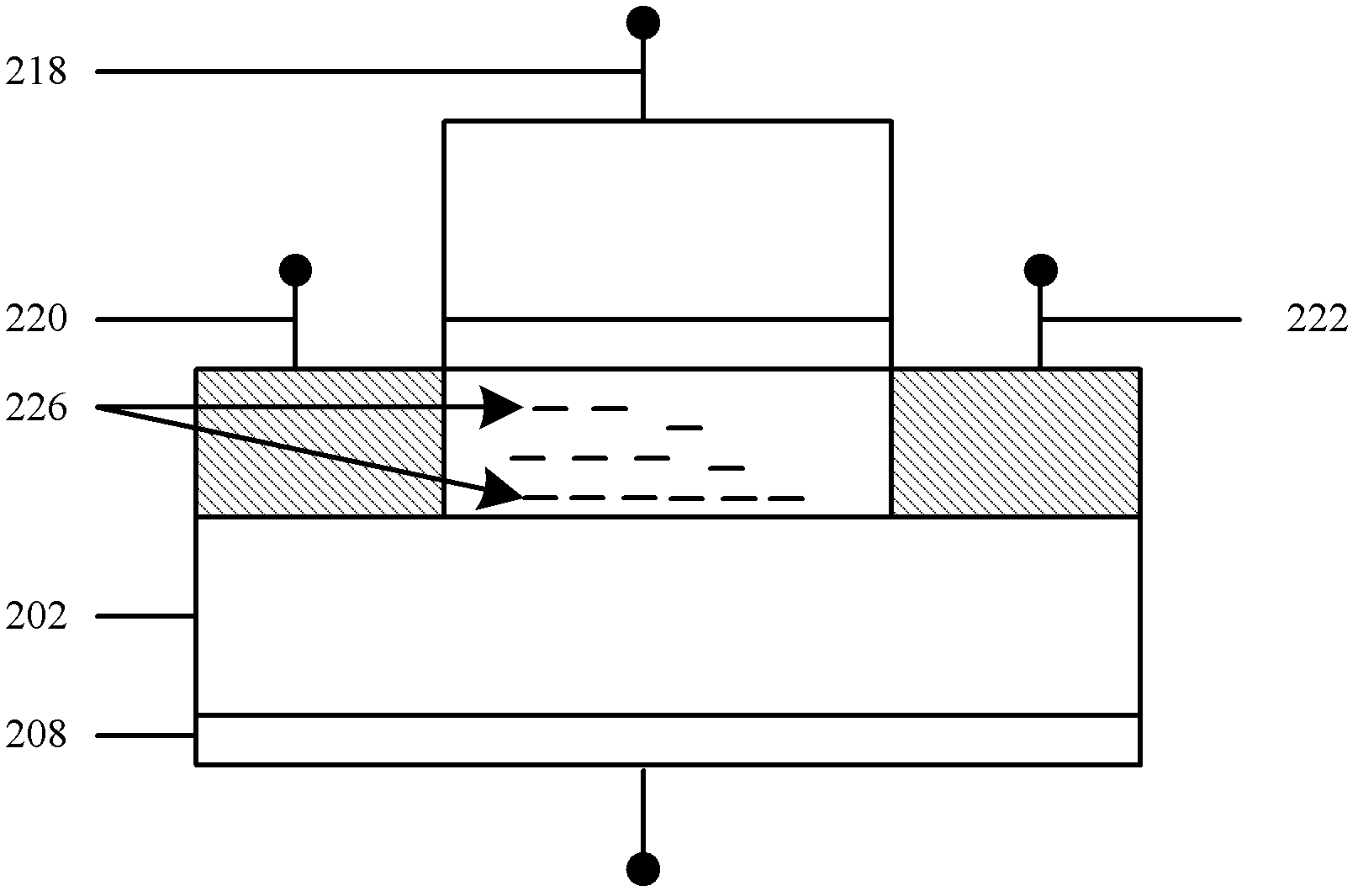

Vertical image sensor and method for manufacturing the same

InactiveUS20070131987A1Simple processIncrease the aperture ratioTelevision system detailsSolid-state devicesIon implantationSemiconductor

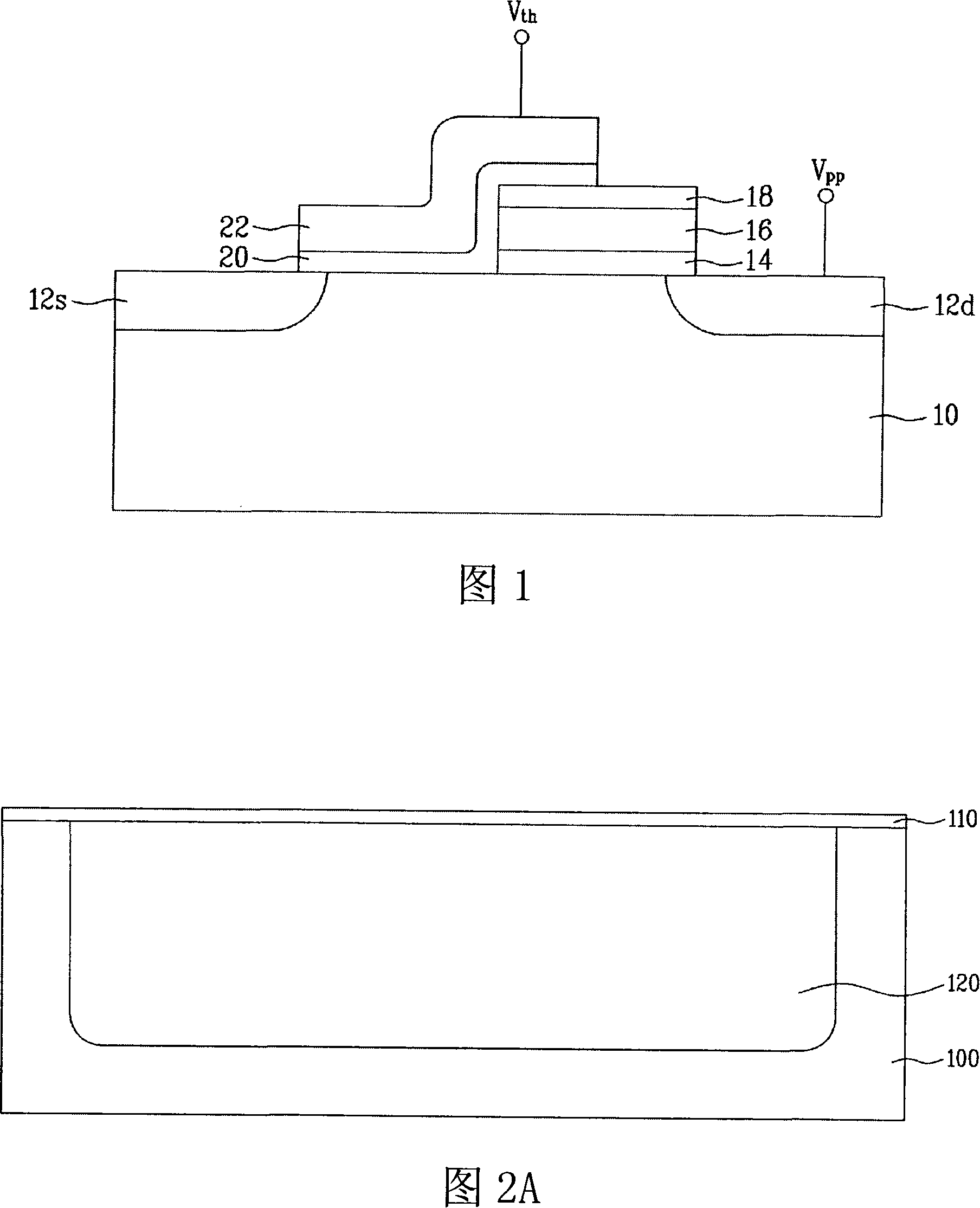

Disclosed are a vertical color filter detector group (image sensor) and a method for manufacturing the same, capable of simplifying a manufacturing process by reducing the number of ion implantations and masks for connecting a green sensitive layer and a red sensitive layer to a sensor on a surface of a silicon substrate. The image sensor includes a semiconductor substrate on which first and second conductive type silicon layers are stacked, and having at least two second conductive type regions at different depths from the semiconductor surface, a trench having a bottom lower than a first region farthest away from the semiconductor surface, to set a peripheral border area of a unit pixel, an insulating layer in the trench in contact with an interfacial surface between the semiconductor and the trench, a channel area in an active area between the first and second regions without contacting the interfacial surface between the semiconductor and the trench, and a transfer gate in the insulating layer.

Owner:DONGBU ELECTRONICS CO LTD

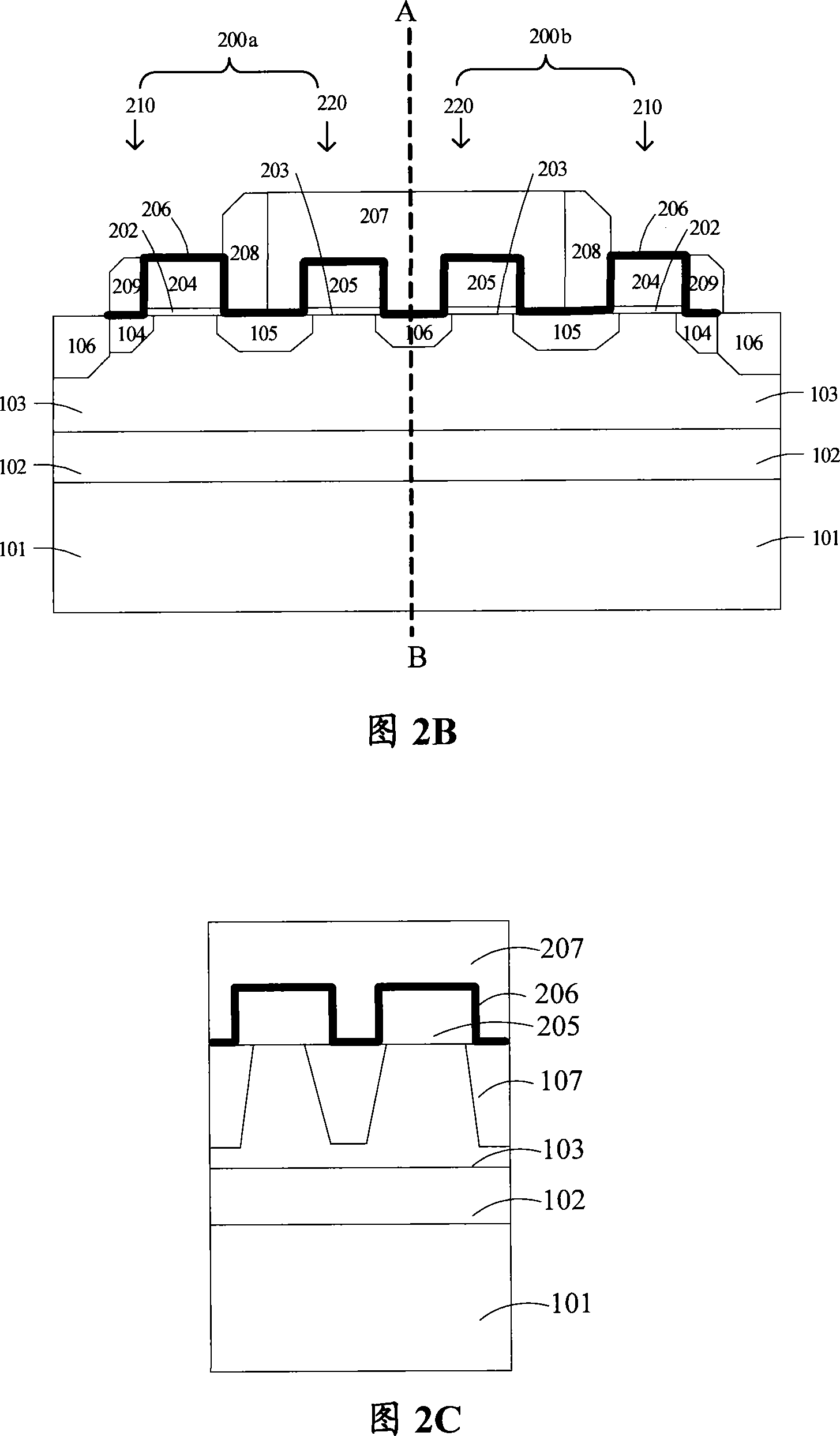

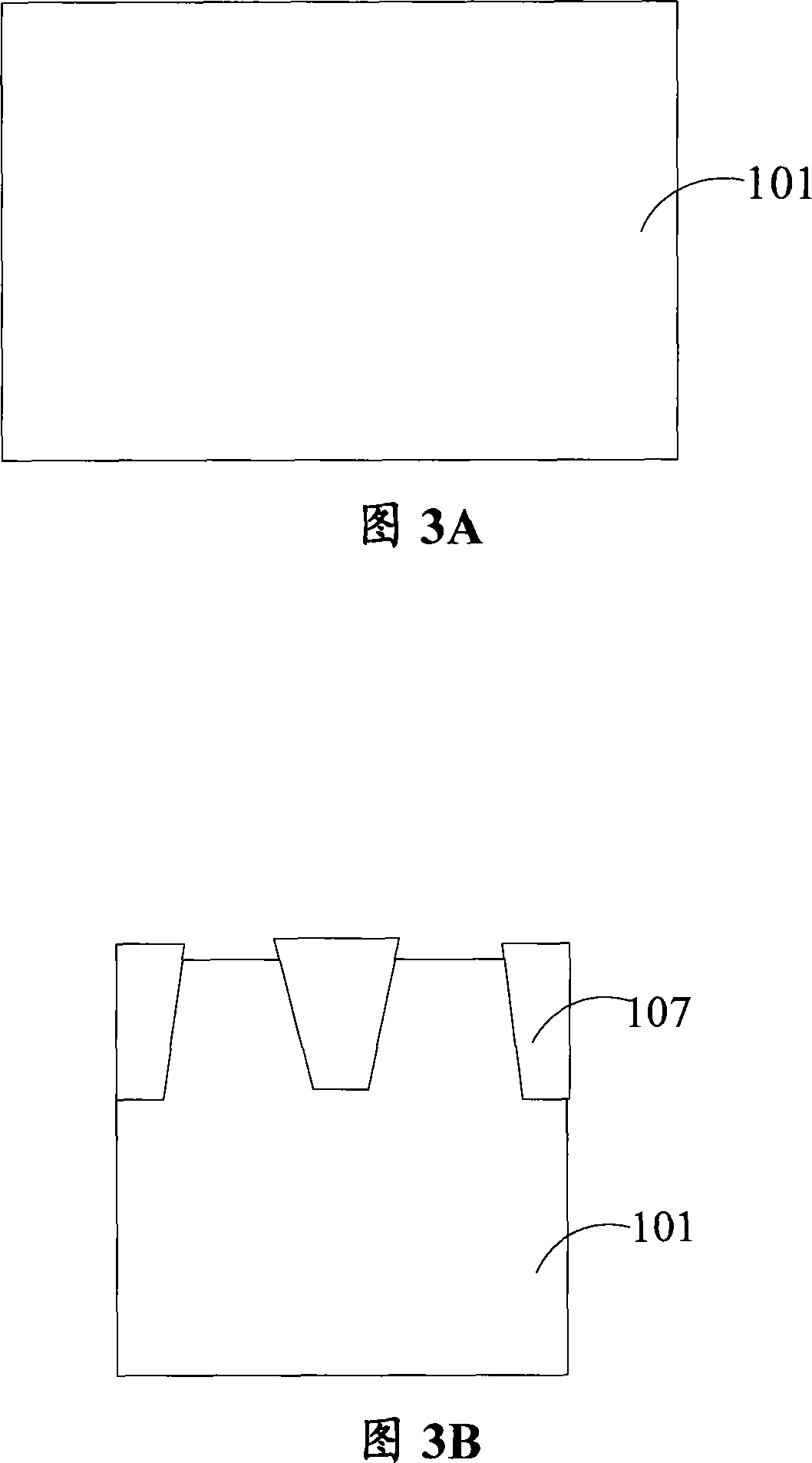

Semi-conductor memory device and manufacturing method thereof

InactiveCN101154666AIncrease coupling capacitanceAvoid areaSolid-state devicesSemiconductor/solid-state device manufacturingCapacitanceCoupling

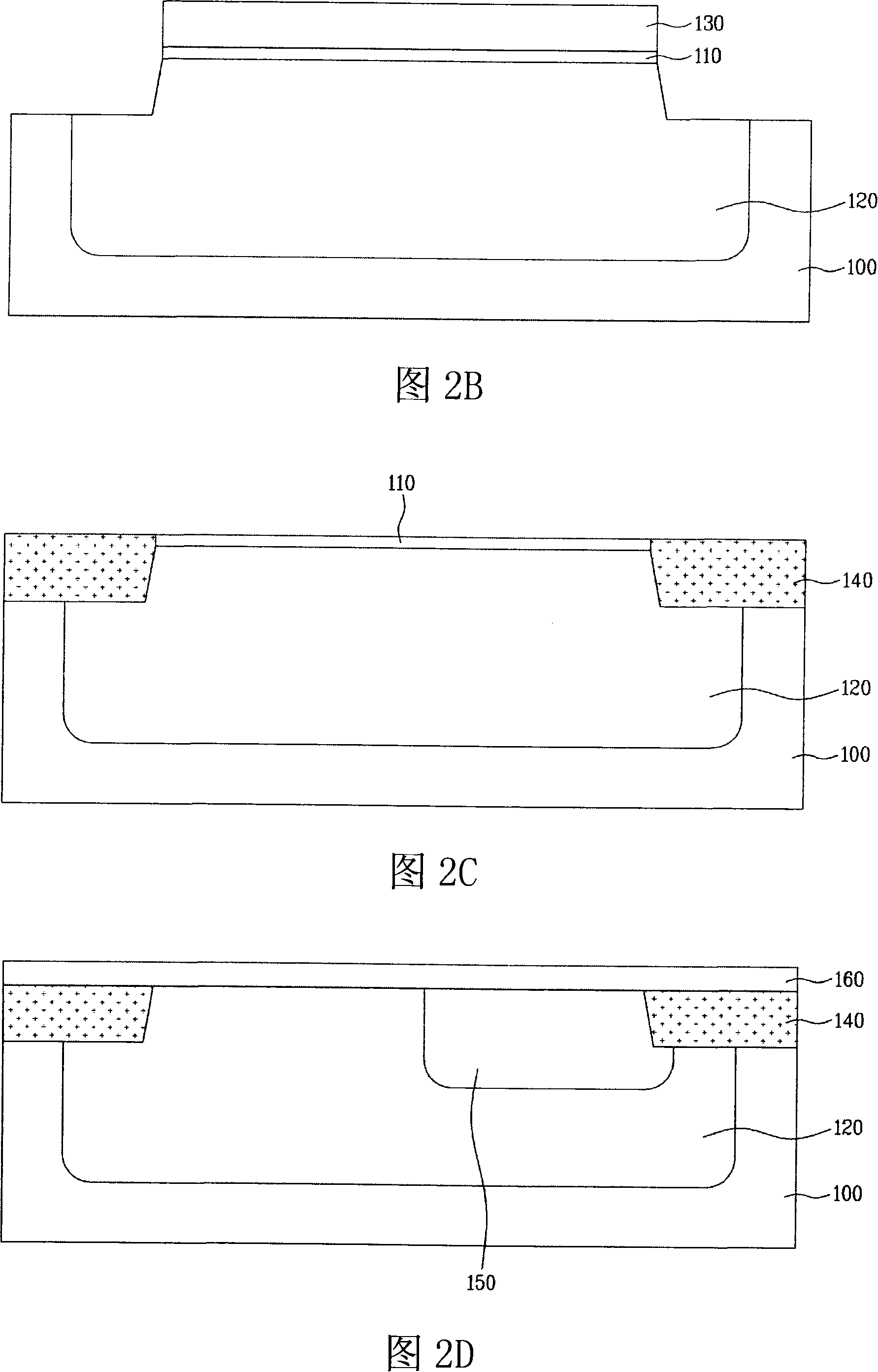

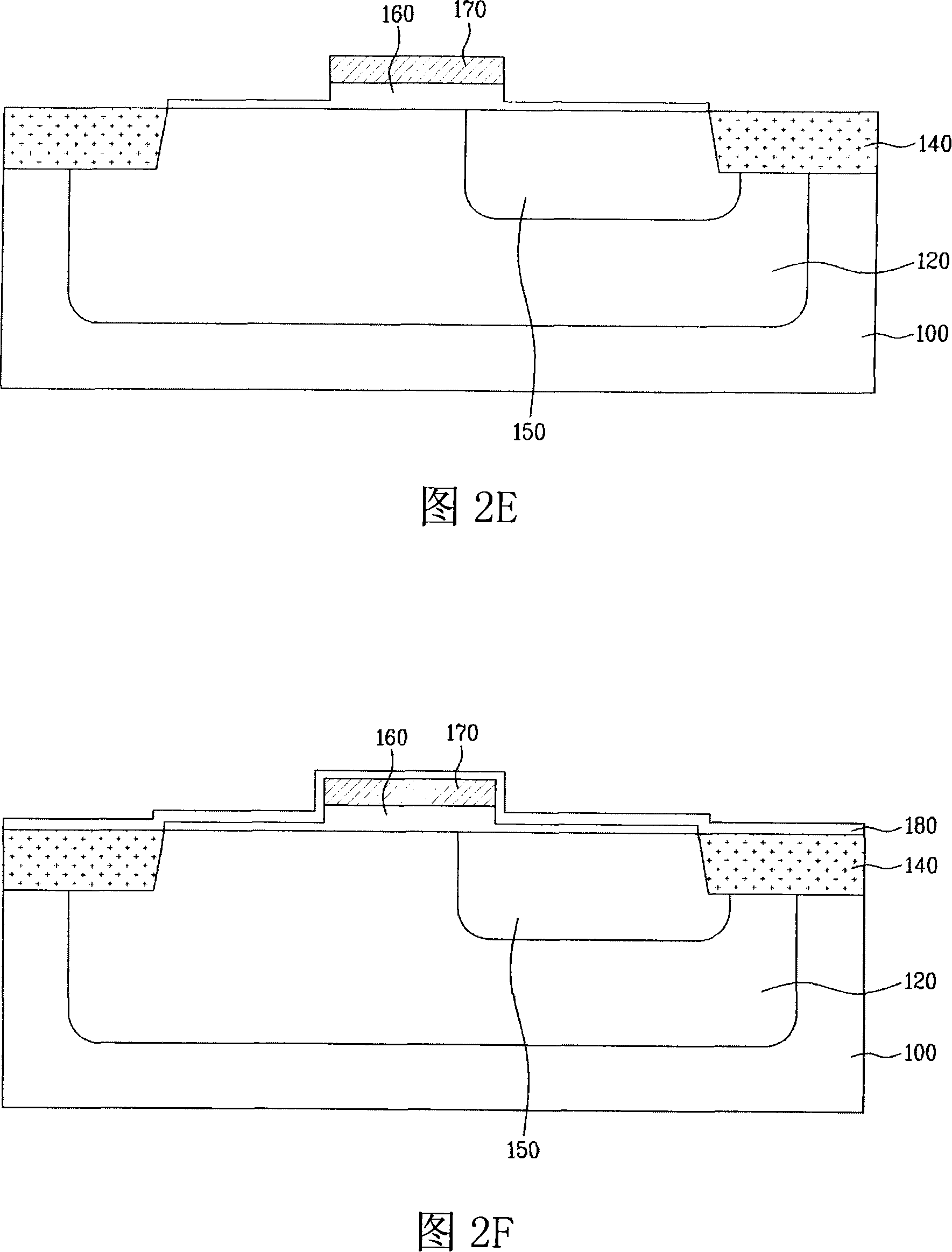

The invention provides a semiconductor memory device, comprising at least one memory unit pair wherein, each memory unit comprises a floating gate transistor and a selection transistor; the two floating gate transistor of the memory unit pair comprise a common source, two drains and two floating gates, wherein, the two floating gates have a common control gate; with voltage applied on the control gate, an conducting channel formed inside a semiconductor substrate connects the common source and the corresponding drains electrically. Accordingly, the invention provides an arrangement of and a method for manufacturing the semiconductor memory device, wherein, the common control gate controls the floating gates at the same time, which reduces the unit area and improves the memory density; meanwhile, common control gate is in complete contact with an interlayer insulated layer, which improves the floating gate coupling capacitor as well as the memory efficiency.

Owner:SEMICON MFG INT (SHANGHAI) CORP

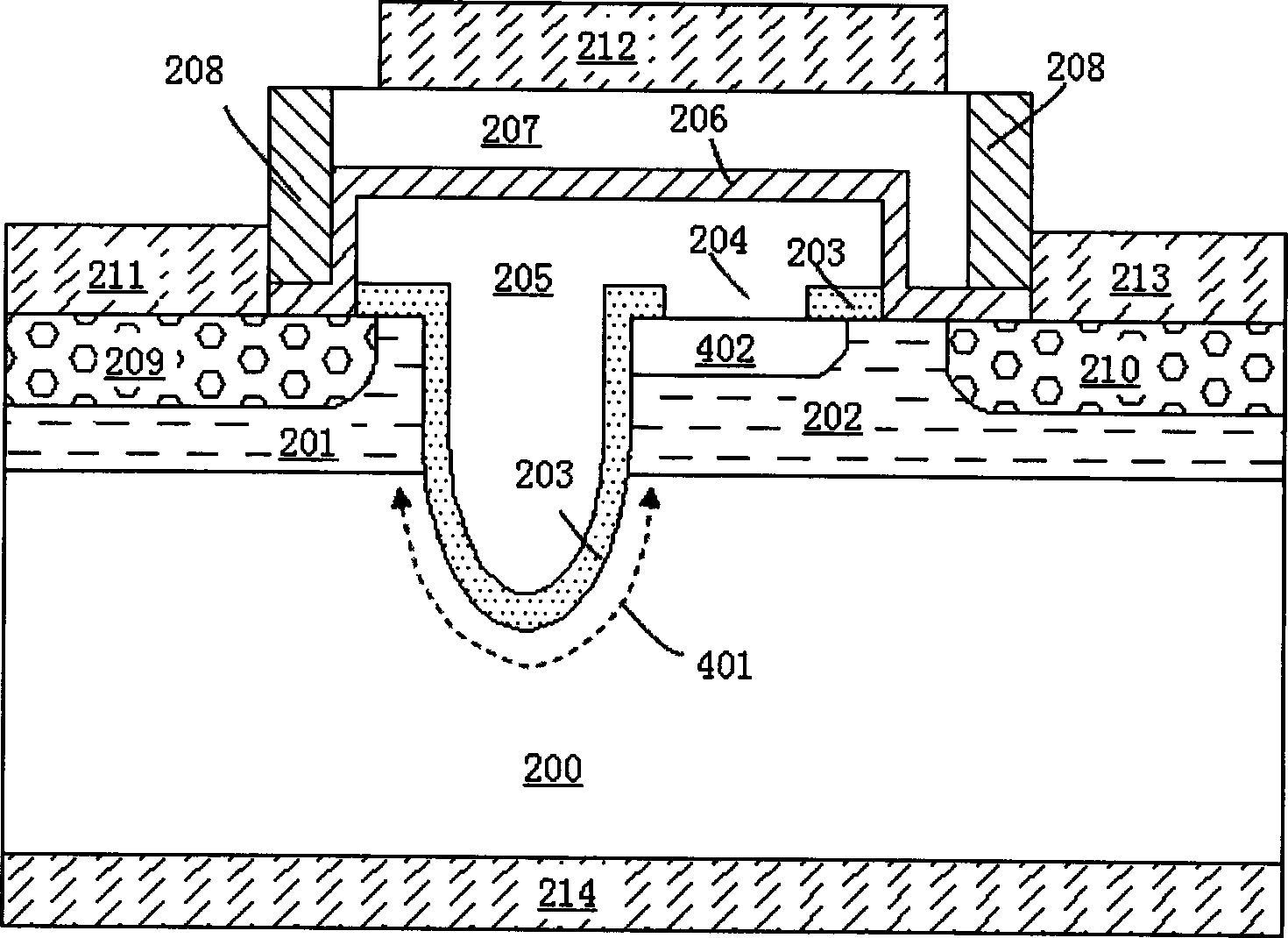

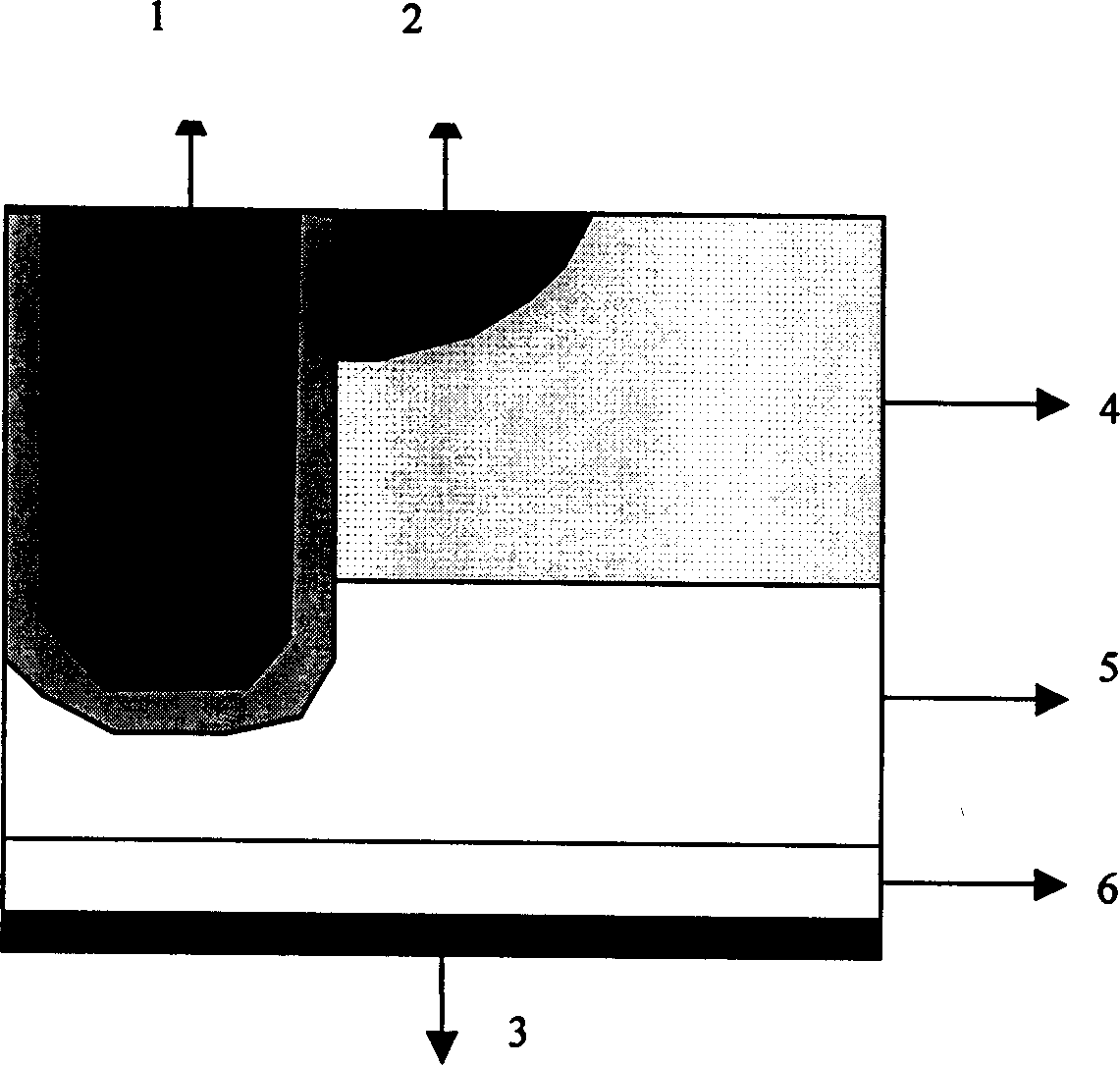

U-shaped trench type semiconductor device and manufacture method thereof

InactiveCN104103678AHigh densitySmall unit areaSemiconductor/solid-state device manufacturingSemiconductor devicesP–n junctionGate control

The invention pertains to the technical field of semiconductor memories, and specifically relates to a U-shaped trench type semiconductor device which comprises at least one semiconductor substrate, a source region, a drain region, a floating gate, a control gate, a U-shaped trench region and a gate-control p-n junction diode for connecting the floating gate and the drain region. The U-shaped trench type semiconductor device provided in the invention uses the floating gate to store information, and perform charging and discharging on the floating gate through the gate-control p-n junction diode, so advantages of small unit area, high chip density, low operating voltage during data storage and good data rentation capability can be realized.

Owner:SUZHOU ORIENTAL SEMICONDUCTOR CO LTD

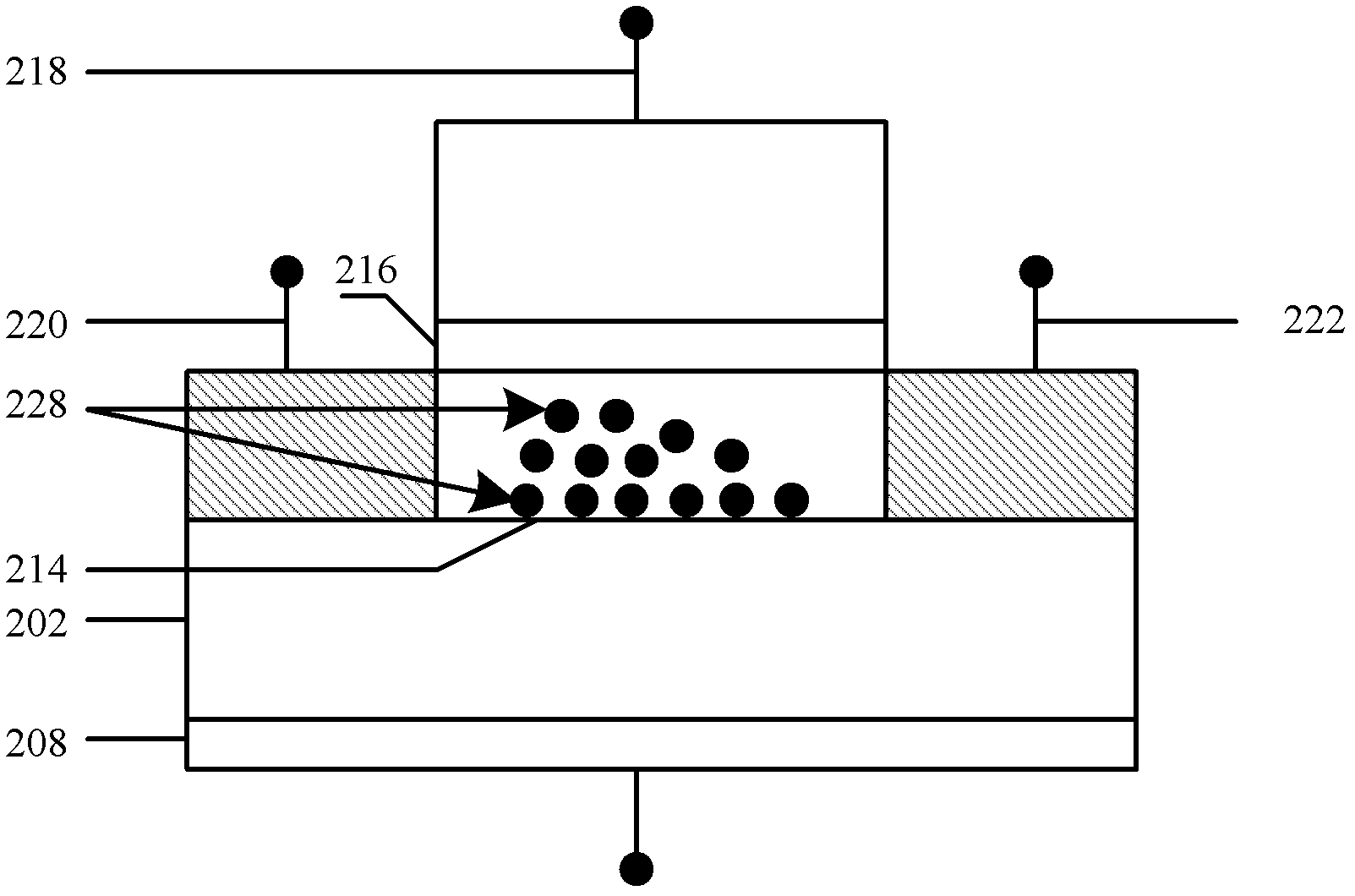

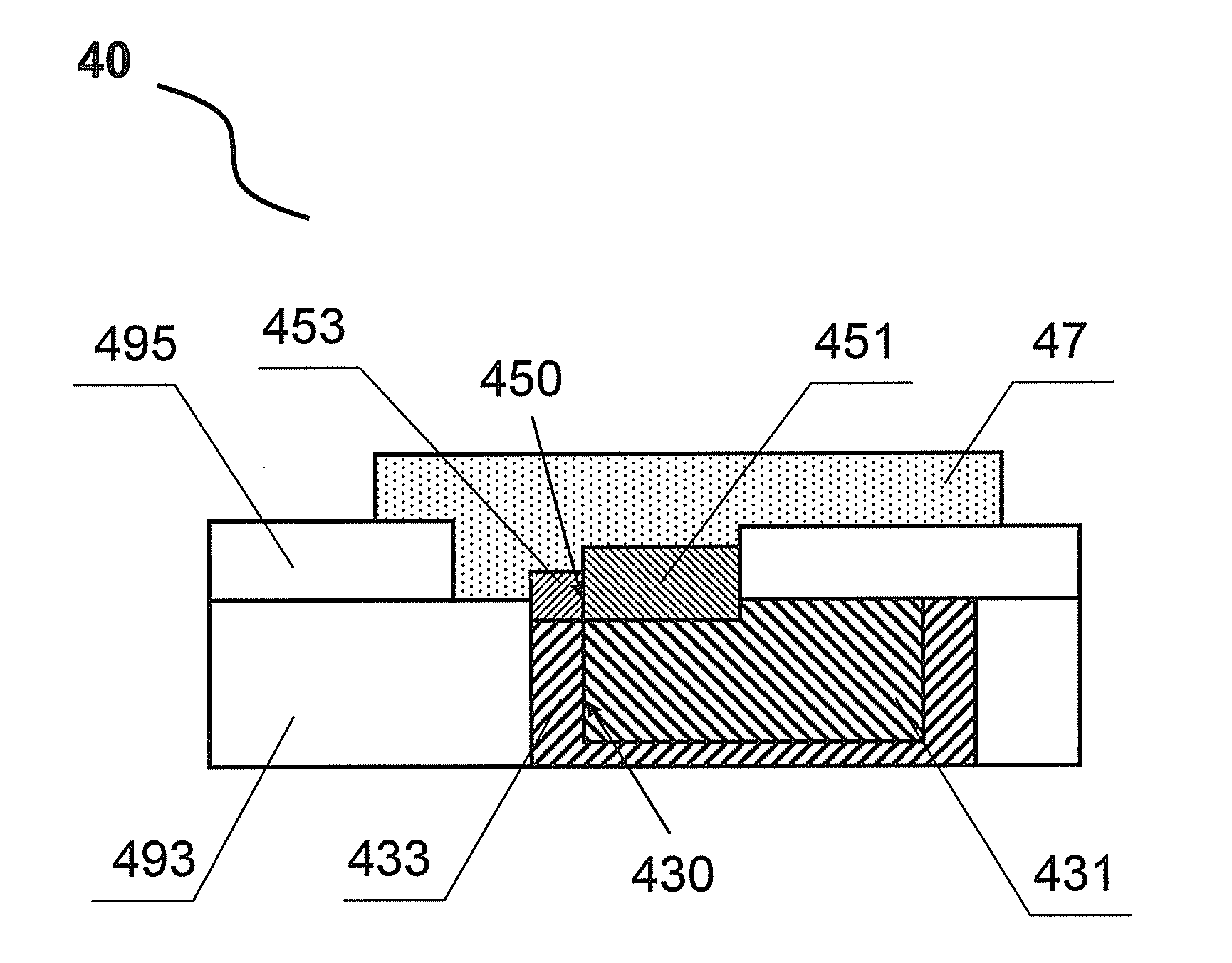

Pressure sensor and manufacturing method thereof

InactiveCN105070823ASmall unit areaHighly integratedFluid pressure measurement using piezo-electric devicesForce measurement using piezo-electric devicesOxide semiconductorSurface electrode

The invention belongs to the technical field of semiconductor sensors, and particularly discloses a pressure sensor and a manufacturing method thereof. The pressure sensor disclosed by the invention comprises at least one field effect transistor and a piezoelectric control gate, wherein the field effect transistor is an N-channel metal oxide semiconductor (NMOS) transistor or a P-channel metal oxide semiconductor (PMOS) transistor; the piezoelectric control gate comprises a piezoelectric film, an upper surface electrode of the piezoelectric film, a lower surface electrode of the piezoelectric film and a connection electrode; and the connection electrode is arranged between a gate of the field effect transistor and the lower surface electrode of the piezoelectric film. The pressure sensor disclosed by the invention is used for sensing a pressure signal, and has the characteristics of being simple in manufacturing process, small in cell area, high in chip integration level, high in sensitivity on pressure and the like.

Owner:FUDAN UNIV

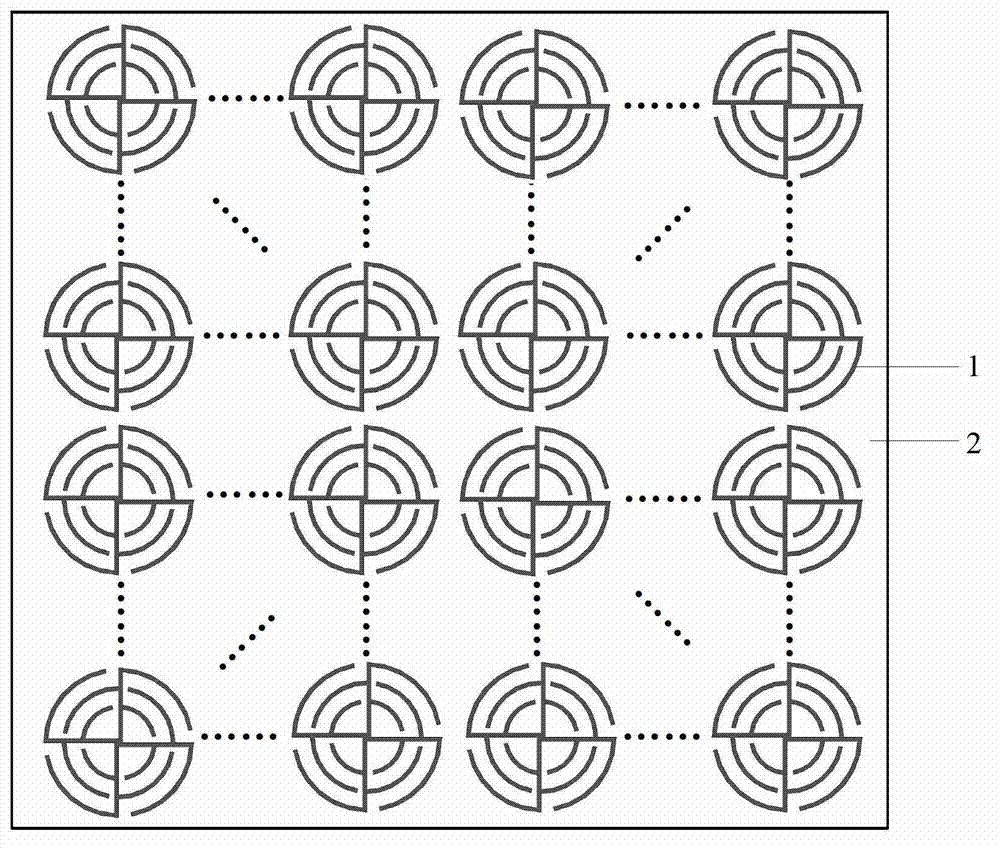

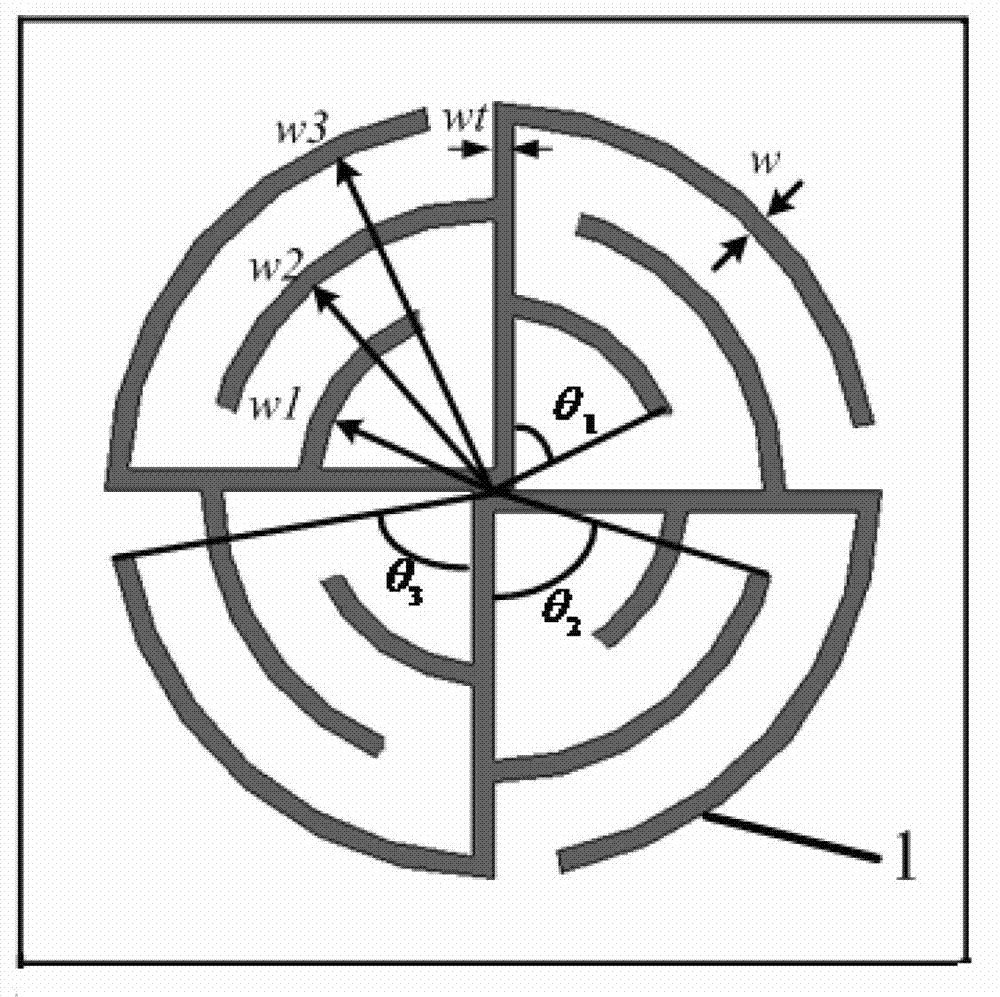

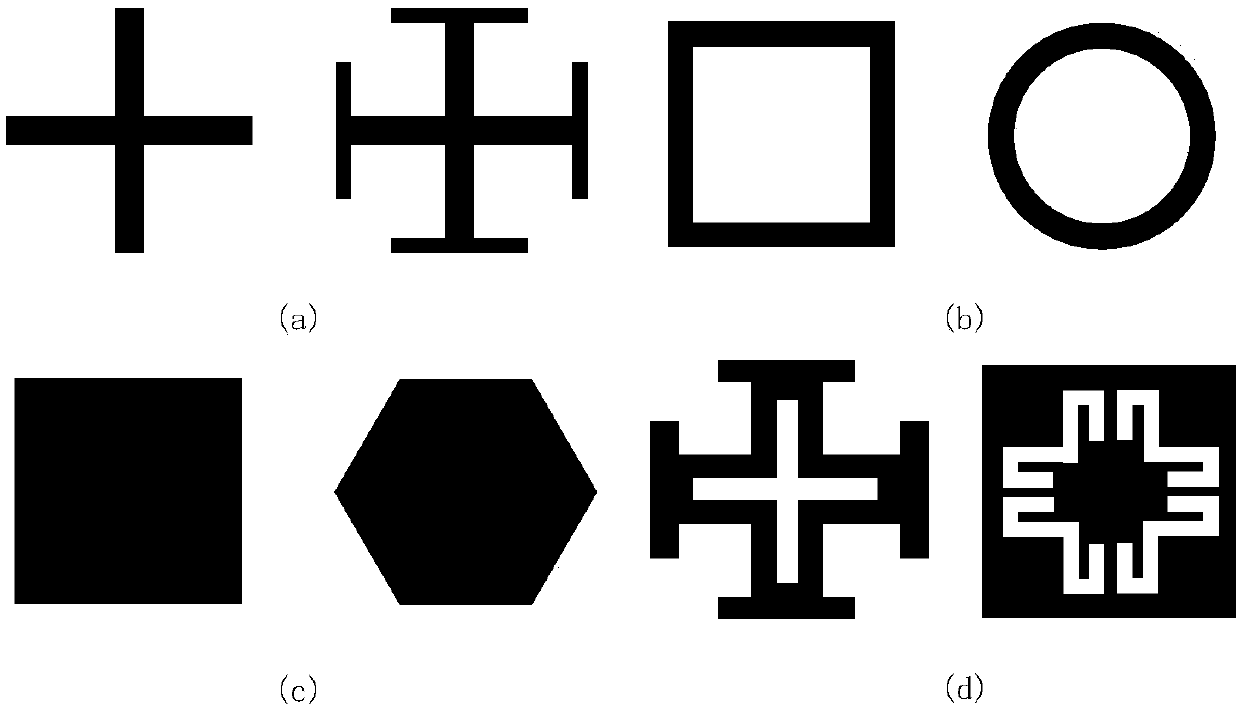

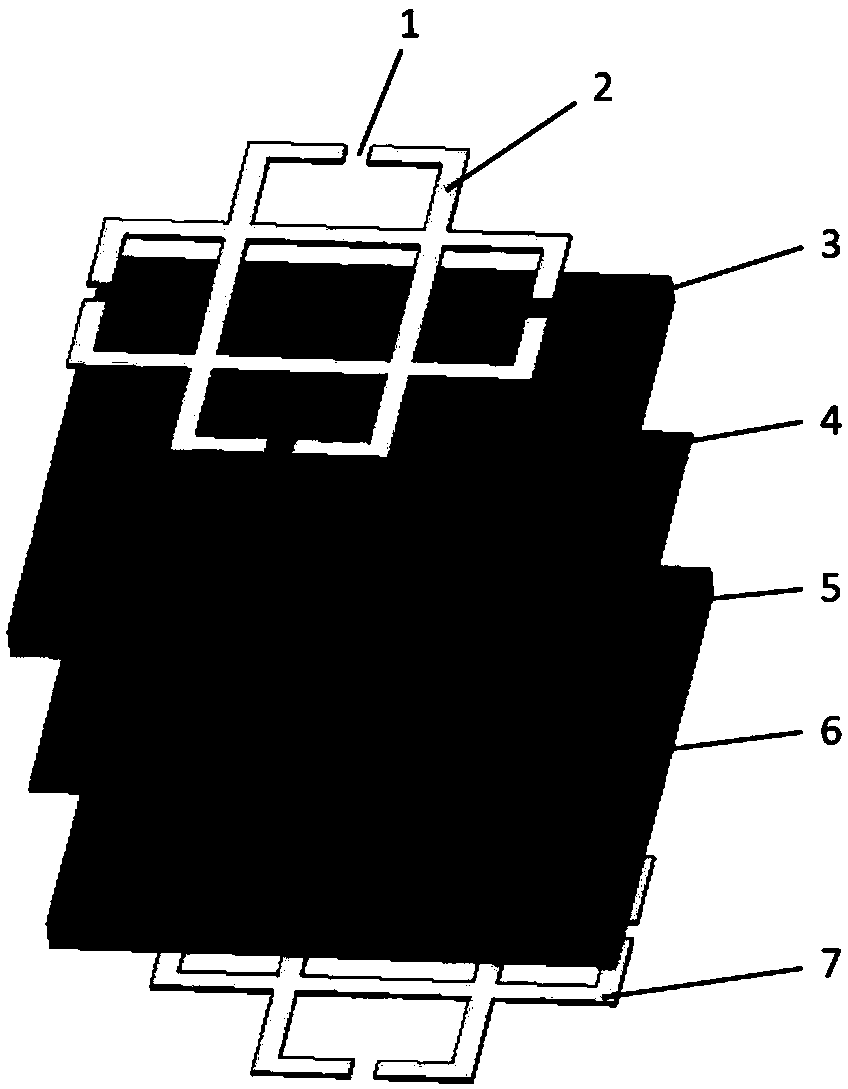

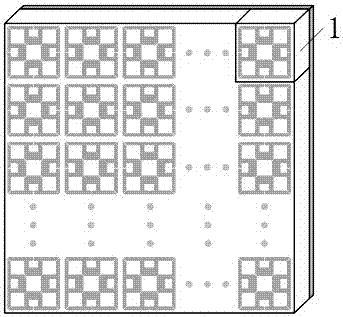

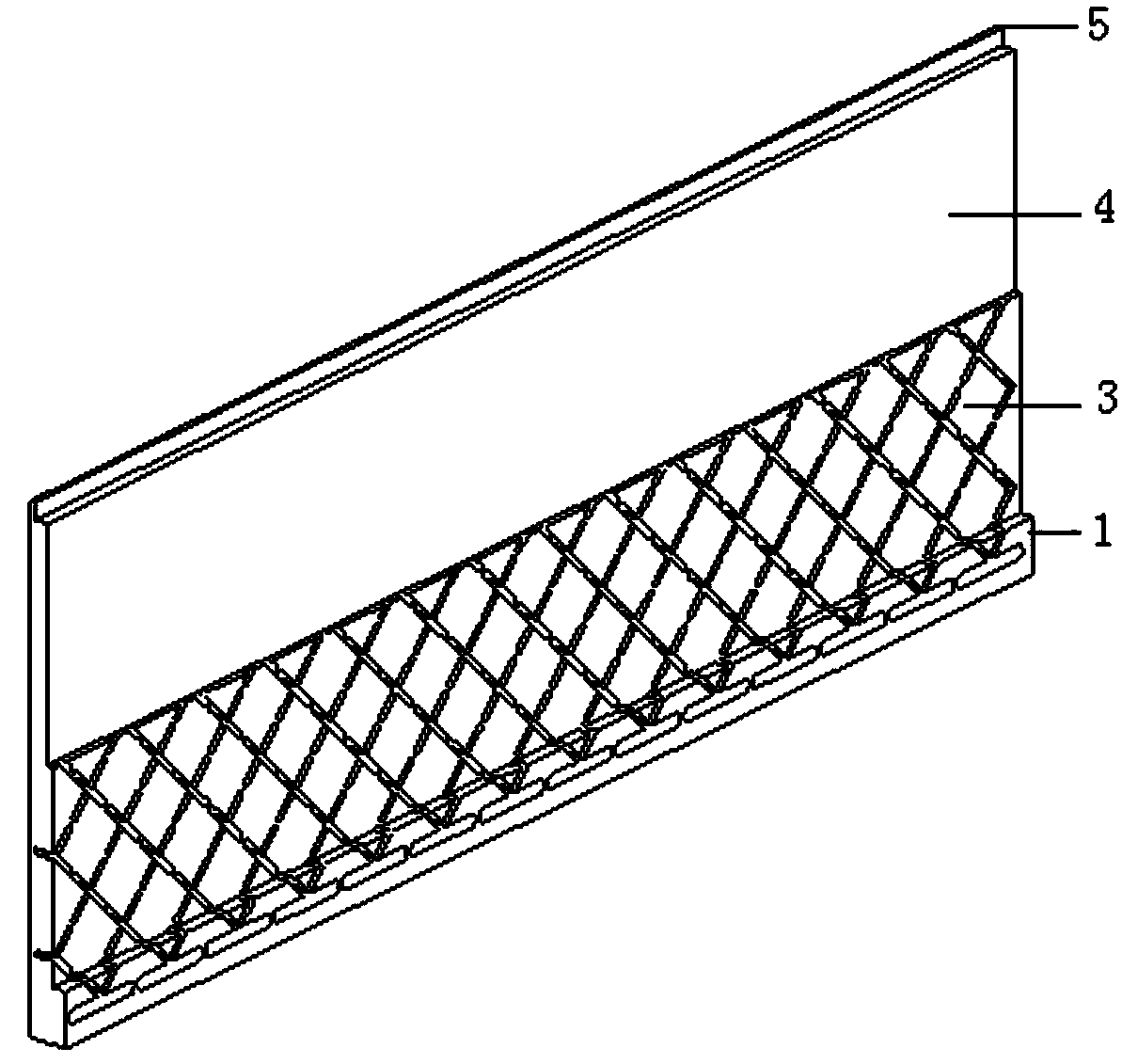

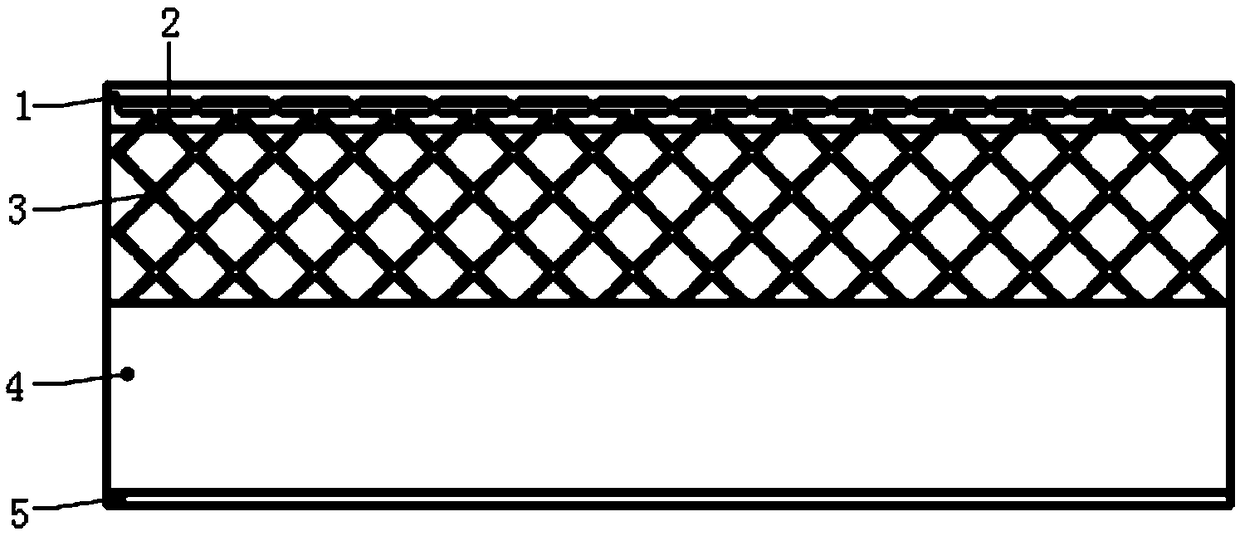

Reflecting plate based on frequency selection surface units

InactiveCN102904063AReduced Scattering Cross SectionAvoid couplingAntennasElectricityScattering cross-section

The invention discloses a reflecting plate based on frequency selection surface units. The reflecting plate is mainly used for solving the problems that an existing reflecting plate is relatively large in size, cannot be applied to antennae with smaller sizes and cannot reduce the antenna radar cross section in a multi-angle manner. The reflecting plate comprises Z frequency selection surface units (1) and a base plate (2), wherein Z is larger than or equal to 4; the Z frequency selection surface unit are uniformly distributed on the surface of the base plate in a rectangular array; each frequency selection surface unit consists of four pasters; each paster (11) comprises a rectangular trunk (111) and n arc-shaped branch knots (112), and the n arc-shaped knot are alternatively arranged on two sides of the rectangular trunk; and the four pasters respectively rotate 90 degrees, 180 degrees and 270 degrees by utilizing the bottom left corners of the pasters as centers, so as to form a crossed distribution structure of the four pasters. According to the reflecting plate, the electric size of each frequency selection surface unit is prolonged, the space is fully utilized, the resonant frequency is reduced, and the reflecting plate can be applied to the antennae with smaller sizes and can be used for reducing the antenna radar scattering cross section in a multi-angle manner.

Owner:XIDIAN UNIV

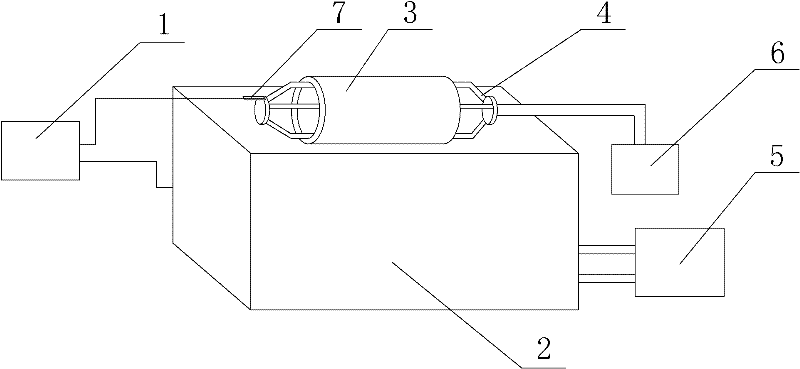

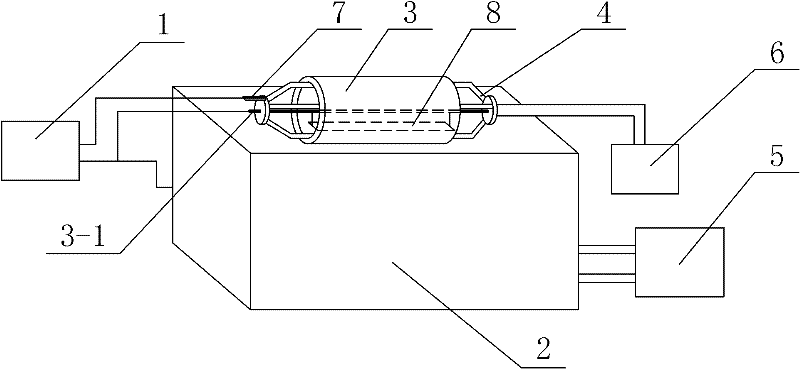

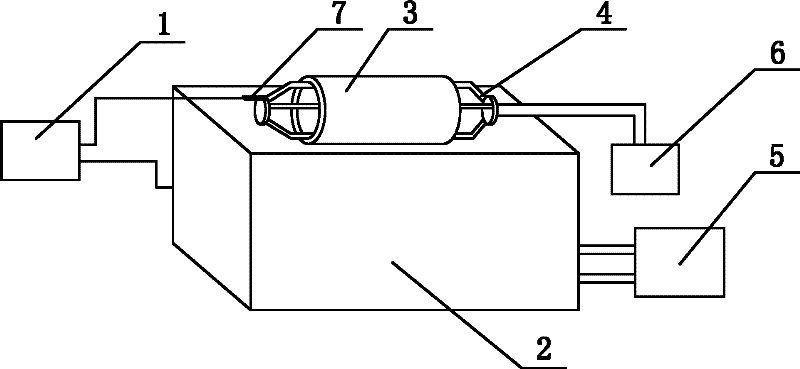

A micro-arc oxidation treatment method and device

InactiveCN102268708ASmall unit areaReduce processing currentAnodisationMicro arc oxidationSteel plates

The invention discloses a microarc oxidation processing method, comprising the following steps of: 1), manufacturing a fixture for supporting a rotary body workpiece; 2), selecting an electrolyte based on the material of the rotary body workpiece, and adding the electrolyte in an electrolyzer; 3), supporting the rotary body workpiece above the electrolyzer by the fixture, and ensuring that a partof the rotary body workpiece is immersed in the electrolyte of the electrolyzer; 4) connecting the fixture with a speed regulating motor, starting the speed regulating motor, and driving the rotary body workpiece to rotate at a constant speed by the fixture; 5), communicating a circulation cooling system with the electrolyzer via a pipeline; and 6), starting a microarc oxidation power supply, andcarrying out microarc oxidation treatment on the rotary body workpiece by adopting the part immersed in the electrolyte, of the rotary body workpiece as an anode, and a stainless steel plate as a cathode. The invention also discloses a device for realizing the method. In the invention, the mode that a part of rotary body workpiece is immersed in the electrolyte is adopted, thus reducing the unit area of the overall workpiece in treatment, greatly reducing the treated current and saving energy.

Owner:CHANGAN UNIV

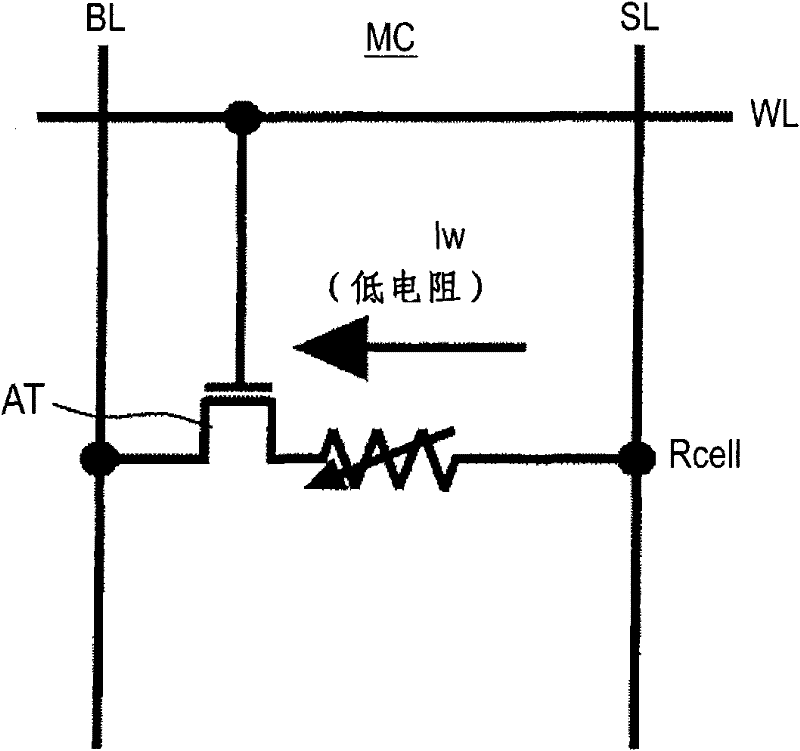

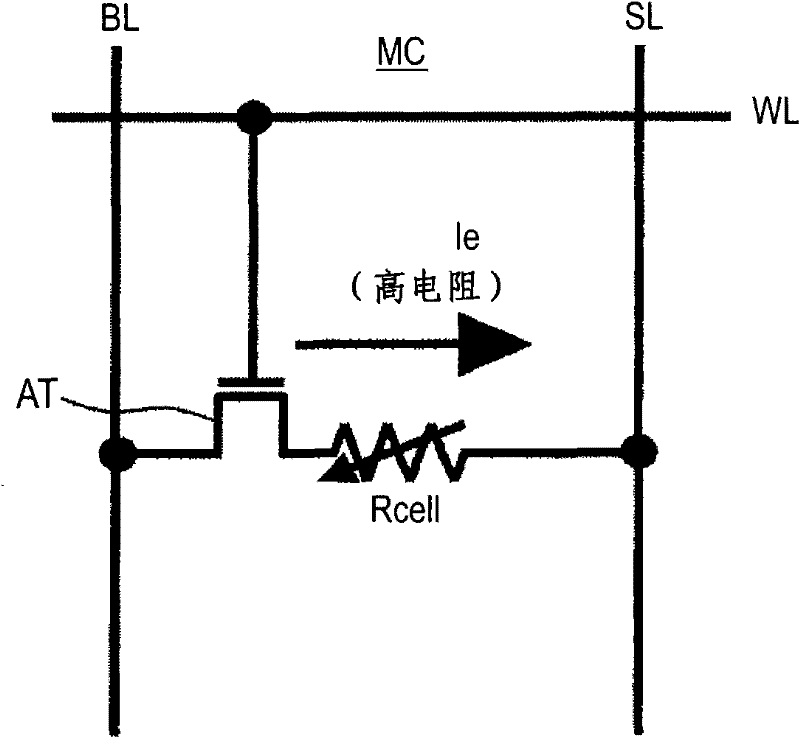

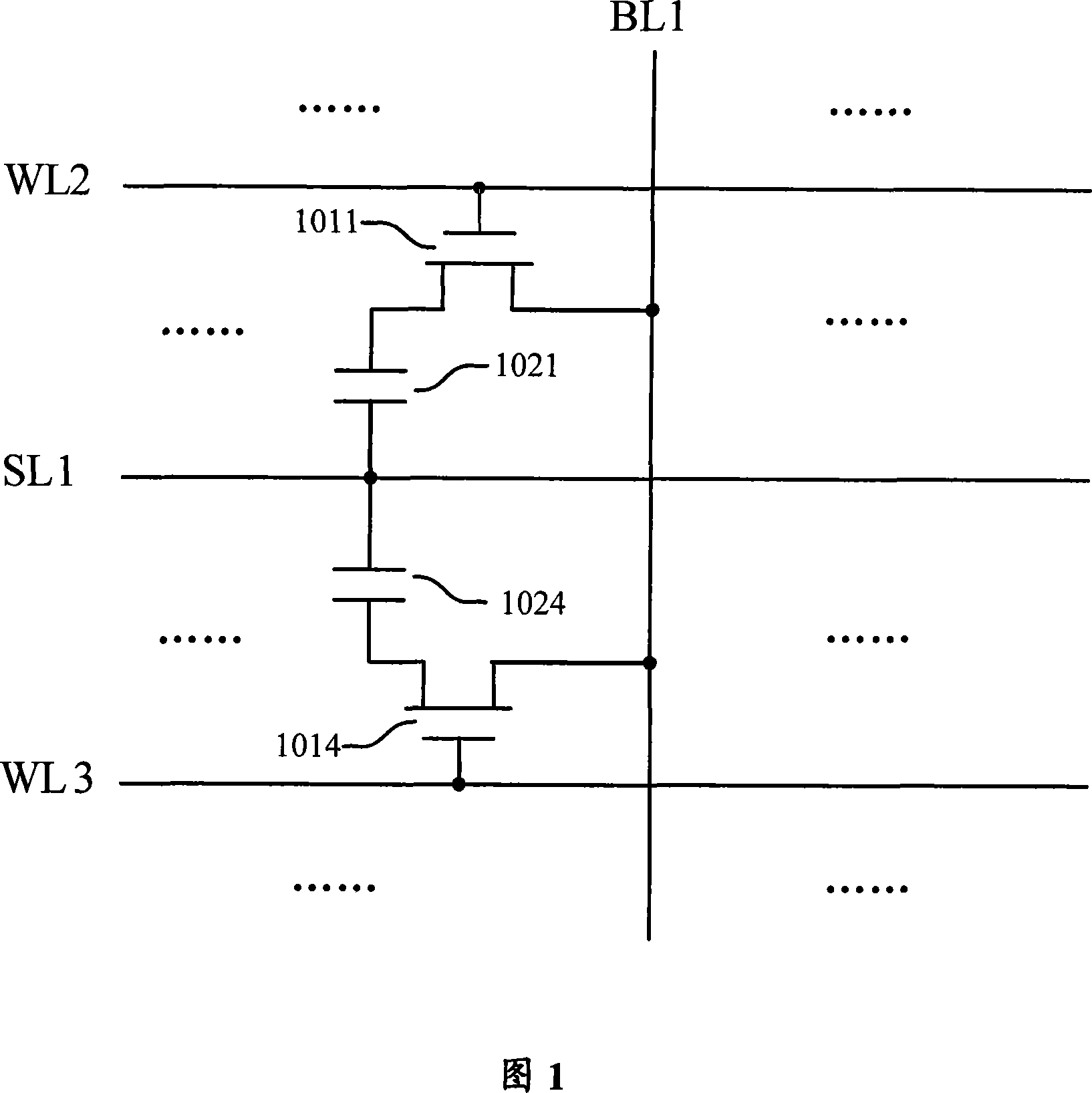

Resistance random access change memory device

InactiveCN102332294ASmall unit areaReduce yieldSolid-state devicesDigital storageResistive elementBit plane

A resistance random access change memory device includes: a memory cell array in which plural memory cells having current paths with series-connected access transistors and variable resistive elements are two-dimensionally arranged; plural bit lines that connect one ends of the current paths; plural source lines that connect the other ends of the current paths; and plural word lines that control conduction and non-conduction of the access transistors, wherein bit line contacts are shared between two memory cells to which the word lines are adjacently provided, and pairs of memory cells are formed, all of the pairs of memory cells connected to the adjacent two bit lines are connected to the corresponding source lines via individual source line contacts, and the source lines are formed by a wiring layer upper than that of the bit lines with a larger pitch than that of the bit lines.

Owner:SONY CORP

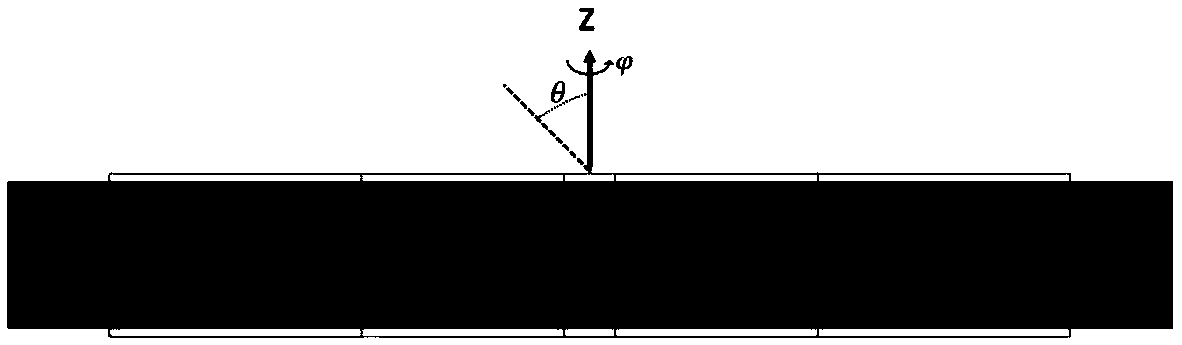

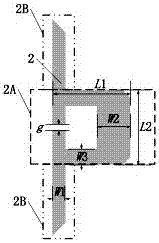

Miniaturized frequency selection surface based on double-opening resonance ring

ActiveCN109616724AGood spatial filteringCompatible with miniaturizationWaveguide type devicesTransmission zerosCoupling

The invention discloses a miniaturized frequency selection surface based on a double-opening resonance ring. A band-pass effect is formed through the combined action of the double-opening resonance ring and a middle coupling aperture. When electromagnetic wave is irradiated to the frequency selection surface, resonance is caused by the opening resonance ring. The frequency selection characteristicof the opening resonance ring is utilized, so that a high spatial filtering function is achieved, meanwhile, the miniaturization characteristic is realized; compared with a common frequency selectionsurface, the cell area is greatly reduced, and the size of the whole circuit unit is only 0.3lambda 0*0.3lambda 0; meanwhile, by virtue of mutual coupling between the opening gap of the resonance ring and an interlayer coupling window, a good out-of-band rejection effect is achieved; and a transmission zero point is arranged on each of the two sides of the band, so that the rectangular coefficient of the circuit is greatly improved. A symmetrical circuit structure is adopted, so that the structure is simple, and machining is easy; and meanwhile, the whole circuit is quite high in stability around the incident angle theta and a formula which is as shown in the specification, so that the practical value is increased.

Owner:四川众为创通科技有限公司

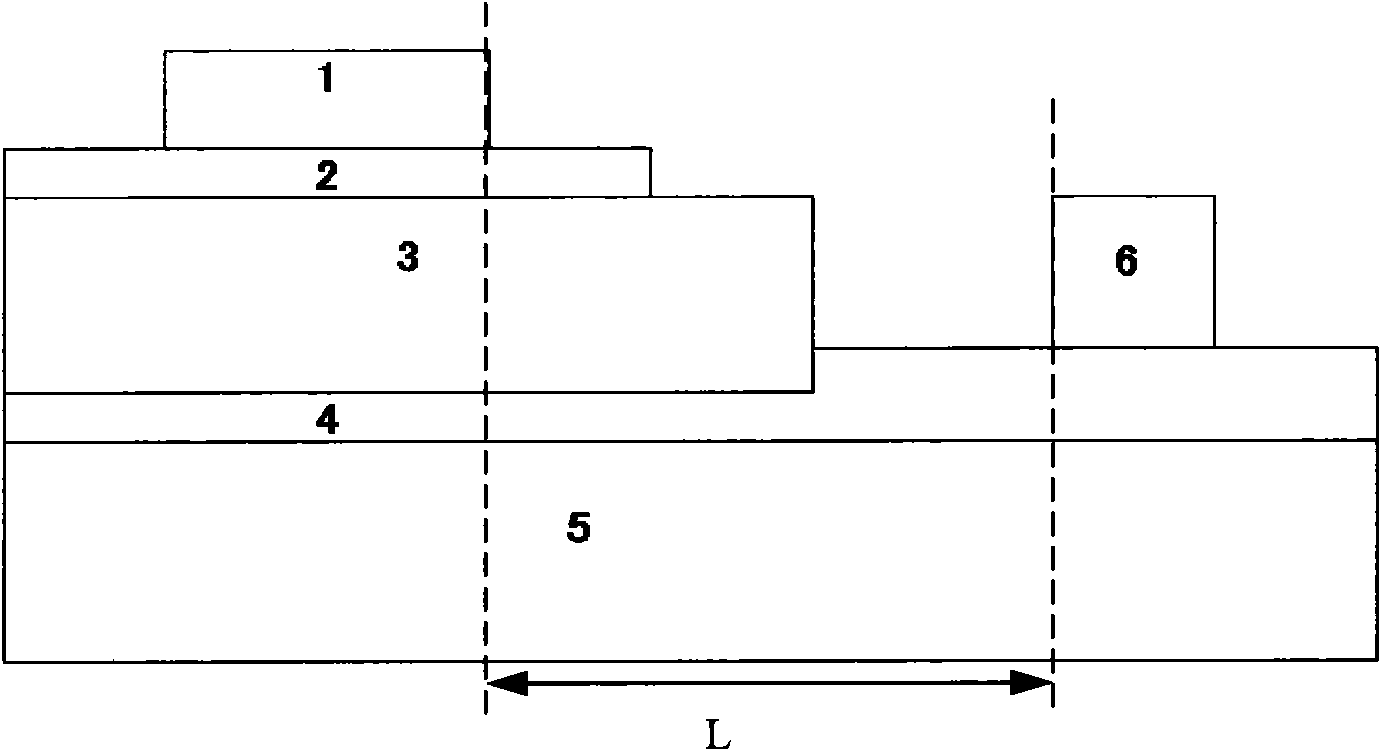

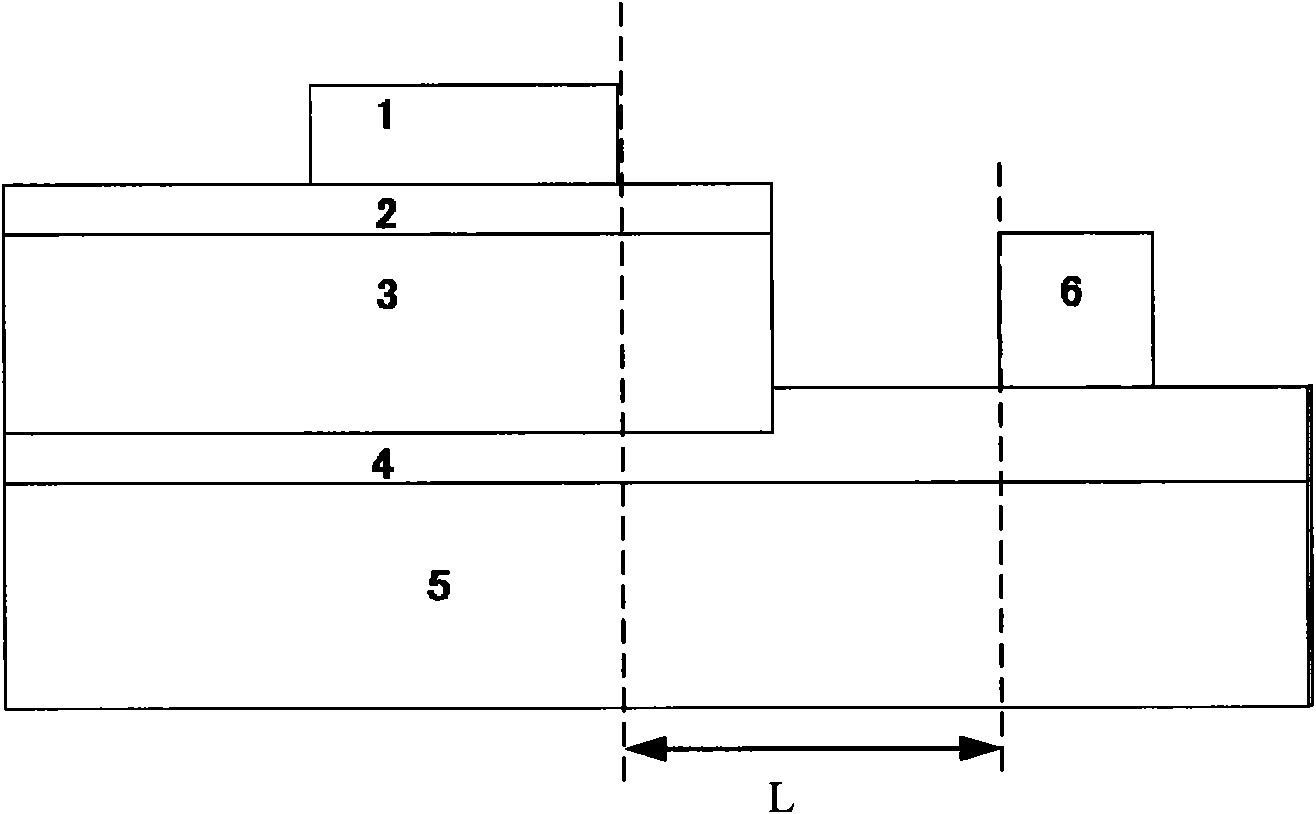

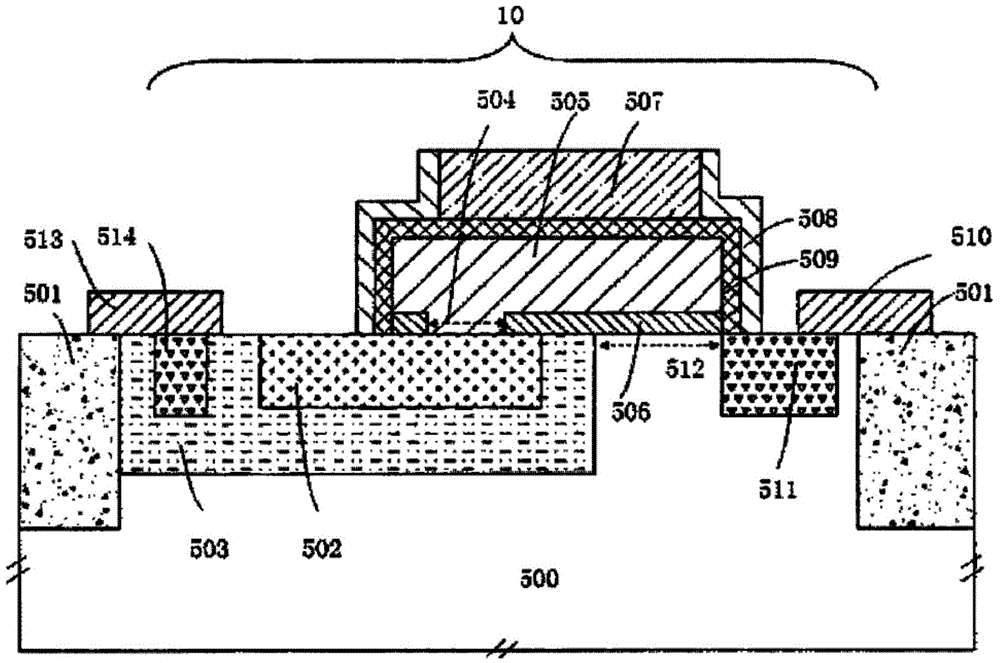

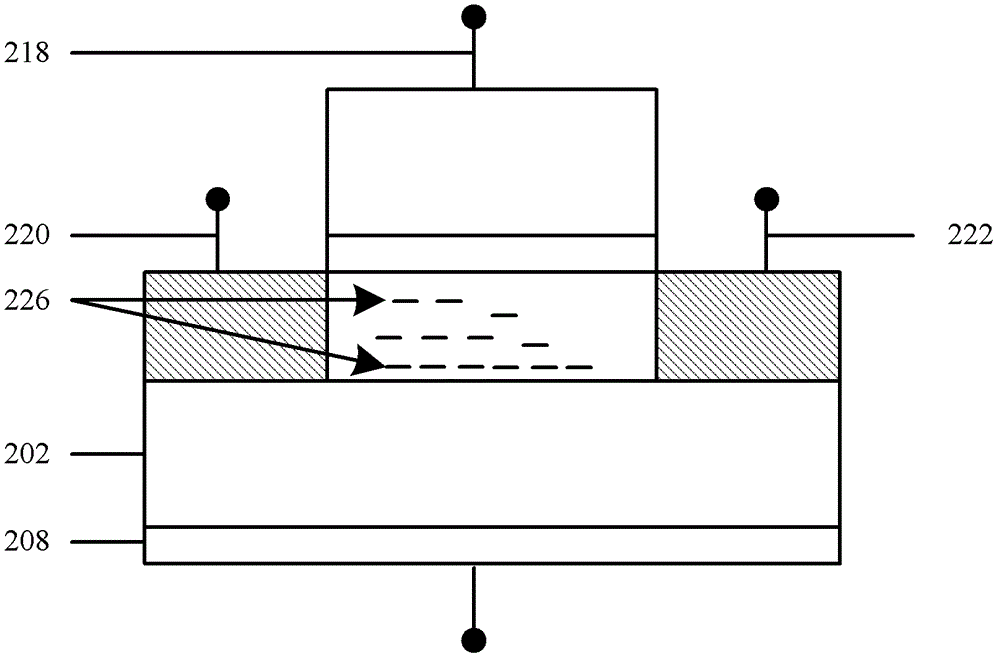

Vertical high-power field-effect transistor unit structure

InactiveCN1450657ASmall unit areaHigh pressureSemiconductor/solid-state device manufacturingSemiconductor devicesUnit structureSilicon chip

This invention relates to a vertical N channel MOS high-power field-effect transistor structure applying etching channel method on N silicon epitaxial chip to make grating oxygen layer of the fieldistor and W grating electrode in the channel of the silicon epitaxial film, W grating and silicon chip are vertical on the surface, when the fieldistor in working condition, the current flows from the drain of the silicon chip bottom through an inversion channel zone to get to the source vertical to silicon chip surface.

Owner:SHANGHAI INTEGRATED CIRCUIT RES & DEV CENT +1

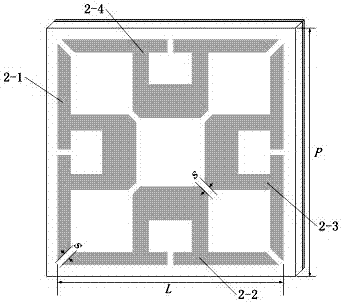

Microwave band polarization insensitive six-frequency band metamaterial wave absorber

The present invention relates to a microwave band polarization insensitive six-frequency band metamaterial wave absorber. The metamaterial wave absorber is composed of a top resonant element, a medium substrate and a metal bottom plate, the top resonant element and the metal bottom late are attached on the upper and lower surfaces of the medium substrate respectively, the top resonant element is composed of four multimode omega-shaped resonators which are placed at the upper, lower, left and right edges of the medium substrate symmetrically and are totally same, and the multimode omega-shaped resonators can show a plurality of different absorption peaks under the horizontal polarization and the vertical polarization. The metamaterial wave absorber provided by the present invention has the characteristics of high wave absorption rate and insensitive polarization, also has six wave absorption peak points, and has the very high engineering application value.

Owner:SOUTHWEST UNIVERSITY

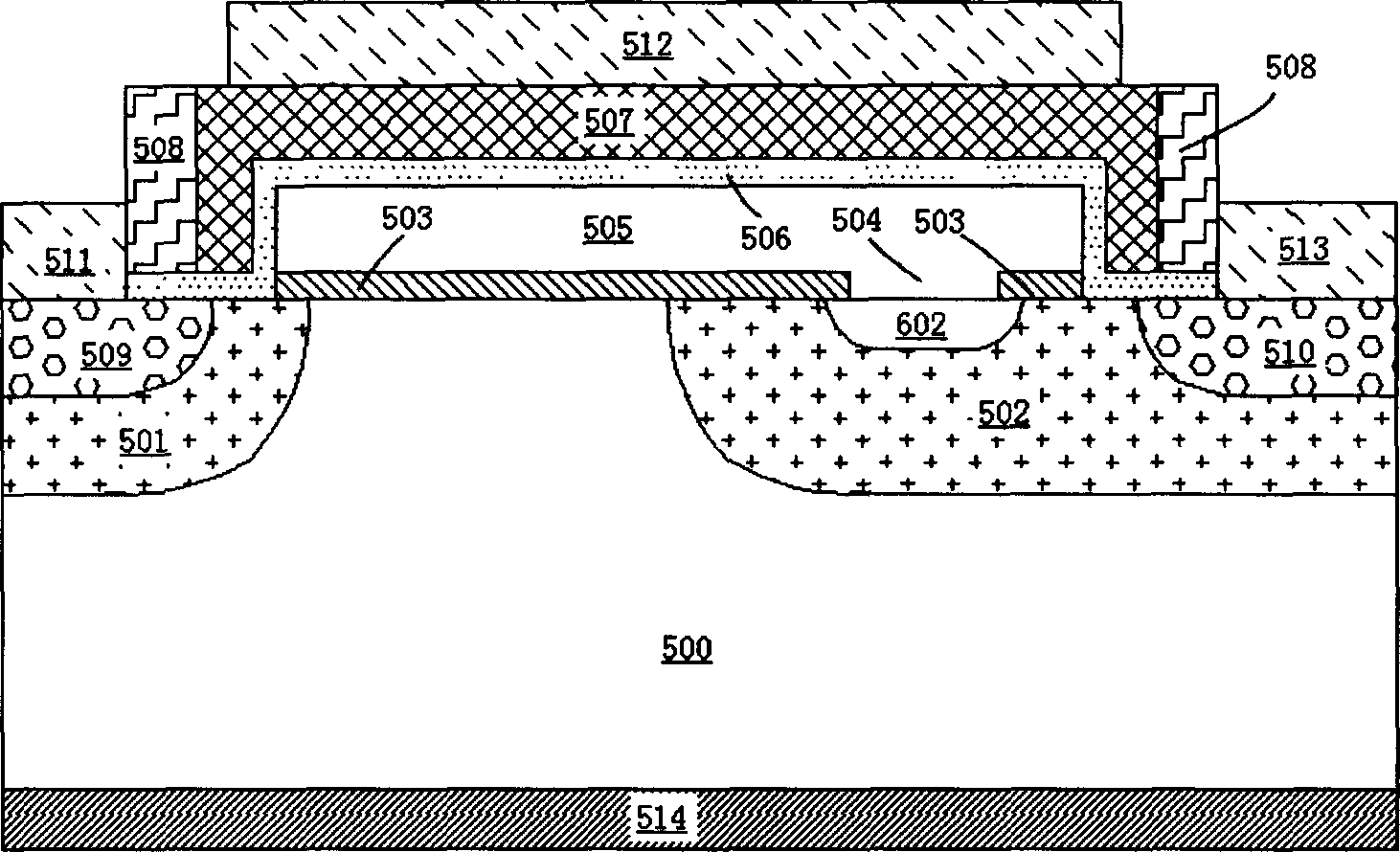

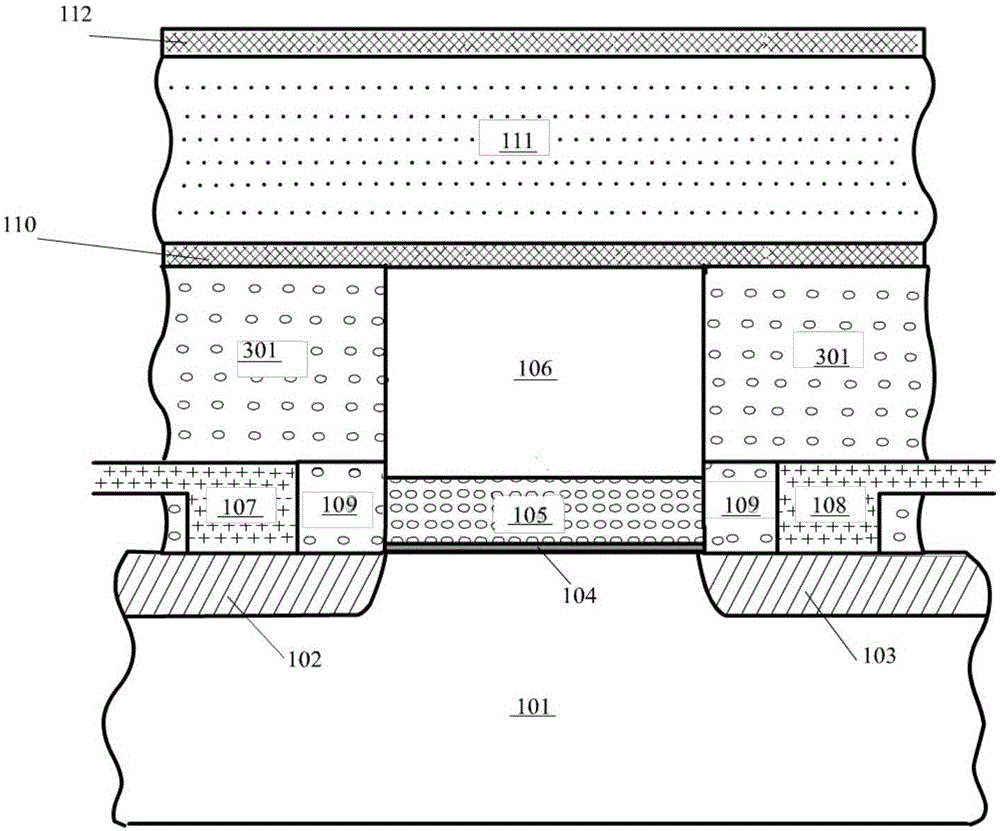

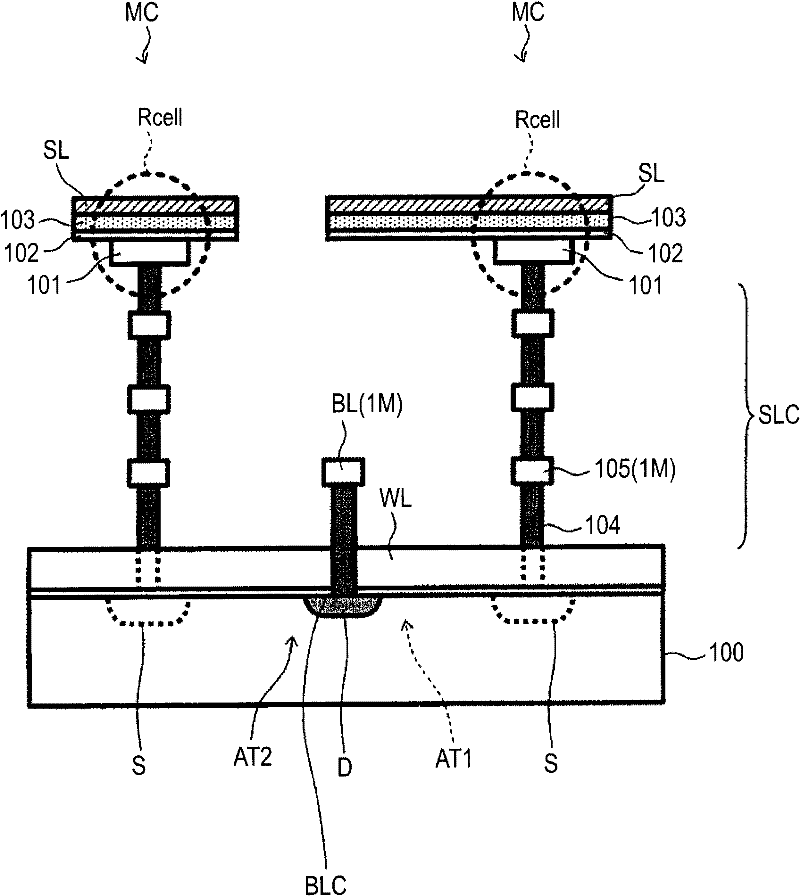

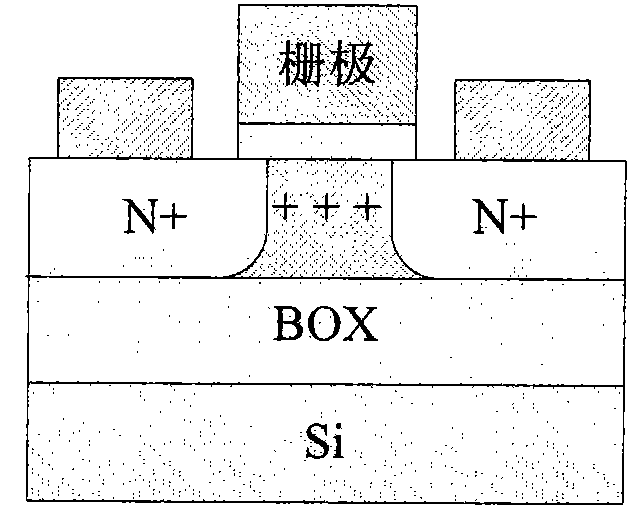

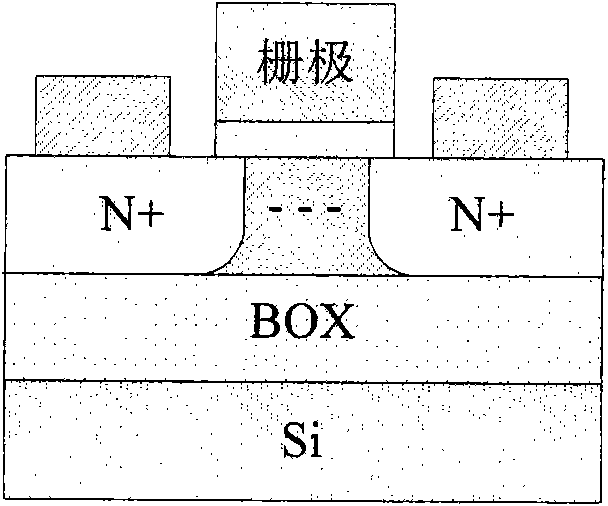

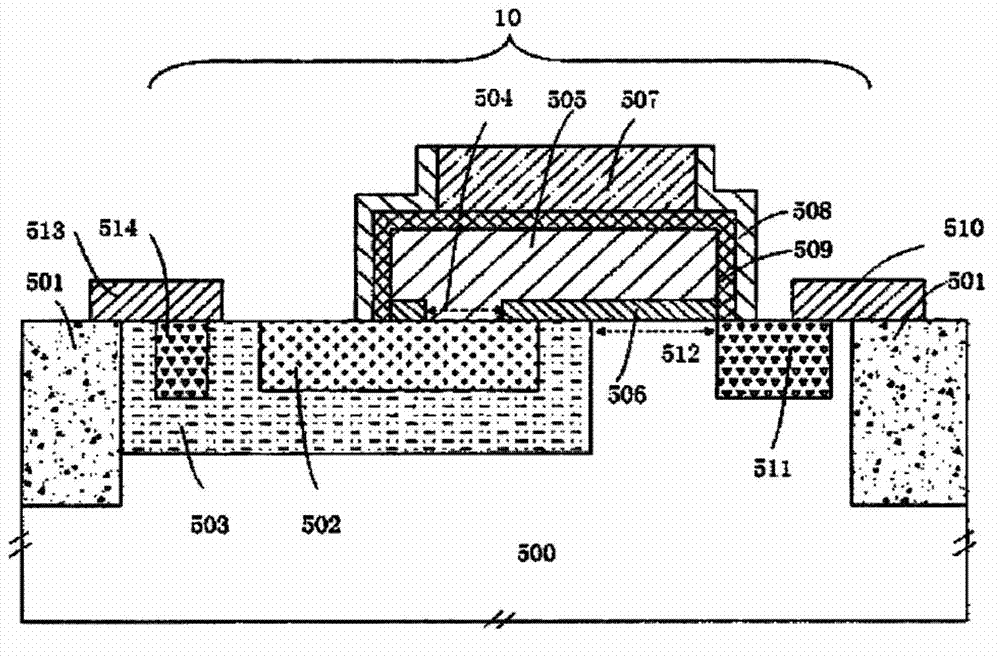

Floating body cell structure of dynamic random access memory and manufacturing technology thereof

InactiveCN101771051ASmall unit areaImprove reliabilityTransistorSolid-state devicesStatic random-access memoryManufacturing technology

The invention discloses a floating body cell structure of a dynamic random access memory and manufacturing technology thereof. The structure comprises an N type semiconductor area on a buried oxide layer (BOX), a P type semiconductor area on the N type semiconductor area and a gate area on the P type semiconductor area. Electric isolation areas are arranged around the P type semiconductor area and the N type semiconductor area. In the invention, isolated floating body gate diodes are employed as the storage nodes. Through tunneling among bands, the state that holes are accumulated in the floating body is defined as the first storage state. Through forward bias of PN junctions, the state that the holes are transmitted from the floating body or the electrons are injected into the floating body is defied as the second storage state. The two states lead to difference of the forward turn-on voltage of the floating body gate diodes (P+ / N+) and can be sensed through the current intensity. The gate diode (P+ / N+) floating body cell of the memory has high efficiency, low power consumption and high density and has the advantages of simple manufacturing technology, high integration density, low cost, high reliability, etc.

Owner:SHANGHAI INST OF MICROSYSTEM & INFORMATION TECH CHINESE ACAD OF SCI

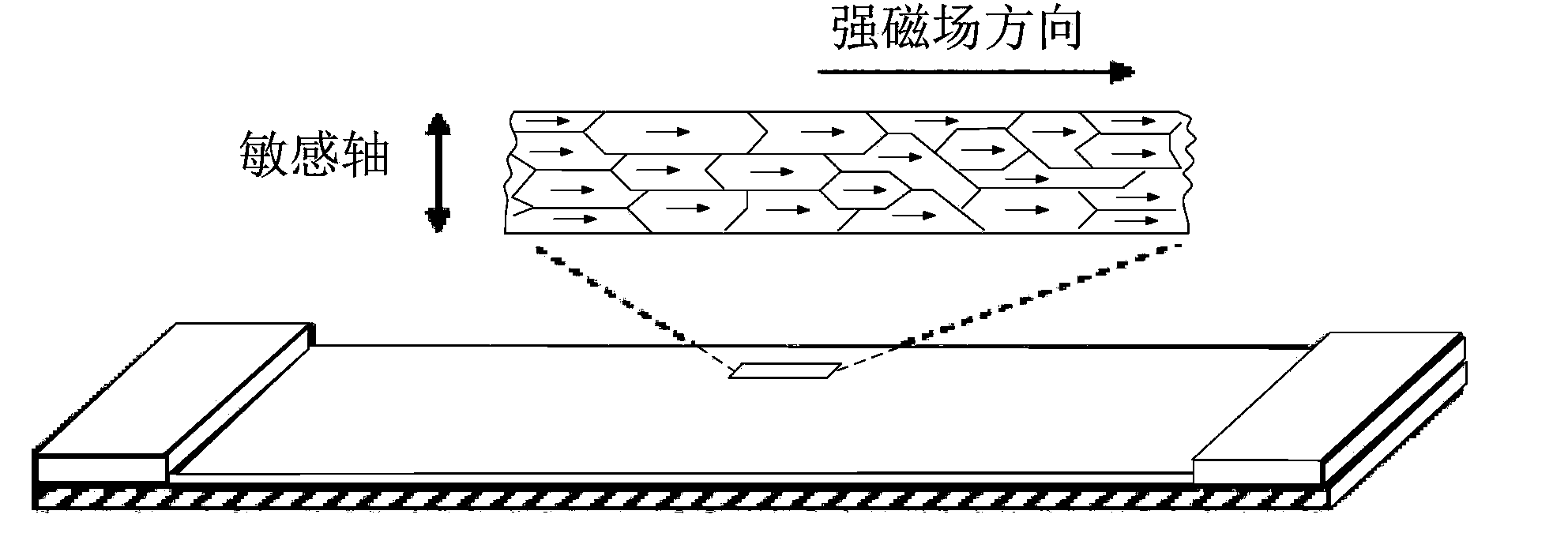

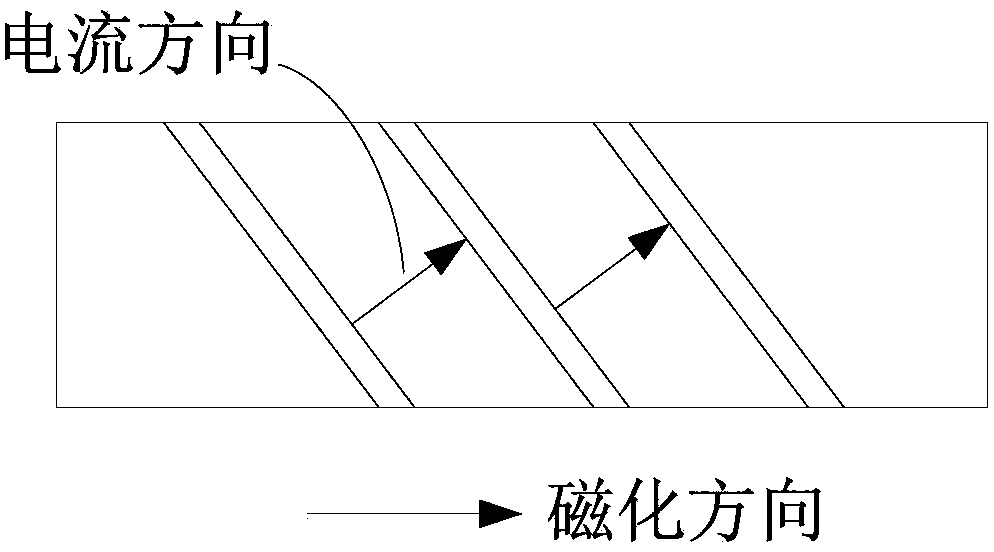

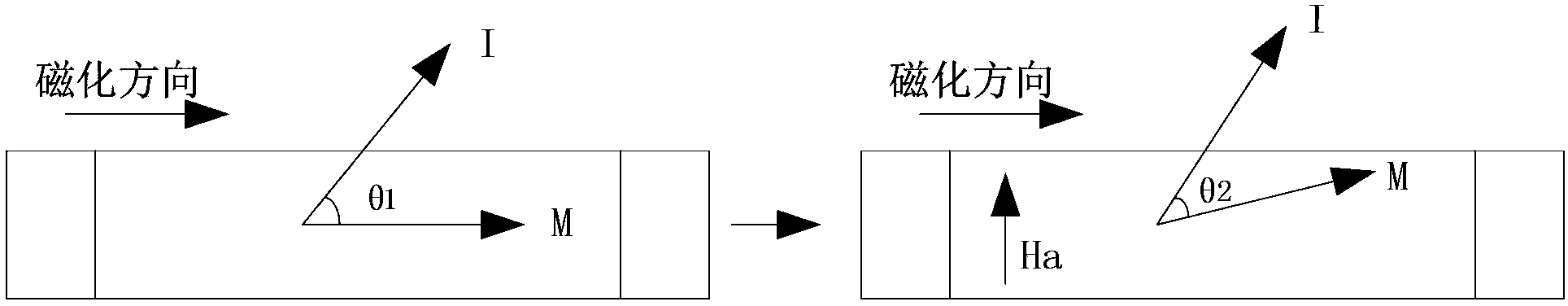

High-density magnetic sensor device and magnetic induction method and preparation process thereof

InactiveCN104122513AImprove manufacturabilityImprove performanceManufacture of electrical instrumentsMagnitude/direction of magnetic fieldsHigh densityUltimate tensile strength

The invention discloses a high-density magnetic sensor device and a magnetic induction method and preparation process thereof. The high-density magnetic sensor device comprises a third direction magnetic sensing member. The third direction magnetic sensing member includes a base, a magnetic permeable unit, induction units and a peripheral circuit. The surface of the base is provided with a trench; the magnetic permeable unit comprises a first magnetic permeable portion and a second magnetic permeable portion which are disposed respectively at two sides of the trench; the induction units are disposed on the surface of the base and at the two sides of the trench, and respectively match the first magnetic permeable portion and the second magnetic permeable portion in the trench; and the induction units are used for receiving magnetic signals in the third direction outputted by the magnetic permeable unit, and measuring the magnetic field strength and direction corresponding to the third direction based on the magnetic signals. According to the invention, the induction devices in the X-axis, Y-axis and Z-axis can be disposed on the same wafer or chip, and the invention has the advantages of good manufacturability, excellent performance and significant price competitiveness; and the unit area of elements can be reduced, and the utilization rate of the chip area is improved.

Owner:QST CORP

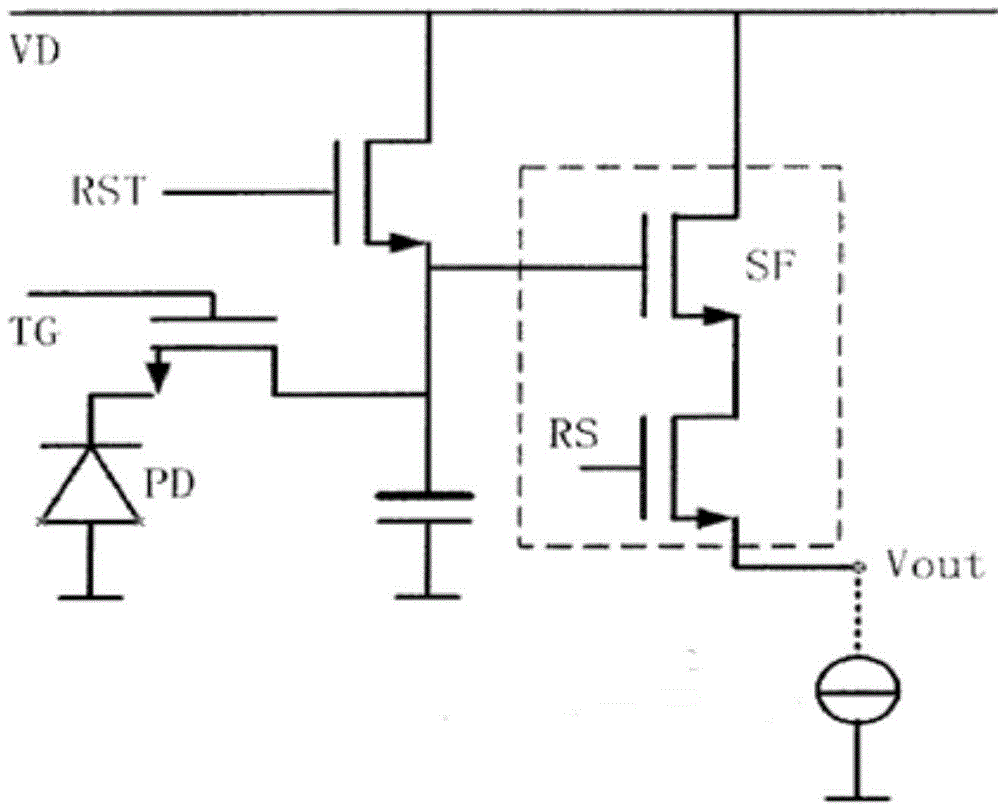

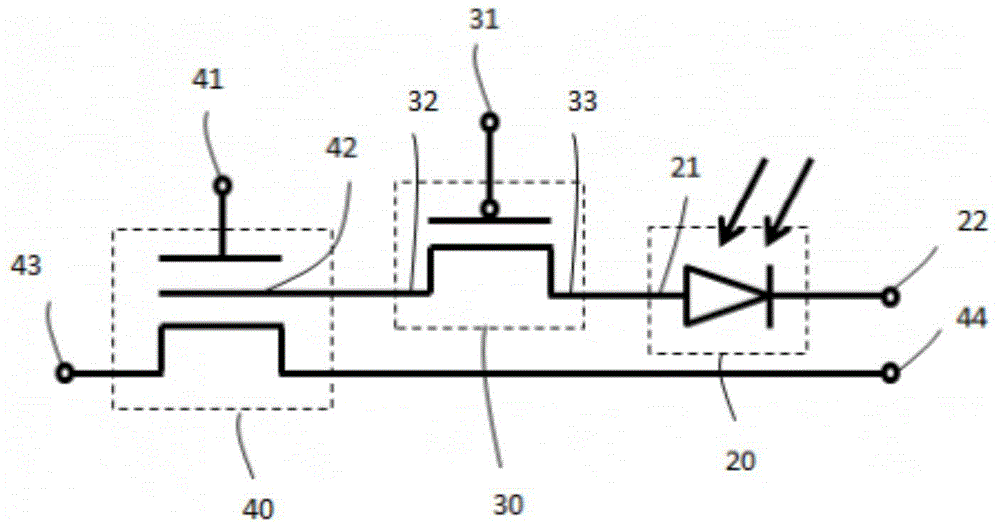

Semiconductor light-sensitive cell and semiconductor light-sensitive cell array thereof

ActiveCN104157658AExtension of timeLarge dynamic rangeTransistorSolid-state devicesSmall cellSemiconductor

The invention relates to a semiconductor light-sensitive cell and a semiconductor light-sensitive cell array thereof. A floating gate transistor, a strobe MOS tube and a light-sensitive diode are disposed in a semiconductor substrate. An anode or cathode of the light-sensitive diode is connected to a floating gate of the floating gate transistor through the strobe MOS tube, and the corresponding cathode or anode of the light-sensitive diode is connected to a drain of the floating gate transistor or electrically connected to an external electrode. As for the semiconductor light-sensitive cell, after the strobe MOS tube is switched on, the floating gate is charged or discharged through the light-sensitive diode; and after the strobe MOS tube is switched off, the charge is stored in the floating gate of the floating gate transistor. The semiconductor light-sensitive cell has the advantages of small cell area, low surface noise, long floating gate storing charge time, large operating voltage dynamic range and the like.

Owner:SUZHOU ORIENTAL SEMICONDUCTOR CO LTD

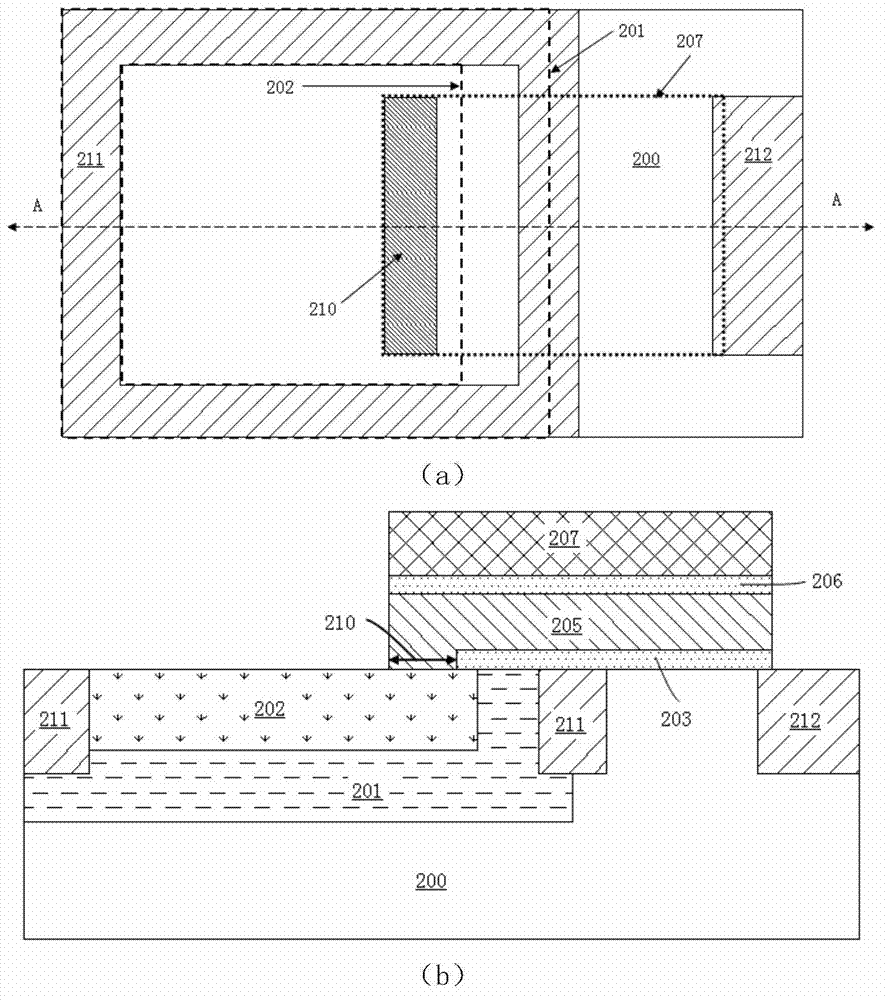

Semiconductor photosensitive device and manufacturing method thereof

InactiveCN103594477ALower resistanceLower column resistanceSemiconductor/solid-state device manufacturingRadiation controlled devicesImage resolutionSemiconductor

The invention belongs to the technical field of semiconductor devices, and particularly relates to a semiconductor photosensitive device and a manufacturing method of the semiconductor photosensitive device. The semiconductor photosensitive device comprises an MOS transistor, a photosensitive pn junction diode and a pinning diode, wherein the MOS transistor, the photosensitive pn junction diode and the pinning diode are formed in a semiconductor substrate, a floating gate of the MOS transistor is connected with one end of the photosensitive pn junction diode through a floating gate opening and connected with one end of the pinning diode, the photosensitive pn junction diode and the pinning diode are surrounded by an annular drain region of the MOS transistor and the annular drain region of the MOS transistor is connected with the other end of the photosensitive pn junction diode and the other end of the pinning diode. A light absorption zone of the photosensitive pn junction diode can be pushed into the semiconductor substrate by the pinning diode and is far away from the interfered surface. An image sensor chip manufactured through the semiconductor photosensitive device has the advantages of being small in unit area, high in chip density, high in sensitivity, high in resolution ratio and the like.

Owner:FUDAN UNIV

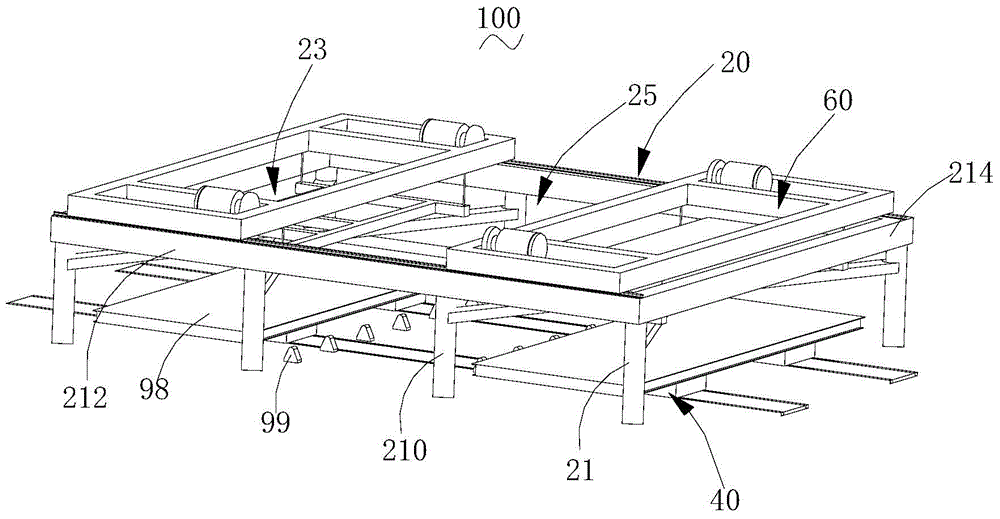

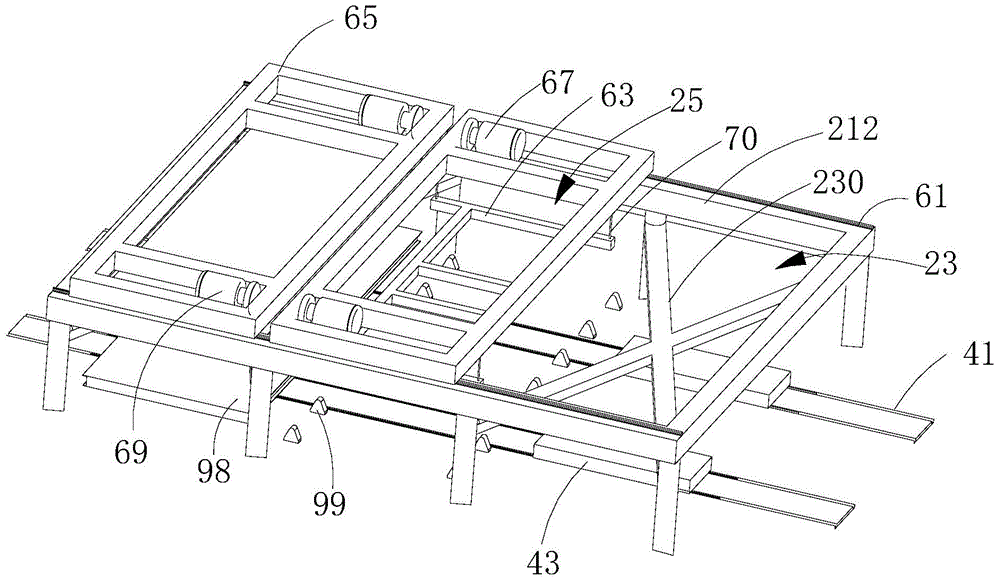

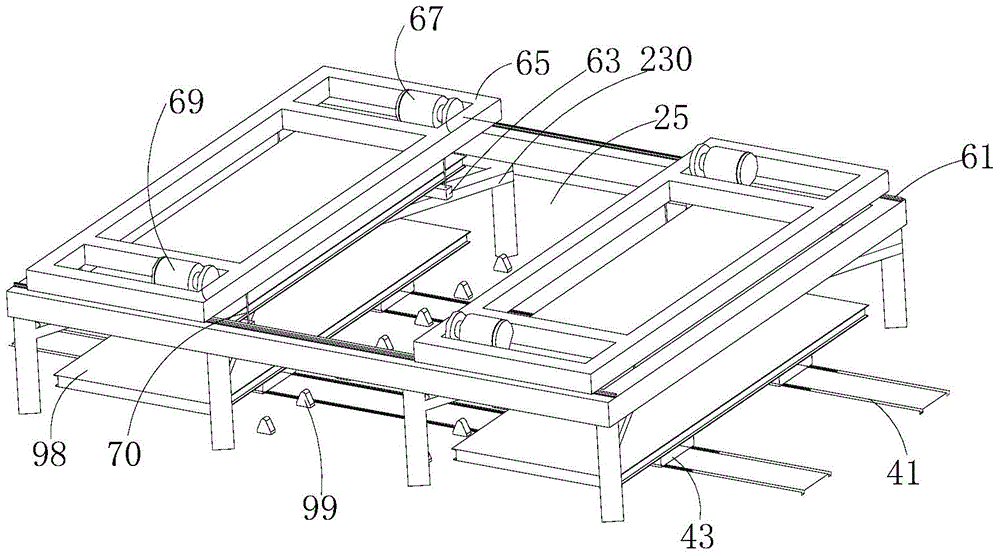

Precuring bin, production line containing precuring bin and control method of production line

ActiveCN104589476AIncrease productivitySmall unit areaCeramic shaping apparatusProduction lineComing out

The invention discloses a precuring bin. The precuring bin comprises a bin body, a lifting device and a horizontal movement device, wherein the bin body comprises a storage space and an access way, the storage space at least comprises an upper layer and a lower layer, the access way is communicated with the upper layer of the storage space, the lifting device comprises a sliding part, a bracket arranged on the sliding part and a power component, the bracket is used for driving a prefabricated part to rise and fall along the access way under the action of the power component and driving the prefabricated part to enter and come out of the upper layer of the storage space in the first direction along with the sliding part, and the horizontal movement device is used for driving the prefabricated component to move back and forth in the first direction relative to the lower layer of the storage space. By the adoption of the precuring bin designed in a multi-layer stacked mode, prefabricated parts to be precured and precured prefabricated parts can be stored and taken out regularly on one station, production efficiency is improved, and productivity in unit area is improved. The invention further relates to a production line containing the precuring bin and a control method of the production line.

Owner:CHINA MINSHENG ZHUYOU

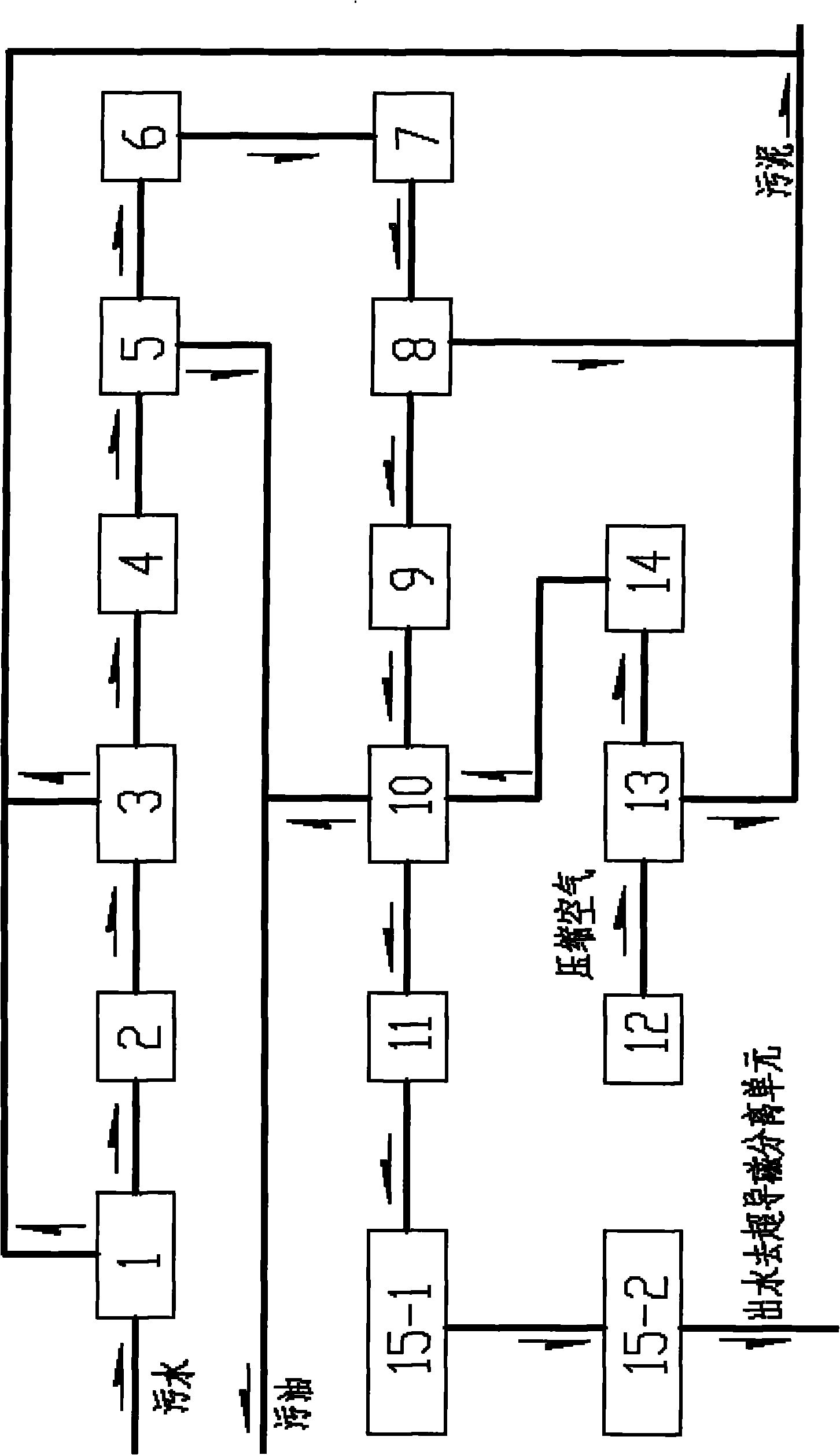

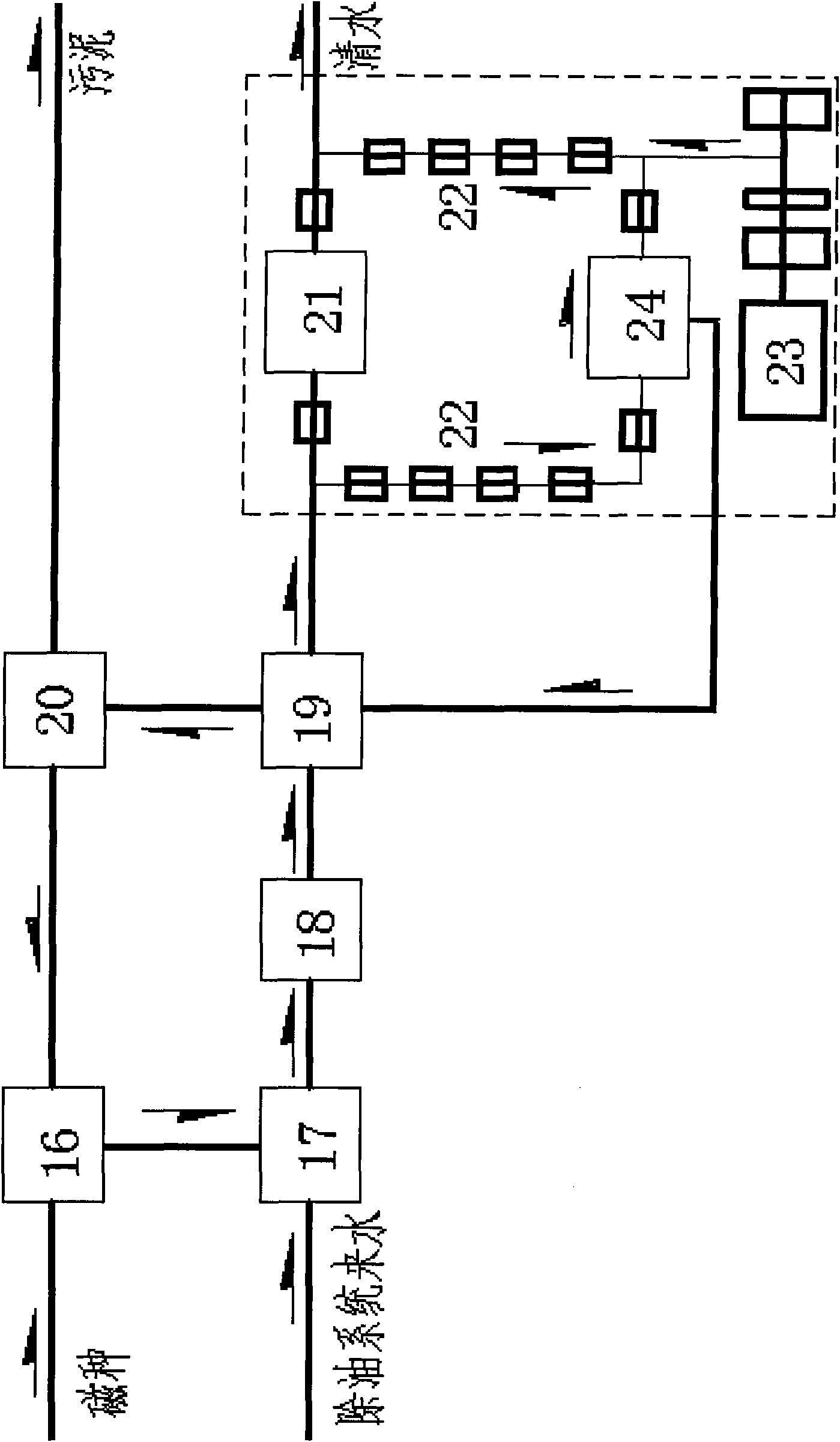

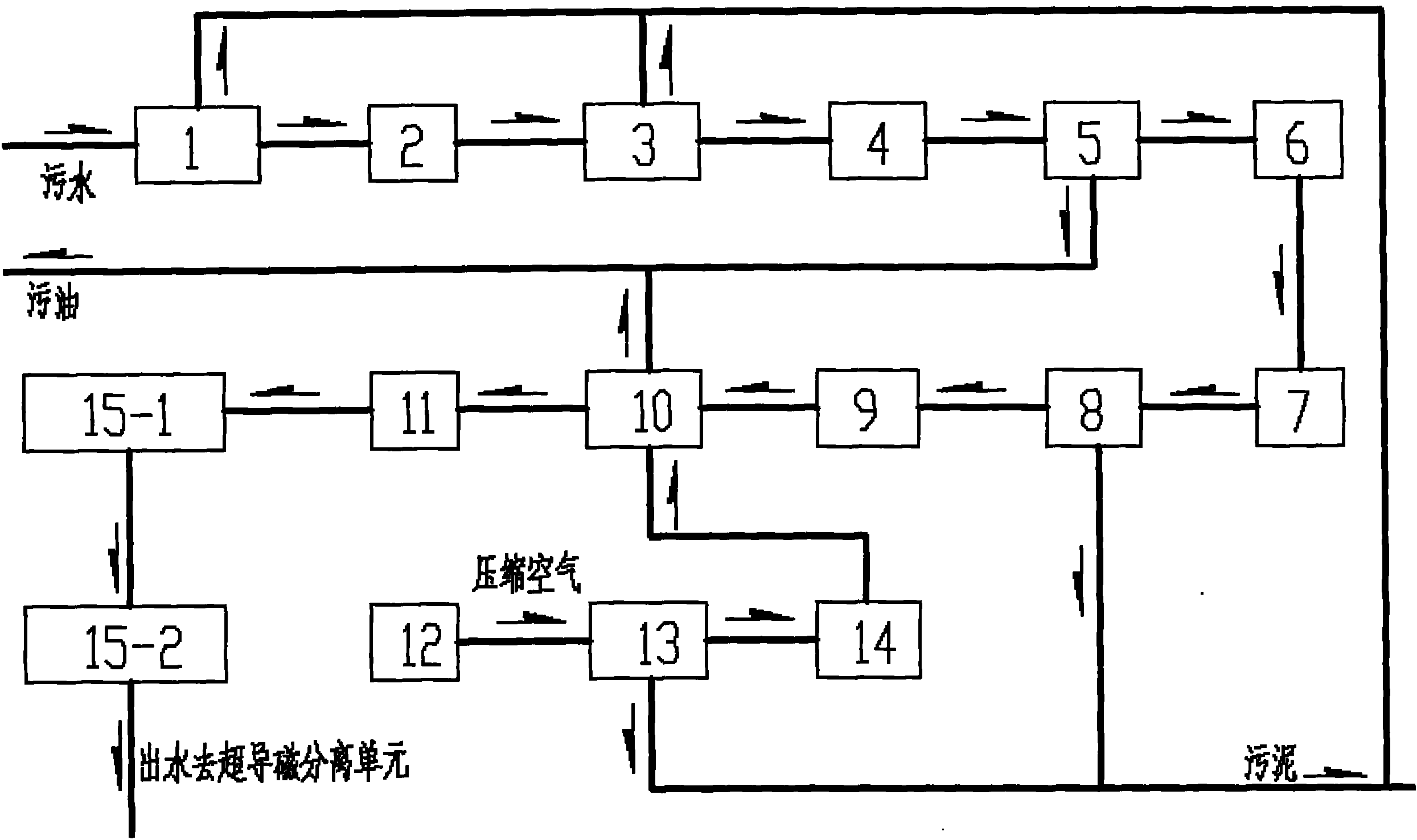

Combined sewage treatment method for oil field

ActiveCN102092886AEfficient captureShort processMultistage water/sewage treatmentCycloneSmall footprint

The invention discloses a combined sewage treatment method for an oil field, which is applied to sewage treatment in a petroleum development gather and delivery process. The method comprises the following steps of: (A) performing a physical separation method: roughly filtering the effluent, regulating the pressure, filtering before metering, and metering the flow to stabilize the pressure; feeding the sewage into a hydraulic cyclone to separate floating oil and dispersible oil; feeding the sewage into a normal pressure buffer tank, and feeding the sewage into the inflating hydraulic cyclone by compression of a screw pump to remove emulsified oil in the sewage; (B) filtering the water flowing out from the inflating hydraulic cyclone into a laminated filter; and (C) feeding the water flowing out from the laminated filter into a magnetic seed mixing tank of a superconducting magnetic separation unit, feeding the nano magnetic seeds into the magnetic seed mixing tank through a magnetic seed feeding tank, pressurizing the water and the magnetic seeds through a mixing pump to enter a pre-sedimentation tank to form lump sediment using the magnetic seeds as cores, feeding the upper clarified liquid and partial water containing the magnetic seed lumps into a superconducting magnetic separation device, and feeding the separated magnetic seeds into the magnetic seed feeding tank. The method has the advantages of no need of chemical agents, short process flow, small floor area and low integral investment and running expenses.

Owner:BC P INC CHINA NAT PETROLEUM CORP +1

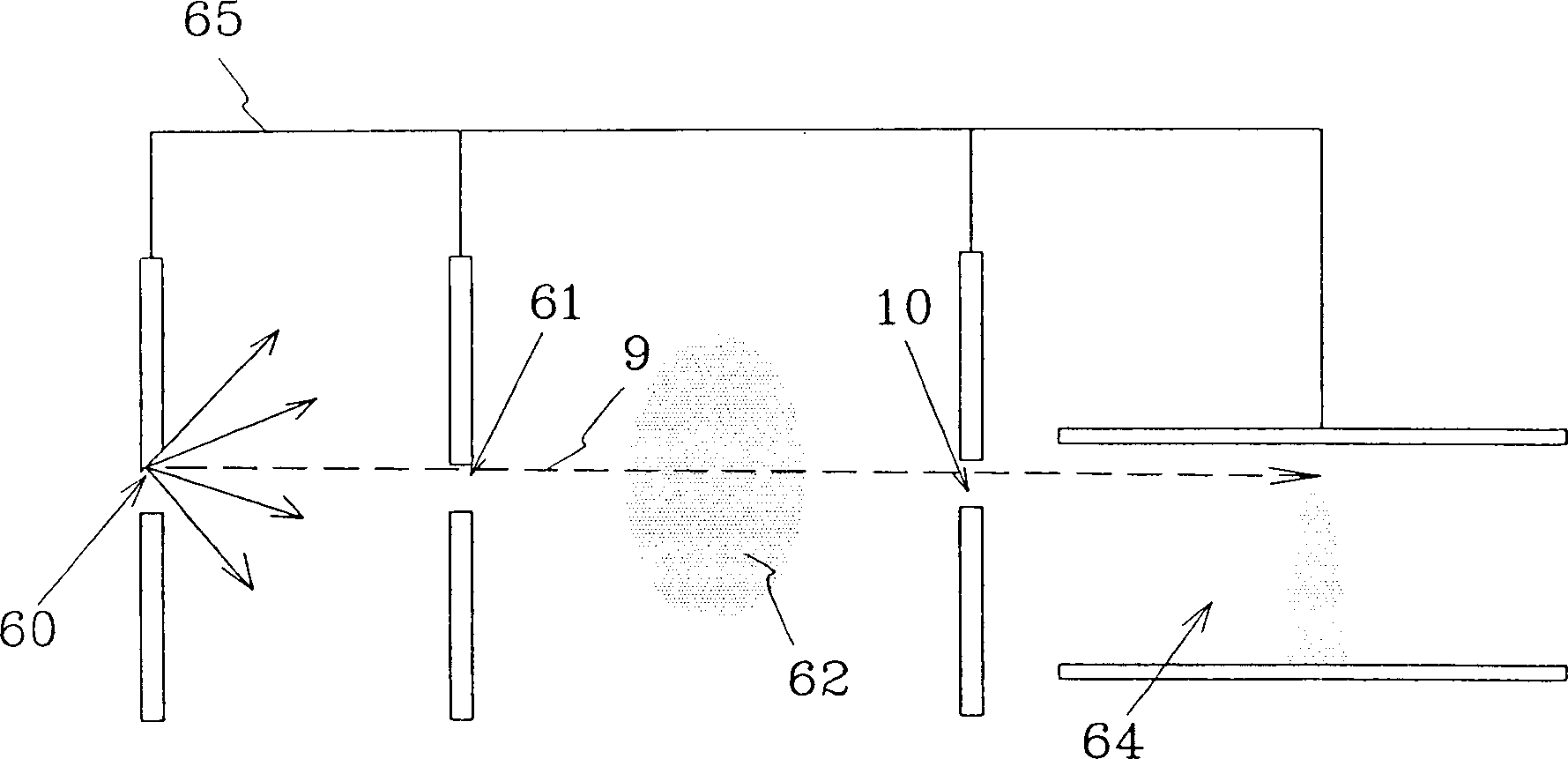

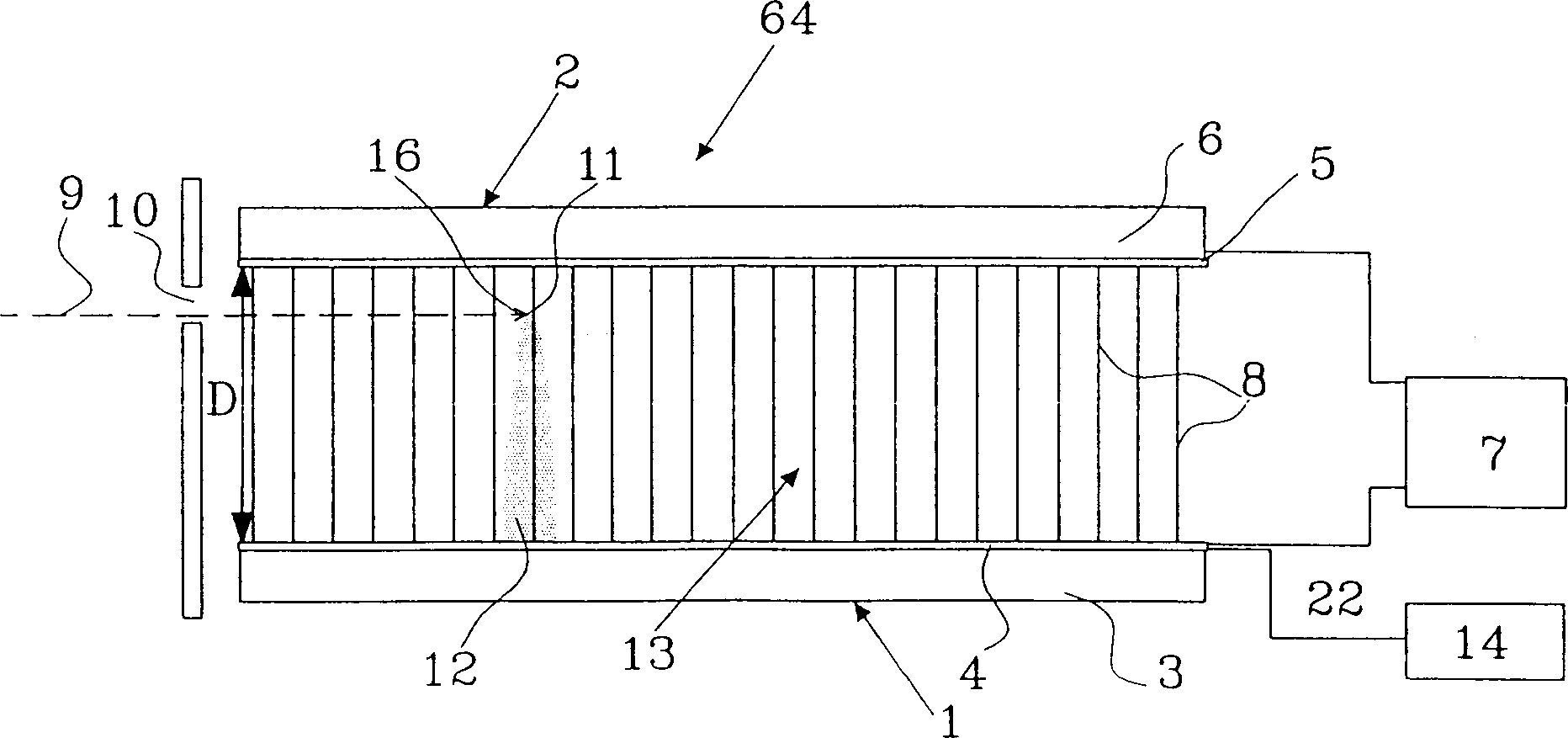

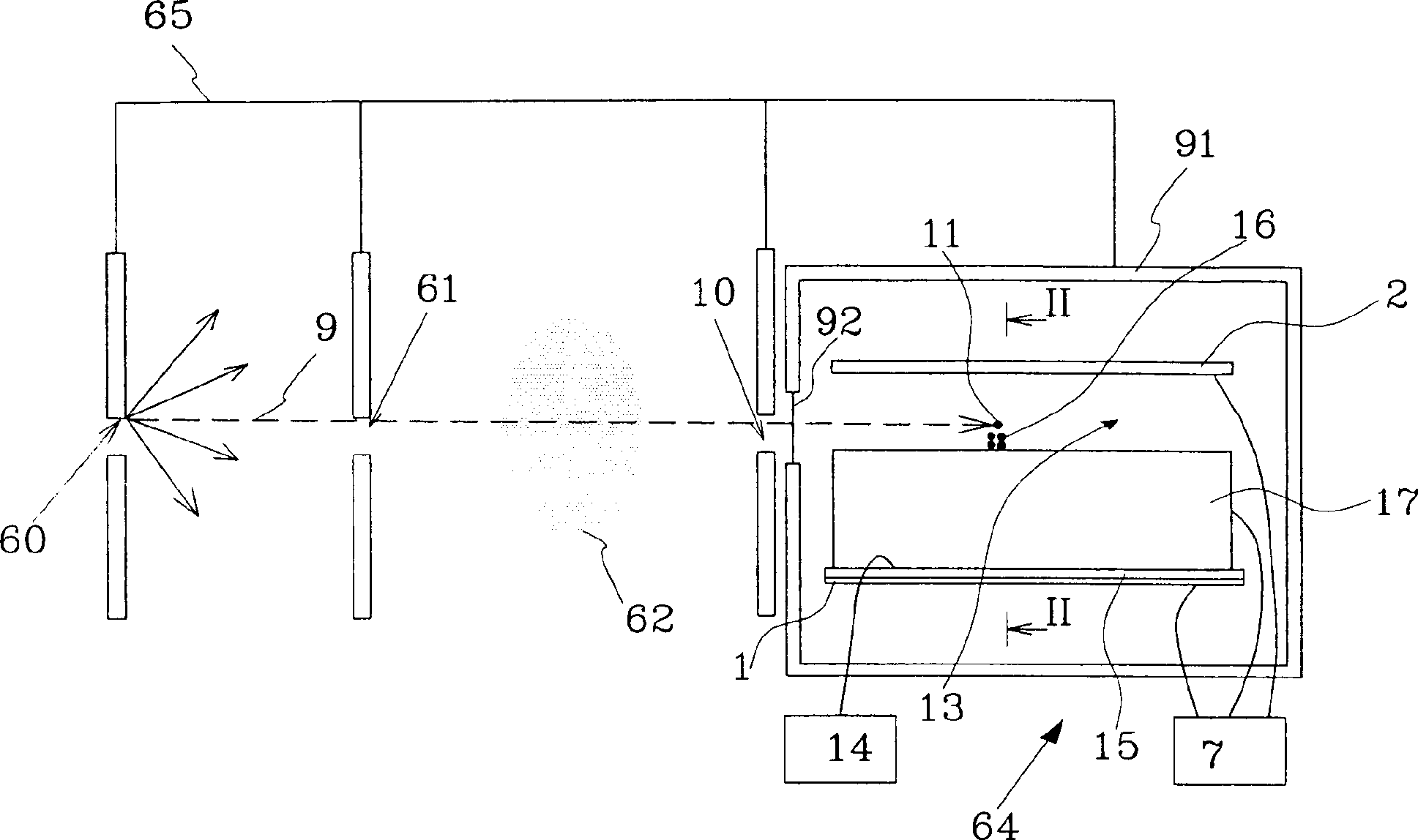

Method and apparatus for radiography and radiation detector

InactiveCN1415076AReduce manufacturing costLow manufacturing costElectric discharge tubesRadiation intensity measurementIonElectric field

A method and apparatus for radiography and also a detector for detecting incident radiation. In the method and the apparatus X-rays (9) are emitted from an X-ray source (60). Said X-rays which have interfered with an object to be imaged are detected (62) in a detector (64). The detector (64), which detects incident radiation is a gaseous avalanche chamber, including electrode arrangements between which a voltage is applied for creating an electrical field, which causes electron-ion avalanches of primary and secondary ionisation electrons released by incident radiation. The detector detects electrical signals in at least two detector electrode modules, said electrical signals being induced by electron-ion avalanches, in at least one of a plurality of detector electrode elements arranged adjacent to each other, each along a direction being essentially parallel to the incident radiation, and where the at least two independent detector electrode modules are arranged in close proximity to each other, each along a direction being essentially parallel to the incident radiation.

Owner:XCOUNTER

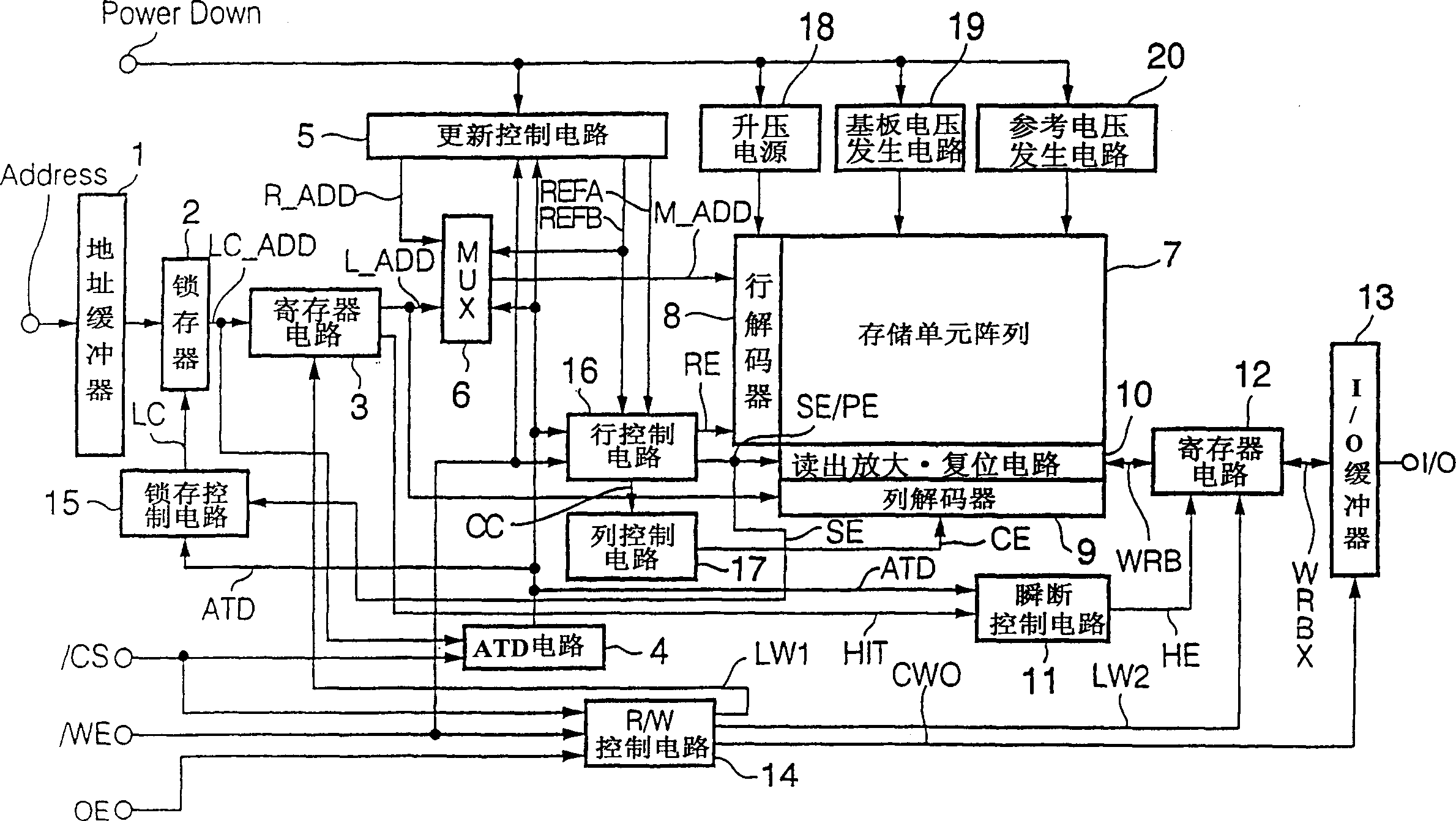

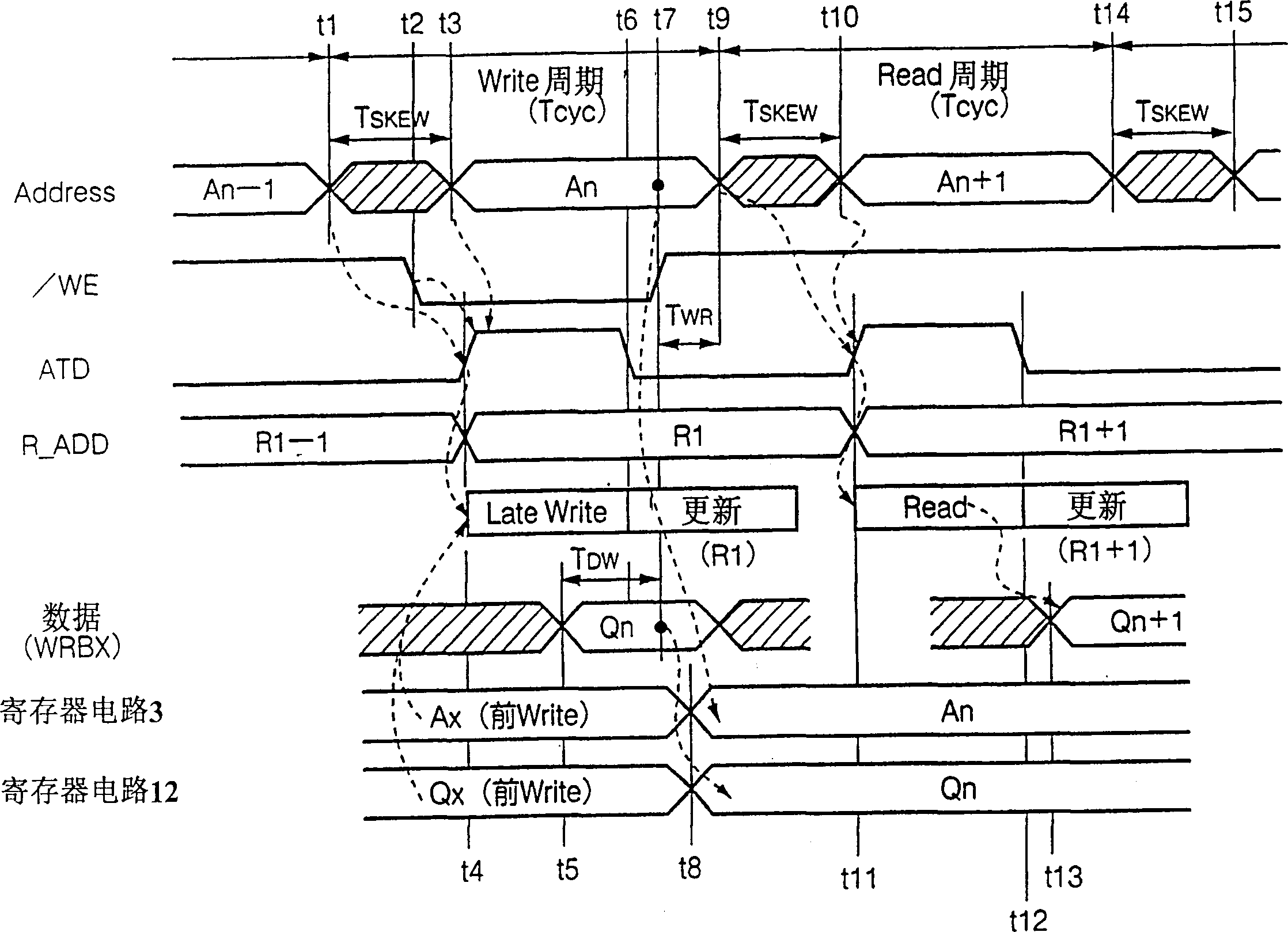

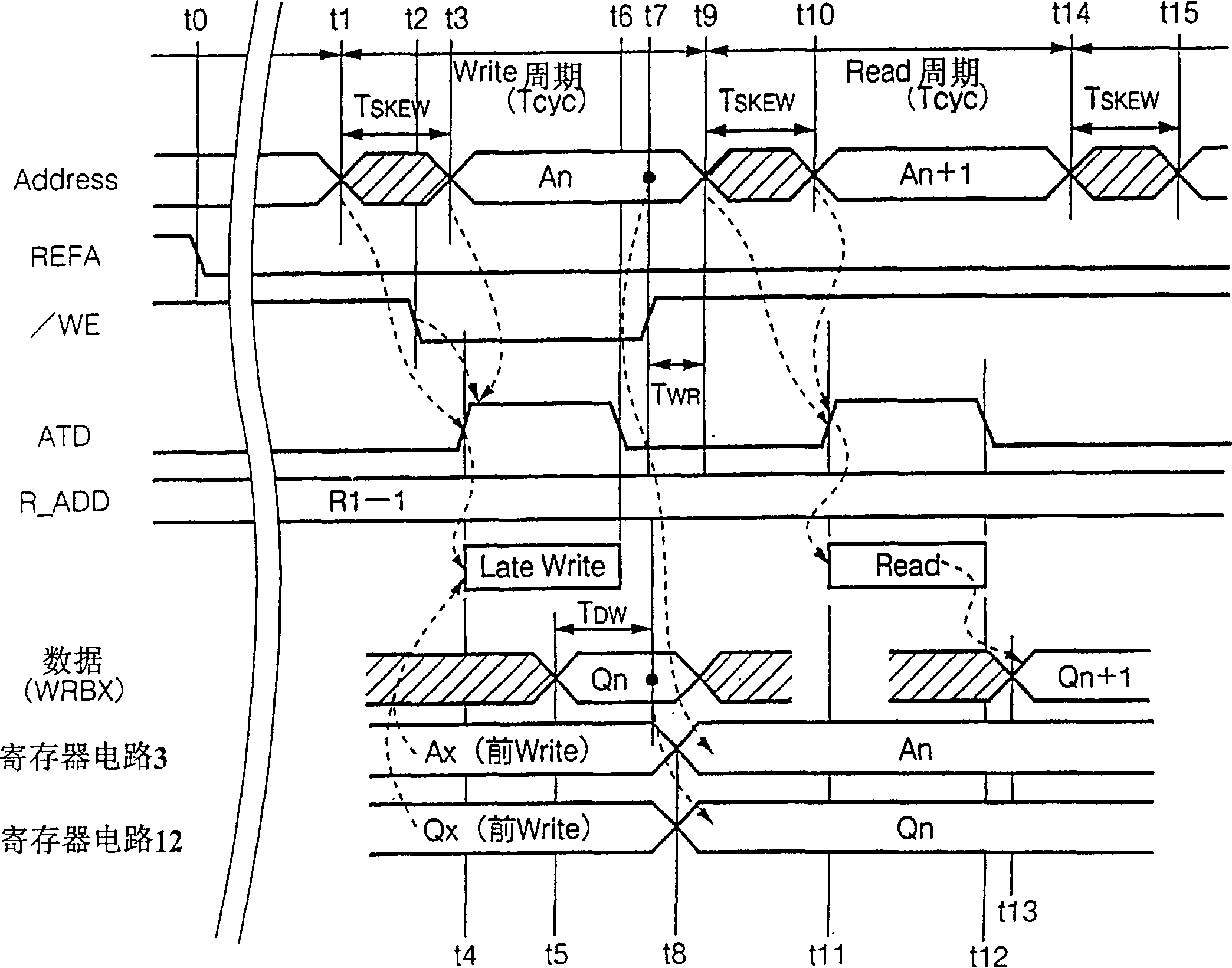

Semiconductor storage device

InactiveCN1422430AReduce power consumptionSmall sizeDigital storageProcessor registerSemiconductor storage devices

A semiconductor storage device operating according to SRAM specifications in which normal access is not delayed by the effect of refresh and the memory cycle can be shortened as compared with conventional one. An ATD circuit (4) is subjected to variation of address (Address) and generates a one-shot pulse in an address variation detection signal (ATD) after an address skew period. In response to a write request, a write enable signal ( / WE) is caused to fall during the address skew period. Write or read is started at the rise of the one-shot pulse. When write is performed, late write is performed, using an address and data provided when write is requested immediately before. Subsequently, refresh is performed within a period from the fall of the one-shot pulse and to the end of the address skew period of the next memory cycle. For the late write performed in response to the next write request, an address and data are taken into register circuits (3, 12) at the rise of the write enable signal ( / WE).

Owner:RENESAS ELECTRONICS CORP

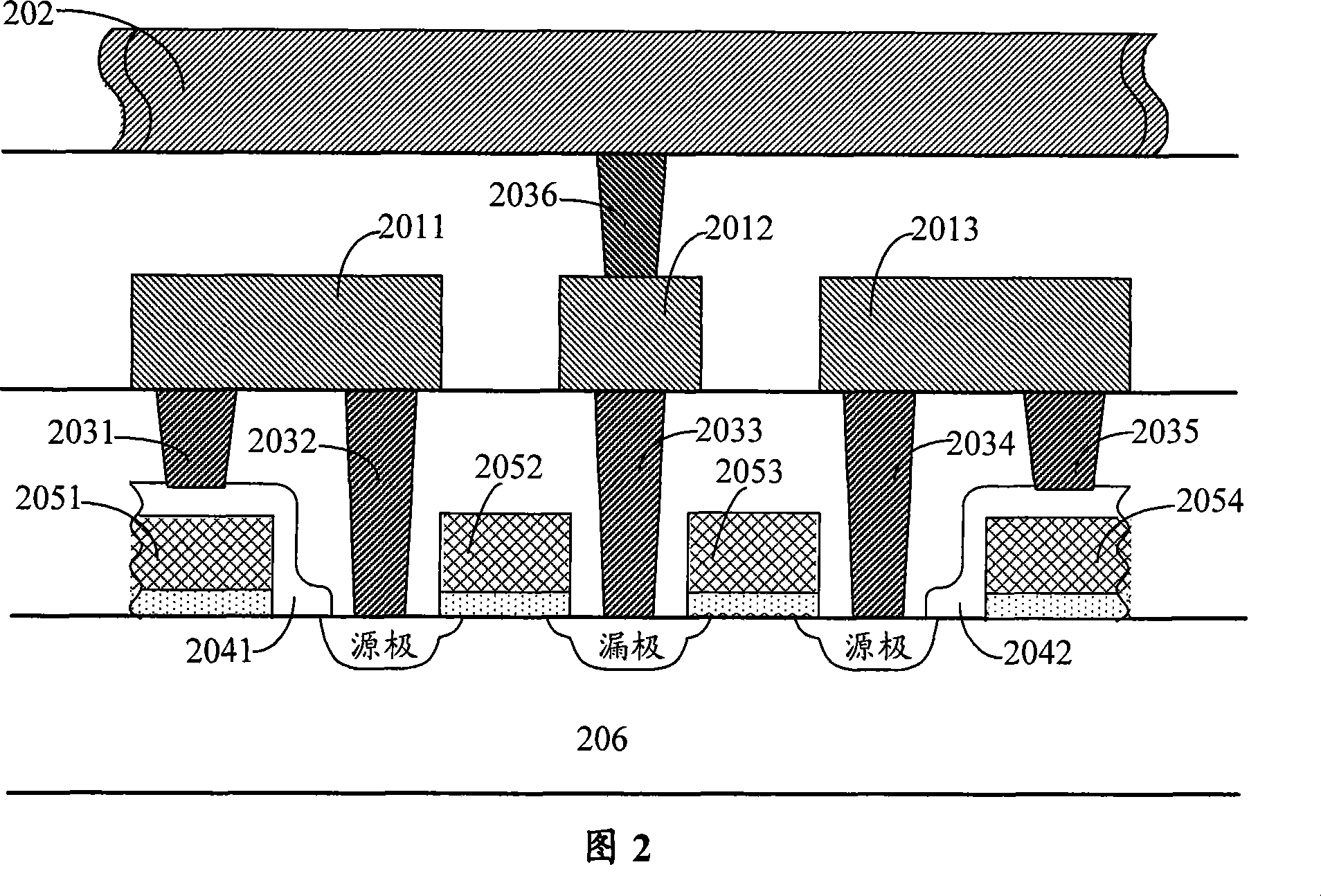

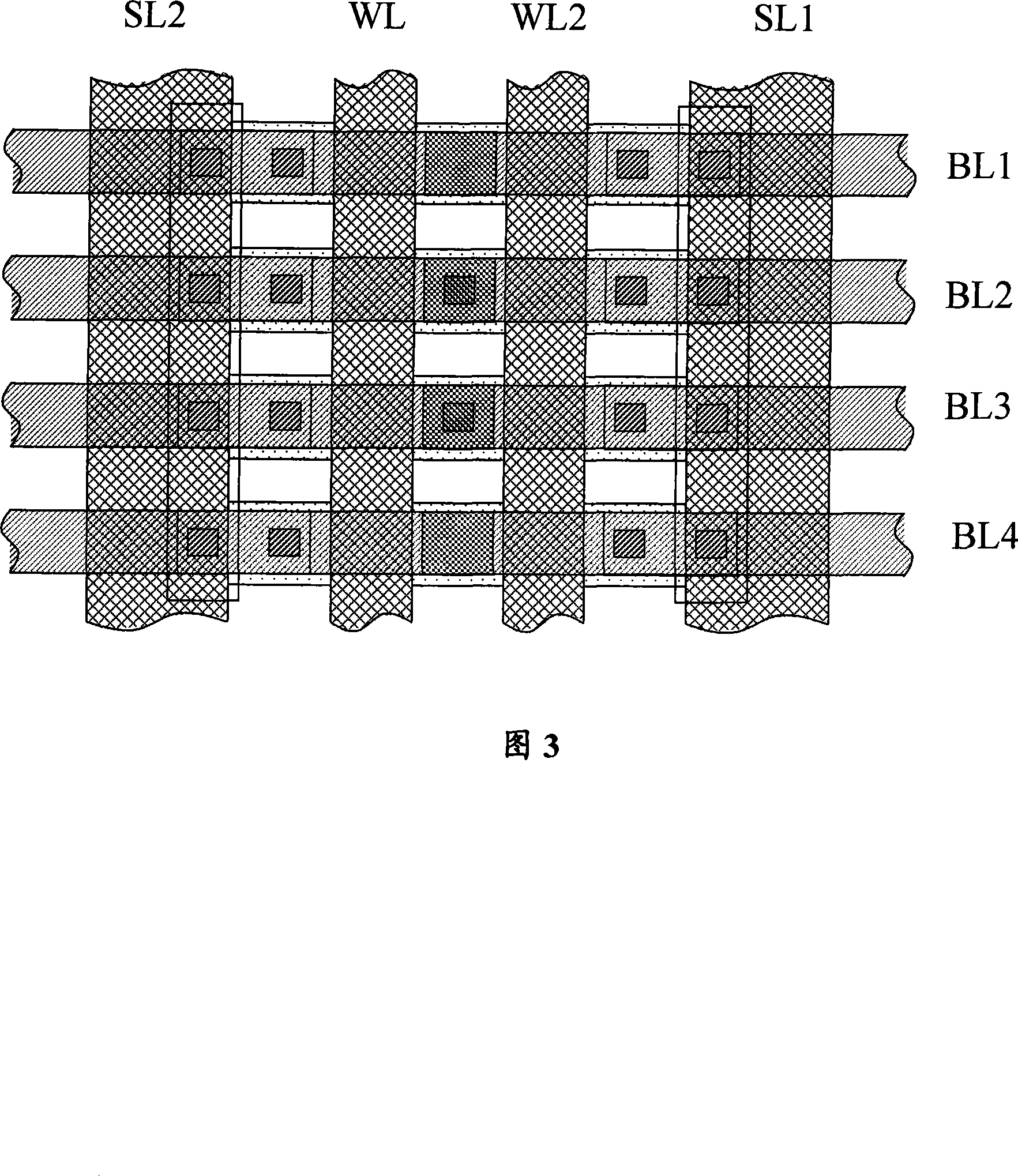

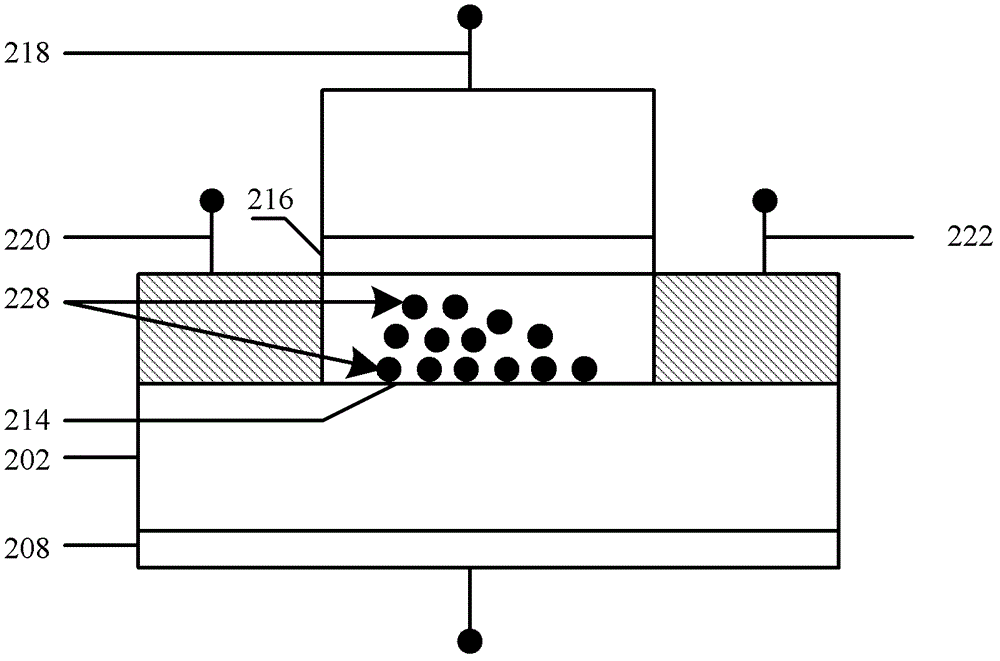

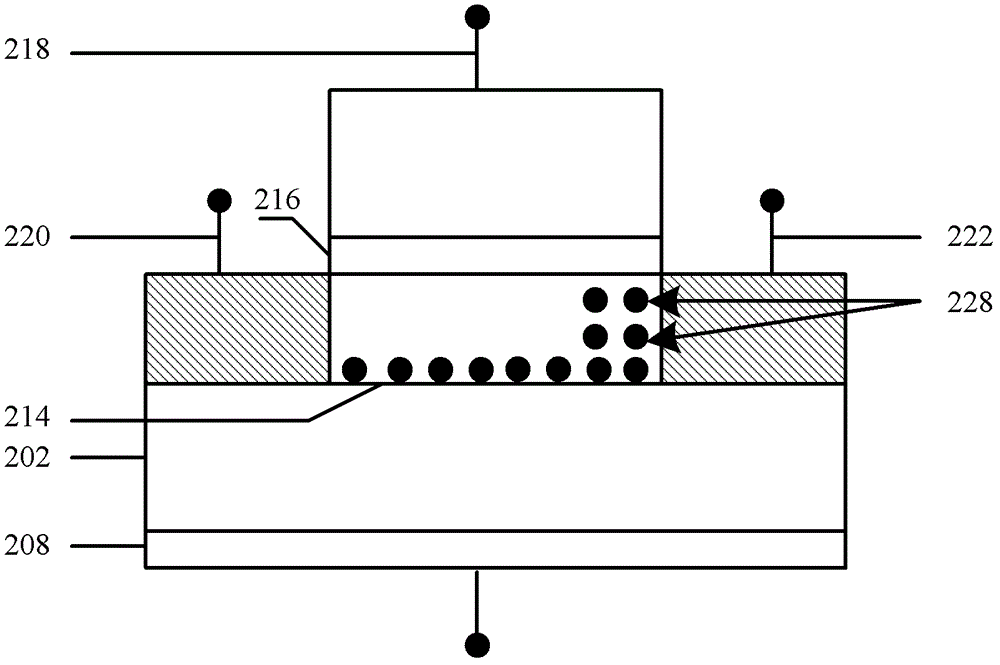

A programmable non volatile memory unit, array and its making method

ActiveCN101188240ASmall unit areaImprove integration densitySemiconductor/solid-state device detailsSolid-state devicesIntegrated circuitPolycrystalline silicon

The invention discloses a programmable nonvolatile storage unit and an array, and the manufacturing method thereof. The device comprises a metal layer, a contact hole, a barrier layer, a plurality of polysilicons in the passive area, a plurality of polysilicons in the active area, and a substrate in the active area. A plurality of transistors are formed by the polysilicons in the active area and a substrate in the active area; a plurality of source lines are formed by the polysilicons in the passive area; A plurality of word lines are formed by the polysilicons in the passive area. A plurality of bit lines are formed by the metal lines in the metal layer. A capacitor is formed by connecting the metal layer, the connecting hole, the barrier layer, and the polisilicons in the passive area one by one. The storage unit is formed by means of corresponding series connection between the transistors and the capacitor and arrayed among the word-lines, the bit-lines and the source lines, which correspond to the storage unit. The invention improves the storage stability, decreases the area of the storage, and popularizes the application of VLSI.

Owner:GIGADEVICE SEMICON (BEIJING) INC

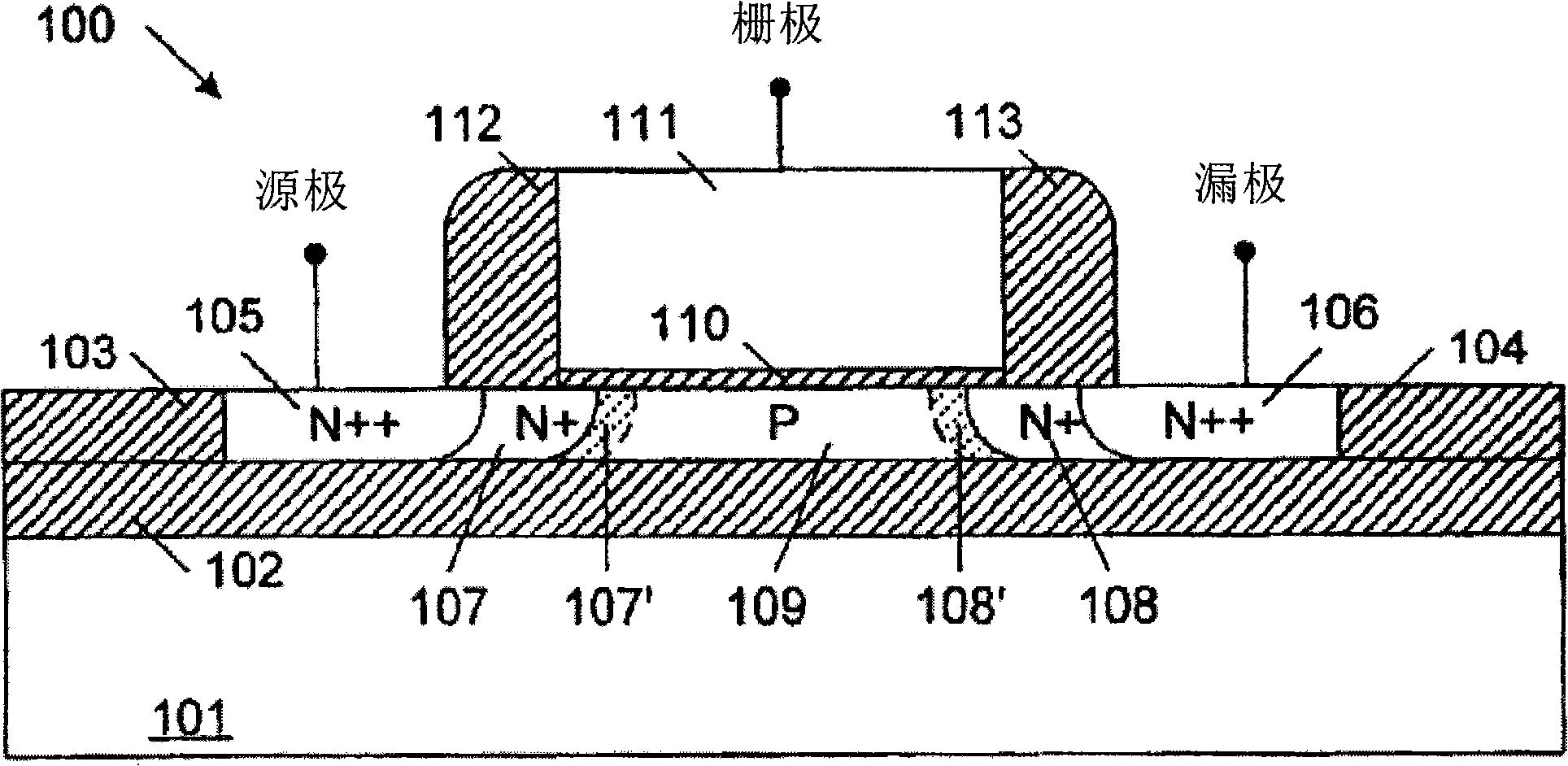

Process for manufacturing floating body dynamic random access memory cell capable of improving data retention ability

InactiveCN102969278ASmall unit areaKeep for a long timeSemiconductor/solid-state device manufacturingFloating body effectRandom access memory

The invention provides a process for manufacturing a floating body dynamic random access memory cell capable of improving data retention ability. The process comprises the steps of providing a first silicon wafer, and preparing a buried oxide layer on the first silicon wafer; bonding a second silicon wafer on the first silicon wafer, and preparing a silicon-on-insulator silicon wafer; pretreating the silicon-on-insulator silicon wafer before preparing a silicon-on-insulator device, implanting nitrogen ions into the buried oxide layer of the silicon-on-insulator silicon wafer, activating implanted nitrogen ions through an annealing process, and forming dangling bonds between the buried oxide layer and a substrate interface; and preparing the floating body effect memory cell in a P-channel metal oxide semiconductor (PMOS) structure on the treated silicon-on-insulator silicon wafer. The process for manufacturing the floating body dynamic random access memory cell capable of improving the data retention ability is provided through implementation of the technical scheme, so that interface dangling bonds between the buried oxide layer and a substrate are increased, electrons are trapped effectively, and the data retention performance of the floating body effect memory cell in the PMOS structure can be improved.

Owner:SHANGHAI HUALI MICROELECTRONICS CORP

Method for manufacturing silicon-on-insulator silicon slice and floating body dynamic random access memory unit

ActiveCN102969268AKeep for a long timeSmall unit areaSemiconductor/solid-state device manufacturingFloating body effectNitric oxide

The invention provides a method for manufacturing a silicon-on-insulator silicon slice. The method includes the following steps that a silicon dioxide thin film and a substrate are formed in a first silicon slice; the first silicon slice is subjected to nitric oxide annealing process to form numerous dangling bonds at an interface position between the silicon dioxide thin film and the substrate; the first silicon slice is subjected to hydrogen ion implantation, a buried layer rich in hydrogen ions is formed in the substrate; a second silicon slice is bonded on the silicon dioxide thin film of the first silicon slice; and bonded silicon slices are subjected to thermal treatment, and the first silicon slice is stripped from the position of the buried layer rich in hydrogen ions to form the silicon-on-insulator silicon slice. By means of the technical scheme, a method for manufacturing a floating body effect memory unit on the silicon-on-insulator silicon slice and capable of improving the data retention performance is provided, interface dangling bonds between the silicon dioxide thin film and the substrate can be increased, thereby electrons can be effectively trapped, and the data retention performance of the floating body effect memory unit in a p-channel metal oxide semiconductor (PMOS) structure is improved.

Owner:SHANGHAI HUALI MICROELECTRONICS CORP

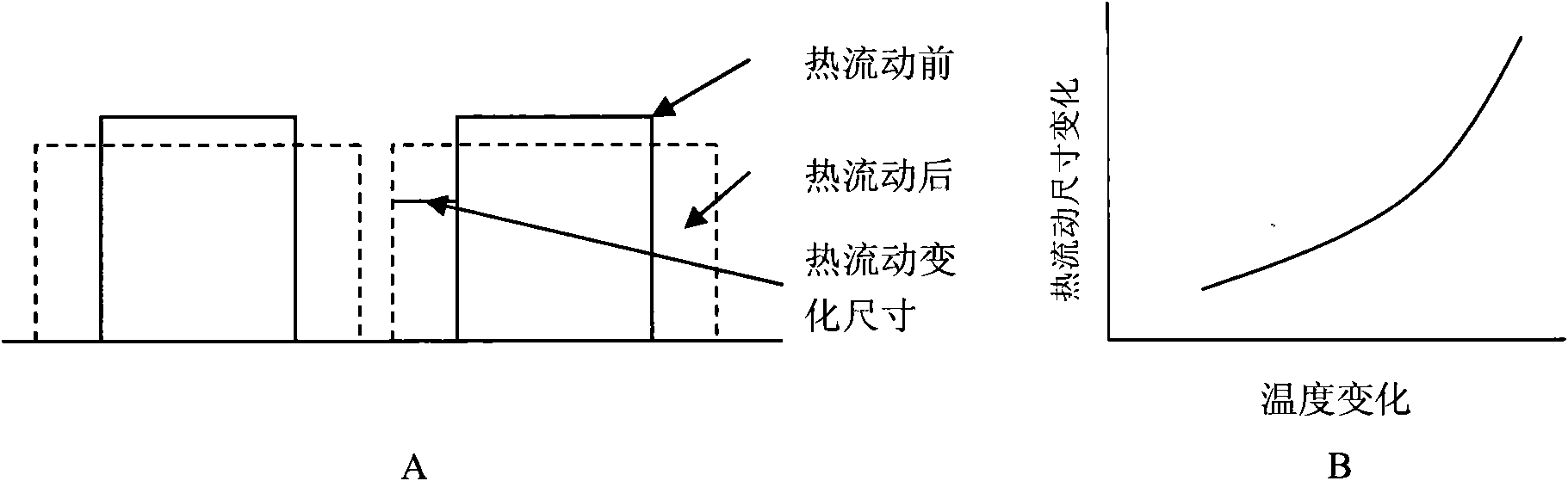

Manufacturing method for reducing area of SONOS storage unit

ActiveCN101924077AReduce lateral etchSmall unit areaSemiconductor/solid-state device manufacturingPhotomechanical coating apparatusGate oxideOxygen

The invention discloses a manufacturing method for reducing an area of an SONOS storage unit, comprising the following steps: (1) completely depositing SiO2 on a silicon substrate; (2), removing SiO2 in an SONOS pipe zone by photoetching and etching, and forming a SiO2 protective layer in a common transistor zone; (3) completely depositing an ONO three-layer film; (4) protecting the ONO zone of the SONO pipe by photoetching, and forming a SiO2 protective layer on the zone; (5) removing ON in the common transistor zone by dry etching; (6) carrying out heating on silicon wafers; (7) removing the rest of SiO2 in the common transistor zone by wet etching; and (8) forming a gate oxide and a grid electrode in the follow-up steps. The method can reduce horizontal etching of SiO2 on the upper layer of the ONO structure of the SONO storage in the wet etching, so that the distance between the SONOS pipe and the common transistor is shortened, thereby reaching the purpose of reducing the area.

Owner:SHANGHAI HUAHONG GRACE SEMICON MFG CORP

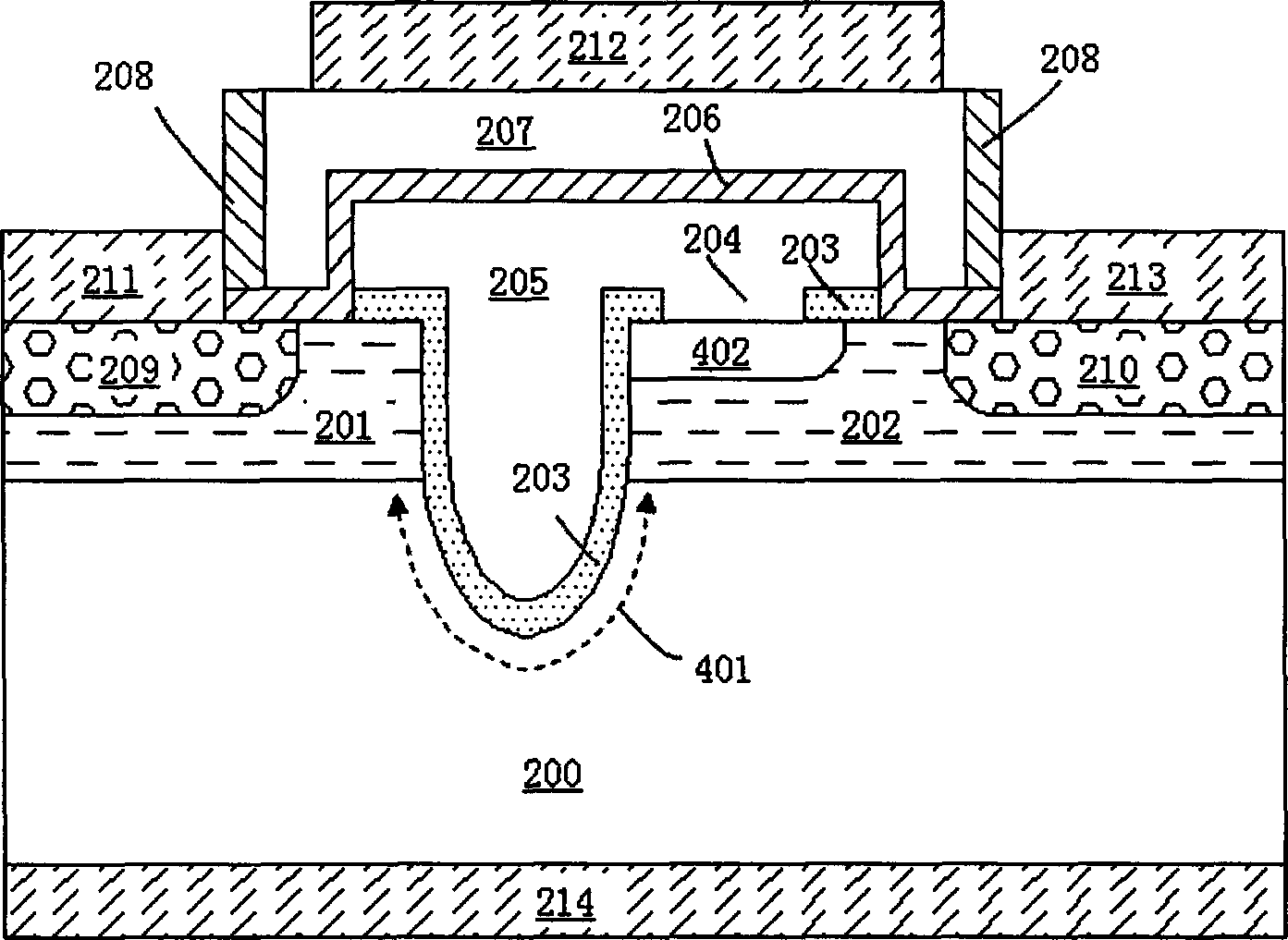

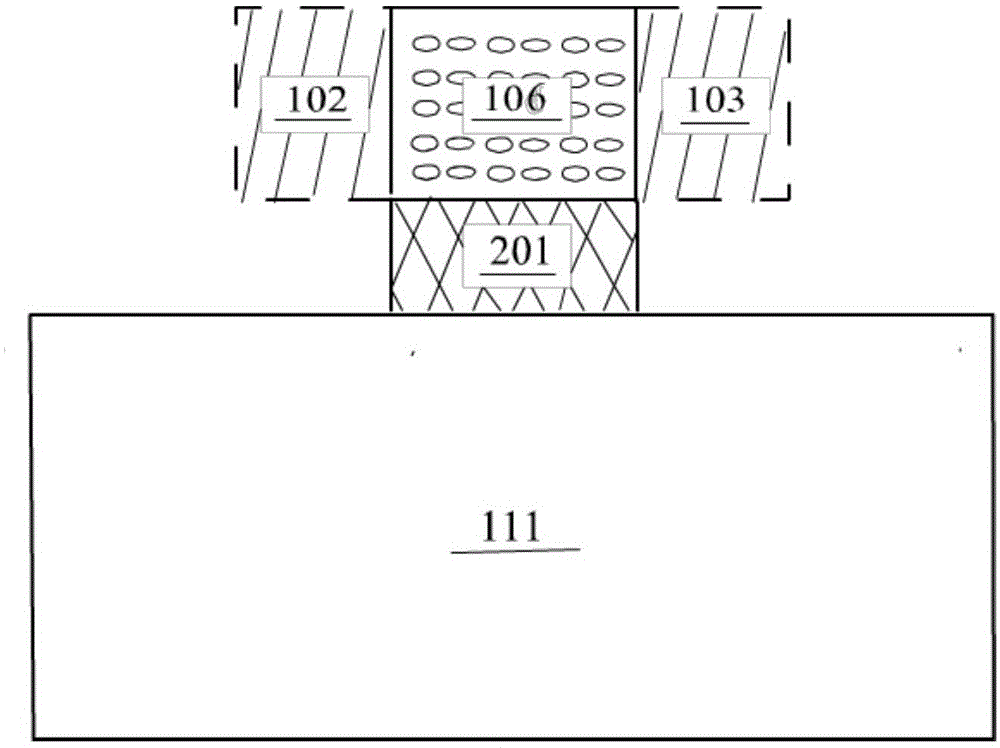

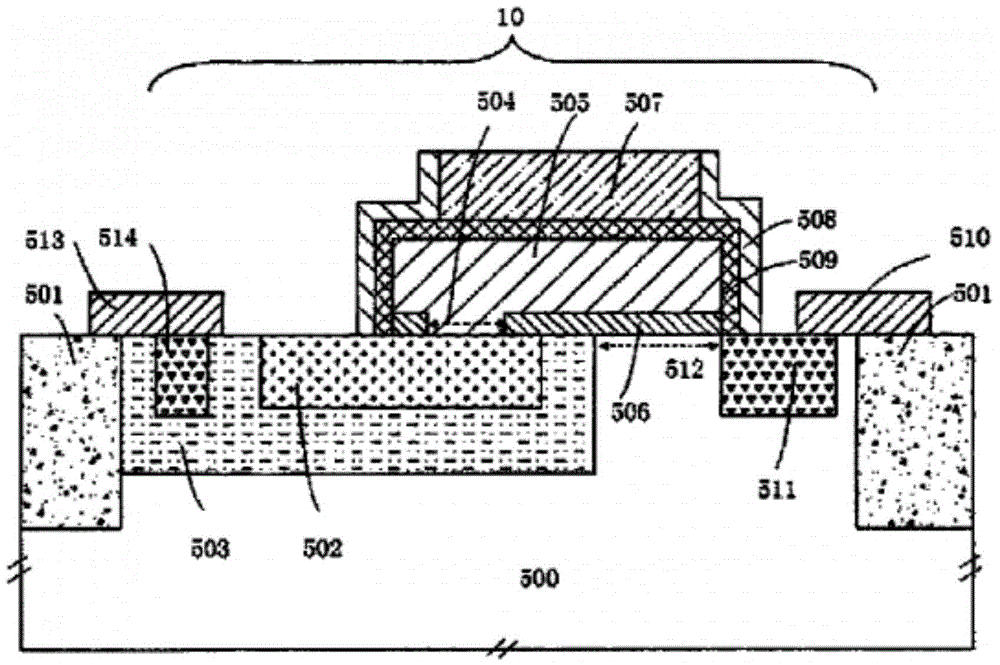

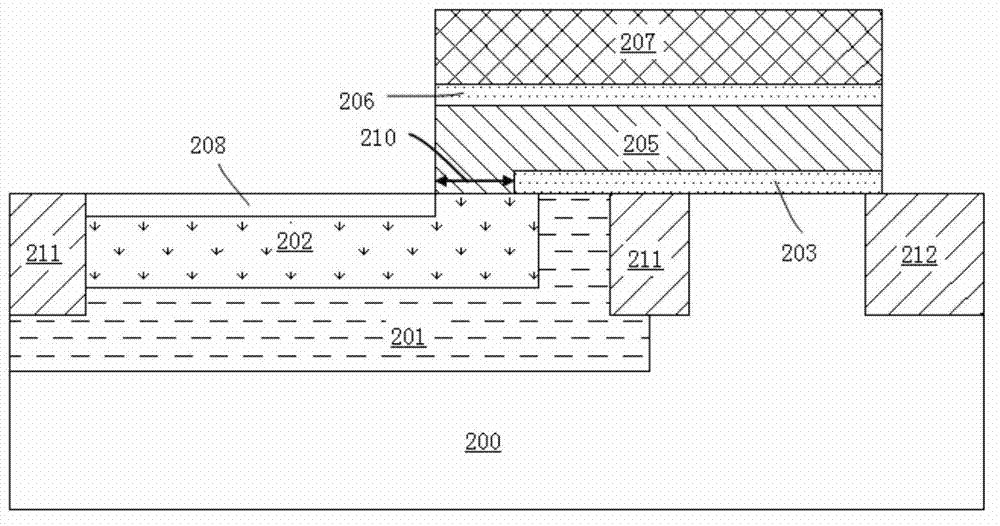

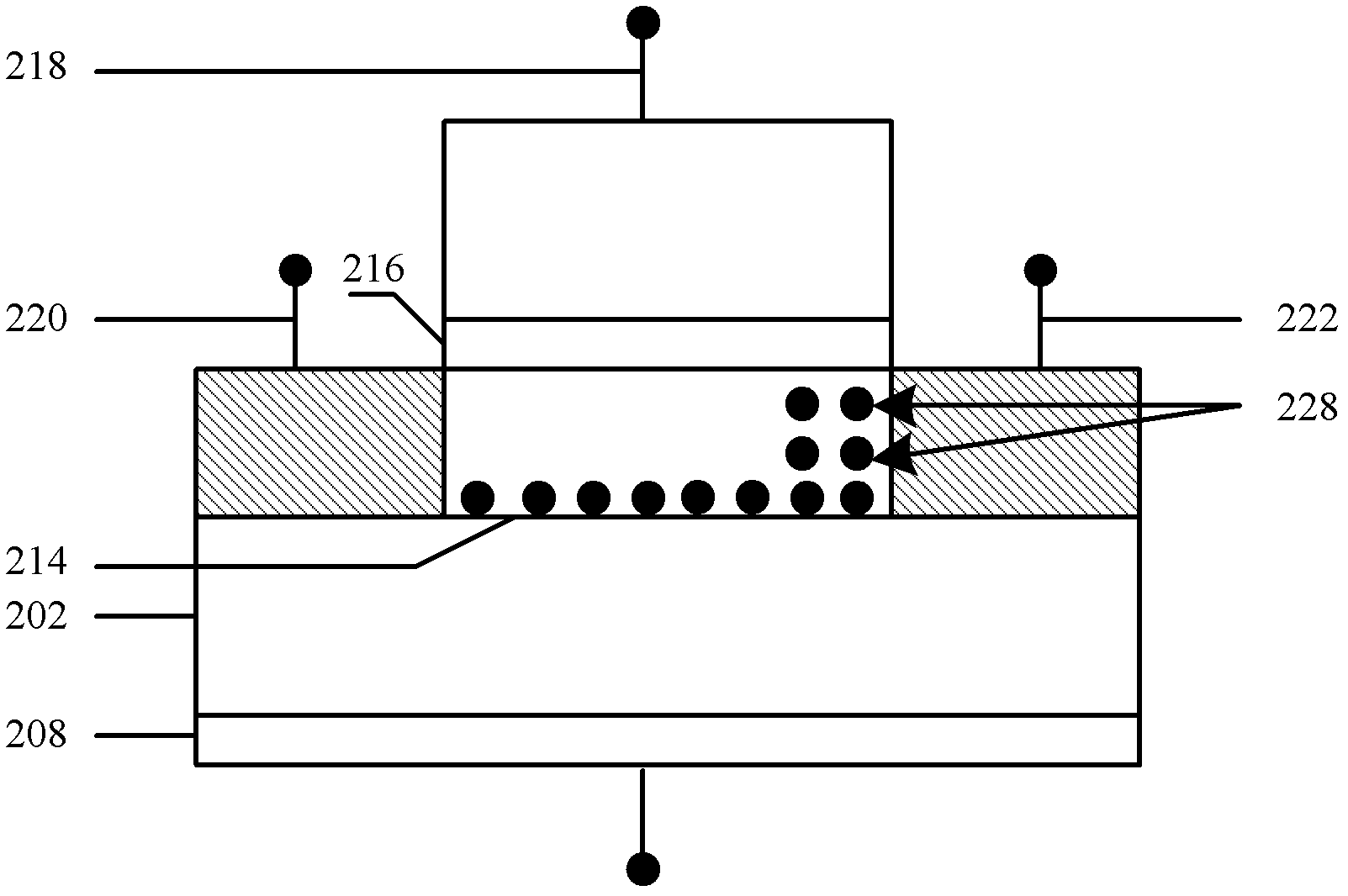

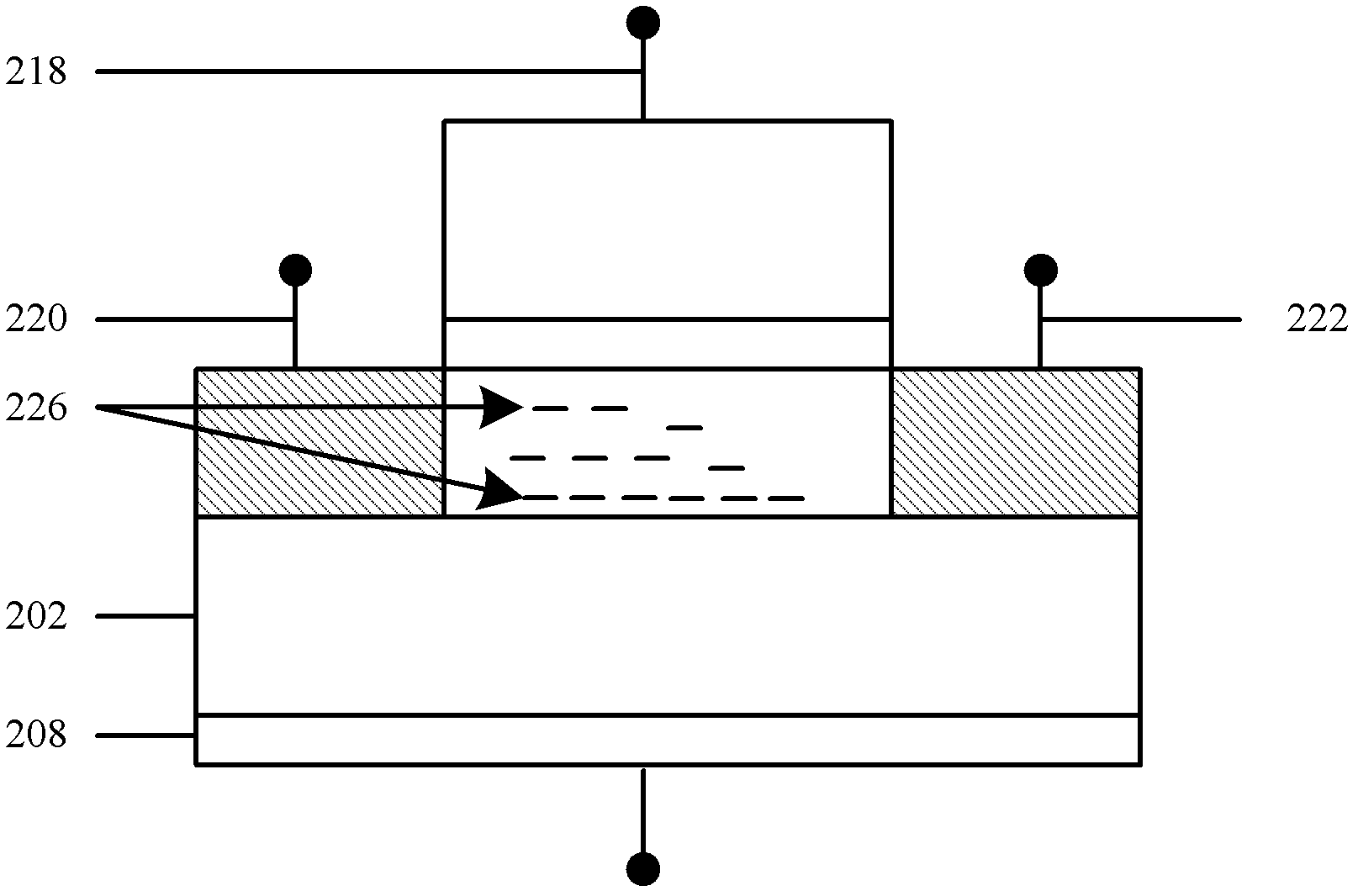

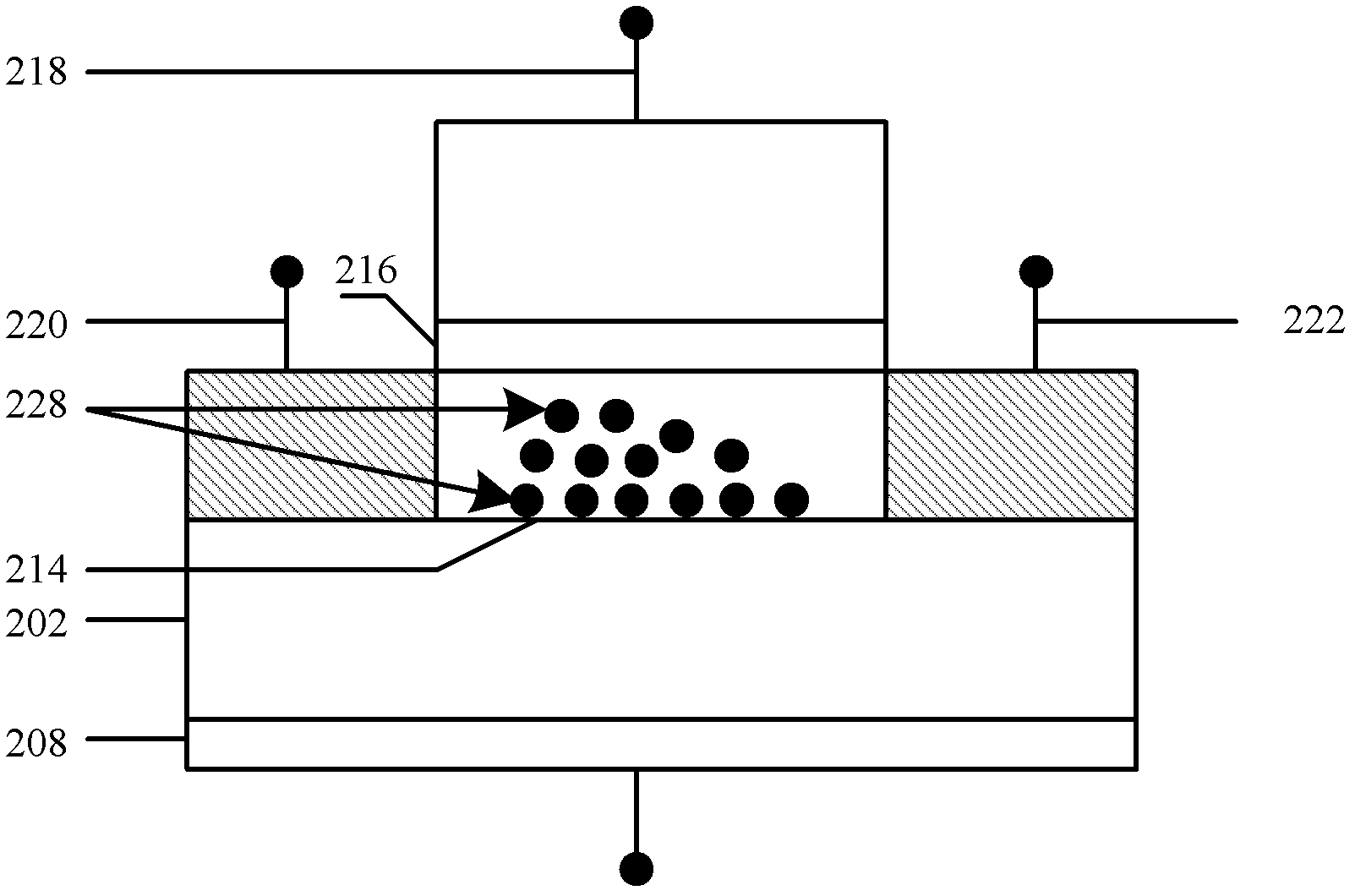

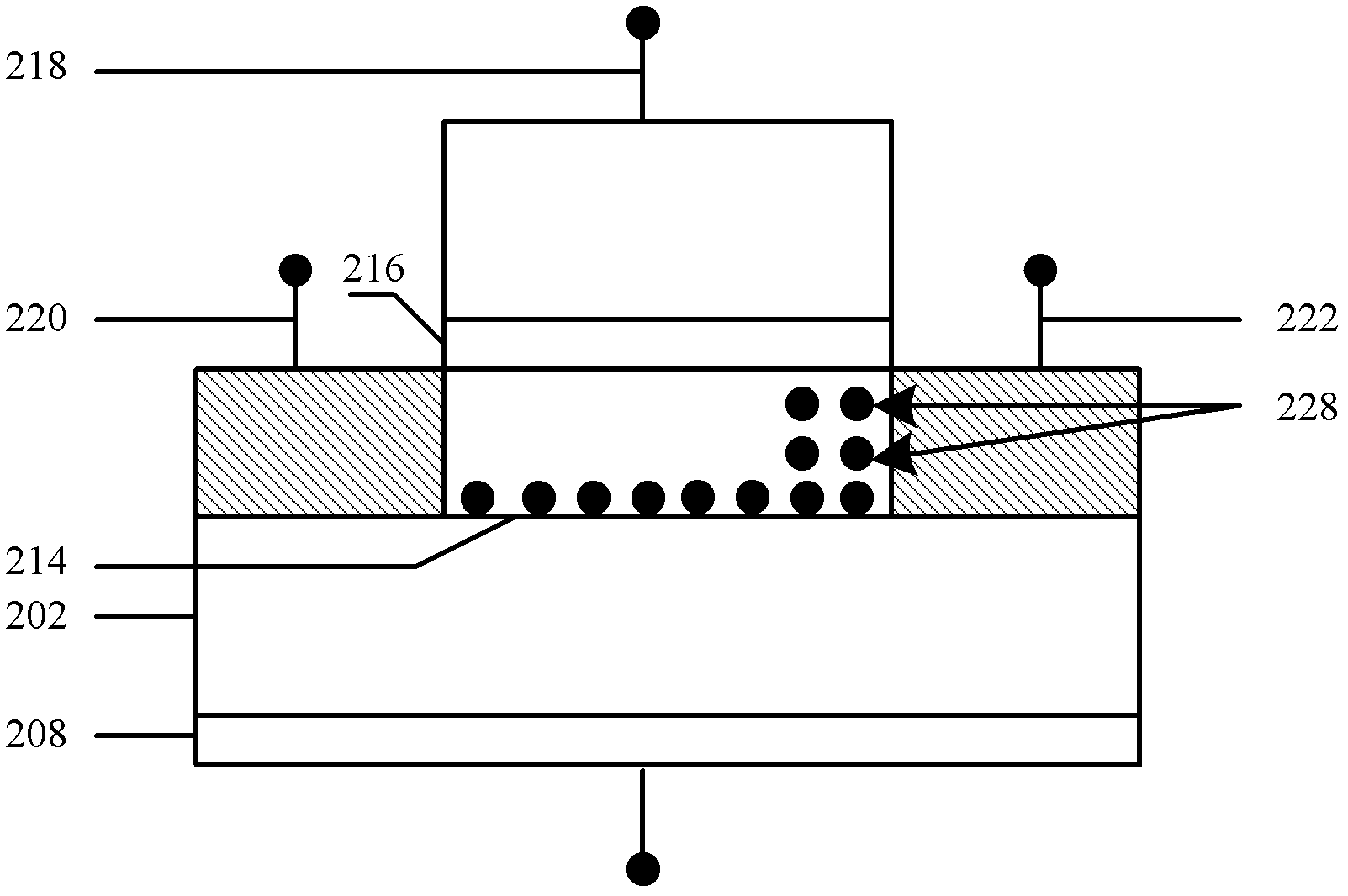

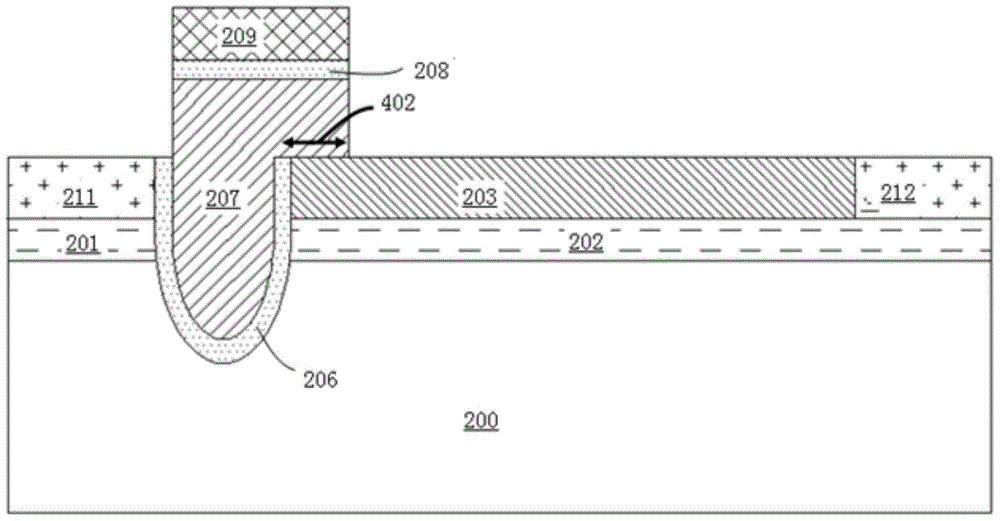

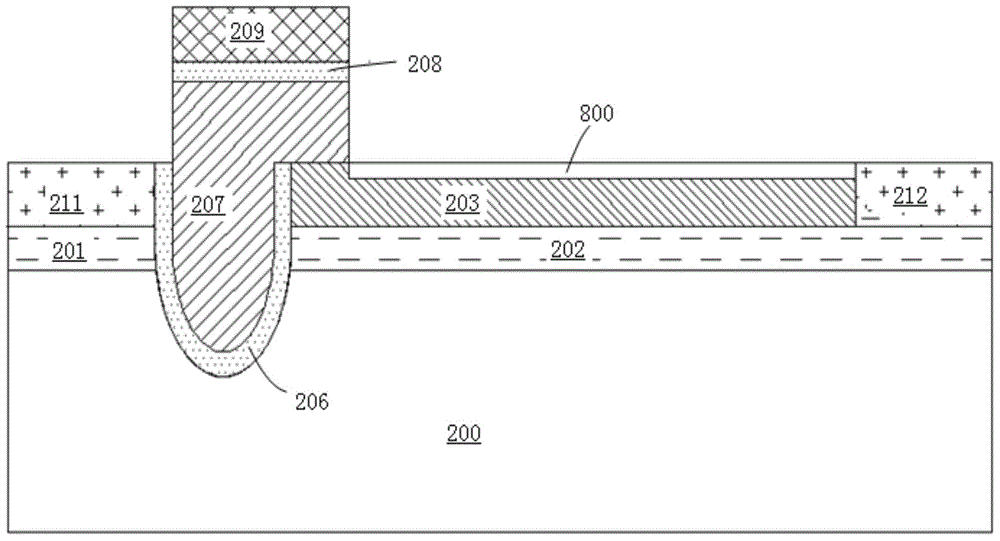

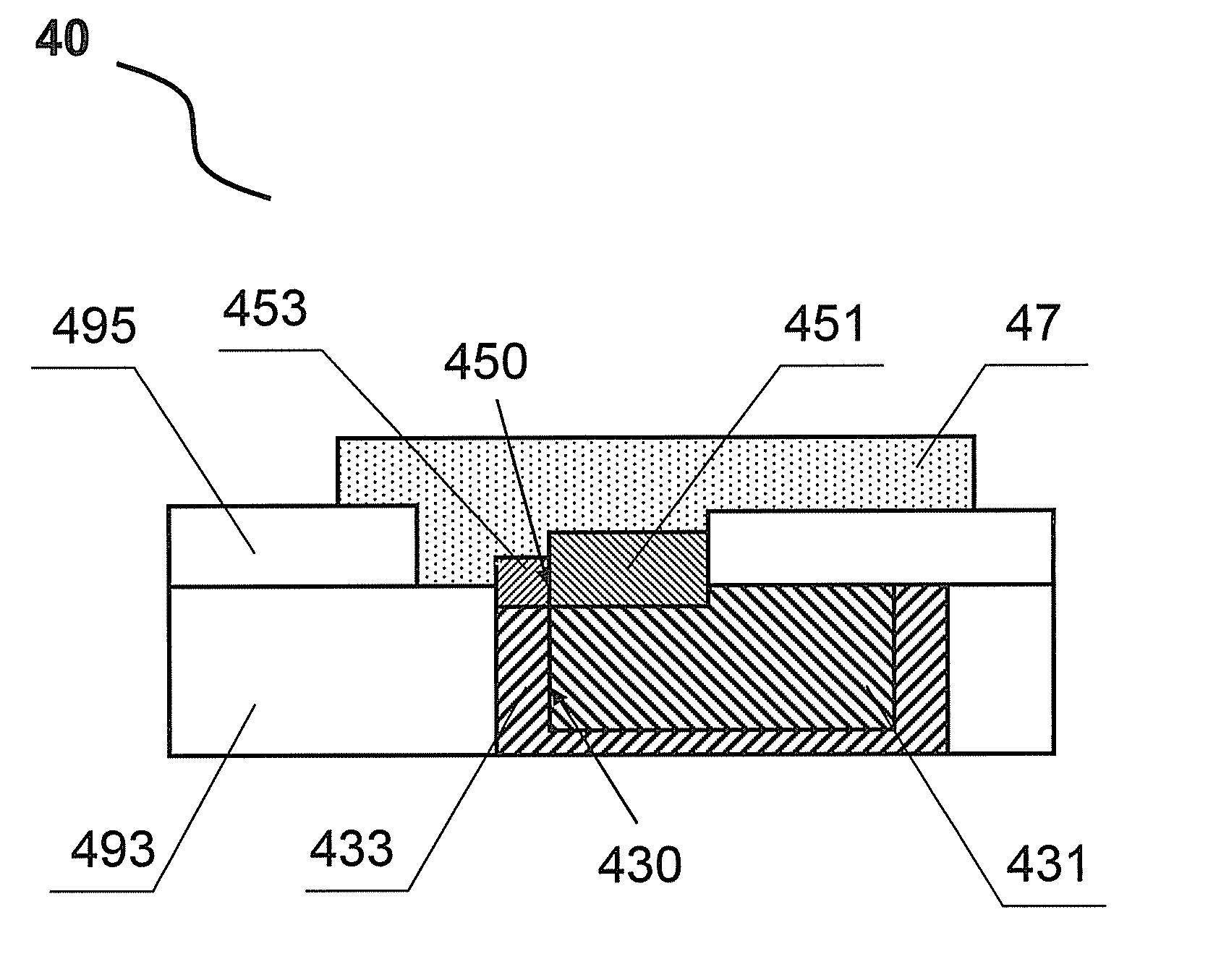

U-shaped channel semiconductor photosensitive device and manufacturing method thereof

ActiveCN104576665AShorten channel lengthSmall unit areaSemiconductor/solid-state device manufacturingRadiation controlled devicesOxide semiconductorImage resolution

The invention discloses a U-shaped channel semiconductor photosensitive device and a manufacturing method thereof. The U-shaped channel semiconductor photosensitive device comprises a U-shaped channel MOS (Metal Oxide Semiconductor) transistor formed in a semiconductor substrate, a photosensitive p-n junction diode and a pinning diode, wherein a floating gate of the U-shaped channel MOS transistor is connected with one end of the photosensitive p-n junction diode through a floating gate opening and is also connected with one end of the pinning diode; a drain region of the U-shaped channel MOS transistor is connected with the other end of the photosensitive p-n junction diode and is also connected with the other end of the pinning diode. The U-shaped channel semiconductor photosensitive device disclosed by the invention has the advantages of small unit area, high chip density, high sensitivity and the like, and the resolution ratio of an image sensor chip is increased.

Owner:SUZHOU ORIENTAL SEMICONDUCTOR CO LTD

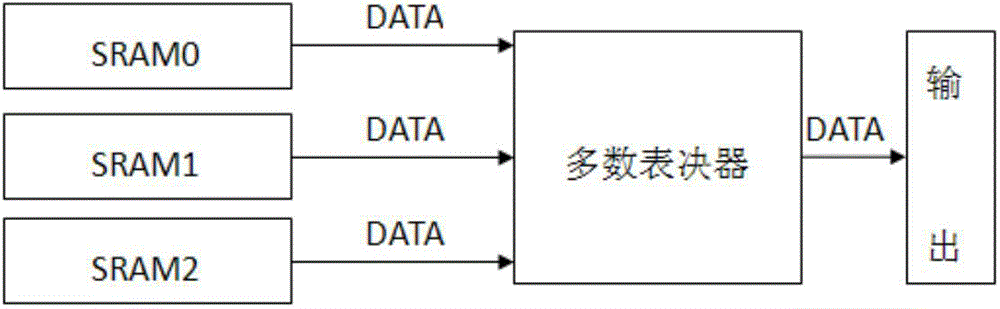

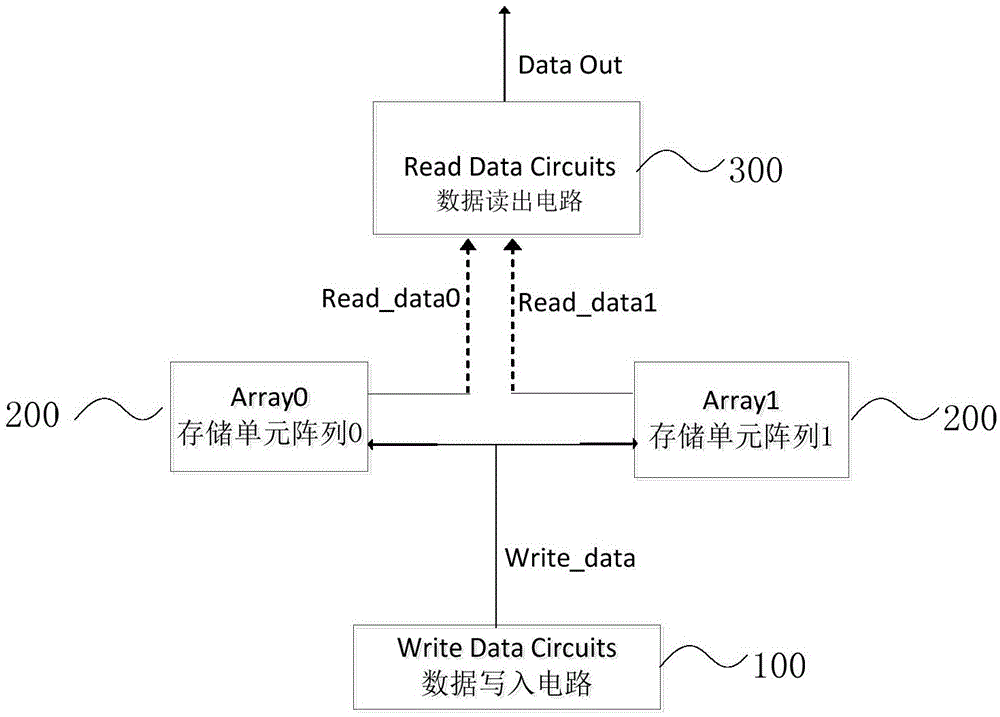

Random access memory with redundant structure

ActiveCN104637530AAccelerateSmall unit areaDigital storageLow complexityDynamic random-access memory

The invention discloses a random access memory with a redundant structure. The random access memory comprises two same memory unit arrays, a data writing circuit and a data reading circuit, wherein the two same memory unit arrays have same array frameworks; memory units at the same address in the arrays have the same initial memory information; the data writing circuit is used for simultaneously writing the same data into the memory units at the same addresses in the two same memory arrays; and the data reading circuit is used for selecting memory information in the memory units at the same addresses in the two memory unit arrays, outputting 0 when the memory information in the two memory units is not different and outputting the same memory information when the memory information in the two memory units is the same. The random access memory has the advantages of small hardware area, low complexity, stable and reliable data storage and the like.

Owner:TSINGHUA UNIV +1

A metallized safety film

PendingCN109243825ASmall unit areaReduce capacity lossFixed capacitor electrodesWound capacitorsEdge regionVoltage

The invention relates to a metallized safety film made by laminating and winding double-sided metallized film, the metallized thin film layer comprises a base film and a fully metallized conductive layer arranged on the base film, One side of the base film is provided with a reserved edge region, and the side opposite to the reserved edge region, of the base film is provided with a thickened region. The thickened region and the all-metallized conductive layer are spaced apart by an isolation region, and a conductive grid region is arranged on the upper part of the all-metallized conductive layer near the thickened region. Compared with the existing double-layer safety film winding, the utility rate of the base film is improved by 2.5%, the safety performance is improved, the high square resistance all-metallized conductive layer improves the self-healing property, the voltage resistance is high, the ripple resistance is strong, and the service life is long under the condition of the same safety performance.

Owner:DELIXI ELECTRIC

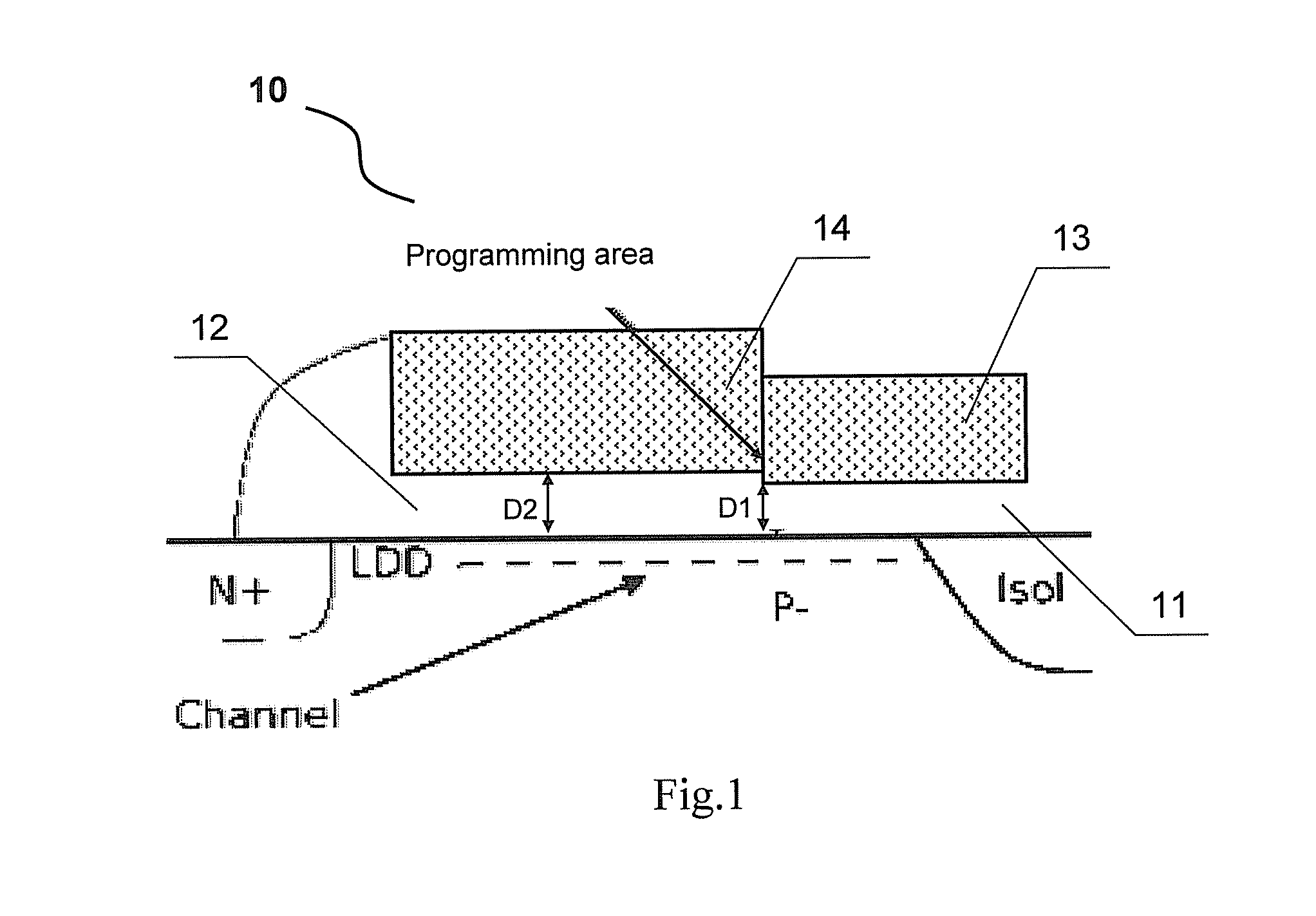

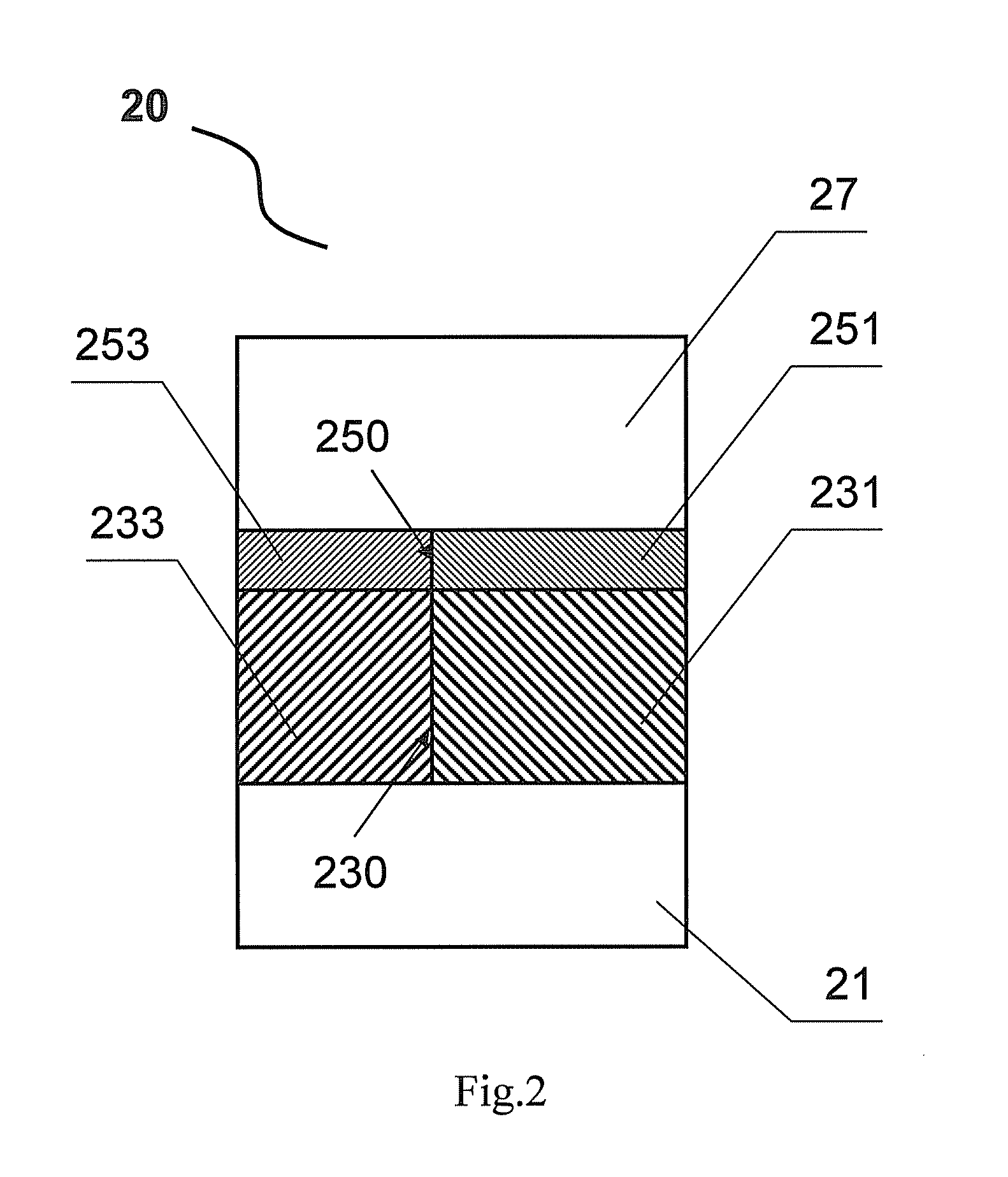

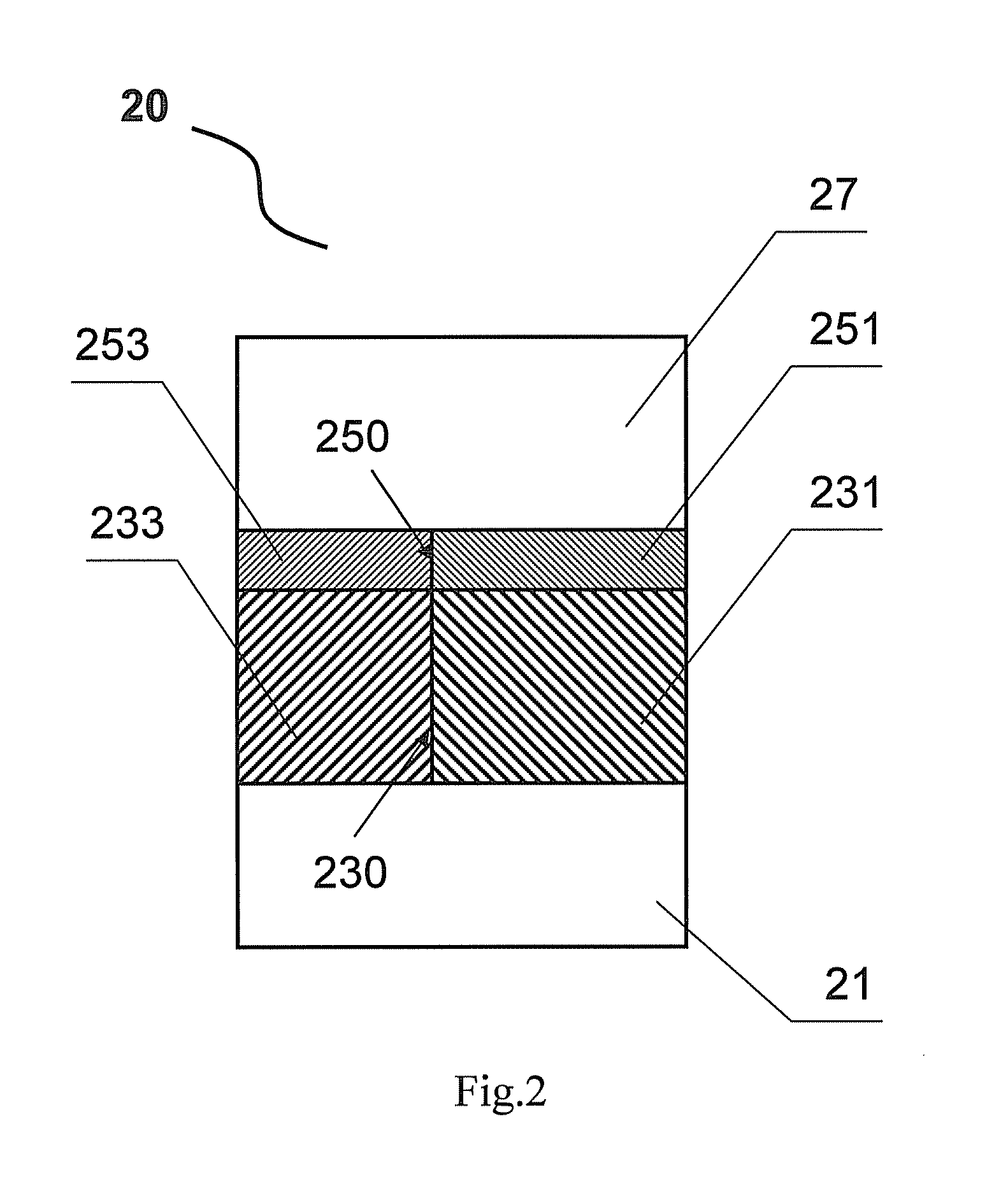

One-Time Programmable Memory Cell, Memory and Manufacturing Method Thereof

InactiveUS20130163306A1Low programming voltageReduce voltageTransistorSemiconductor/solid-state device detailsOptoelectronicsMedia layer

The present invention pertains to the technical field of one-time programmable memory (OTP), and in particular to a one-time programmable memory unit, OTP, and method of fabricating the same. The OTP unit comprises a lower electrode, an upper electrode and a storage medium layer placed between the upper electrode and the lower electrode, the storage medium layer comprises a first metal oxide layer and a second metal oxide layer, wherein an adjoining area for programming is formed between the first metal oxide layer and the second metal oxide layer. The OTP comprises a plurality of the above-described one-time programmable memory units arranged in rows and columns. The OTP unit and the OTP have such characteristics as low programming voltage, small unit area, being able to integrate into a back-end structure of integrated circuit, great process flexibility, and the method of fabricating the OTP unit and the OTP is relatively simple and low in cost.

Owner:FUDAN UNIV

Method for manufacturing silicon-on-insulator silicon slice and floating body dynamic random access memory unit

ActiveCN102969268BKeep for a long timeSmall unit areaSemiconductor/solid-state device manufacturingFloating body effectSilicon dioxide

The invention provides a method for manufacturing a silicon-on-insulator silicon slice. The method includes the following steps that a silicon dioxide thin film and a substrate are formed in a first silicon slice; the first silicon slice is subjected to nitric oxide annealing process to form numerous dangling bonds at an interface position between the silicon dioxide thin film and the substrate; the first silicon slice is subjected to hydrogen ion implantation, a buried layer rich in hydrogen ions is formed in the substrate; a second silicon slice is bonded on the silicon dioxide thin film of the first silicon slice; and bonded silicon slices are subjected to thermal treatment, and the first silicon slice is stripped from the position of the buried layer rich in hydrogen ions to form the silicon-on-insulator silicon slice. By means of the technical scheme, a method for manufacturing a floating body effect memory unit on the silicon-on-insulator silicon slice and capable of improving the data retention performance is provided, interface dangling bonds between the silicon dioxide thin film and the substrate can be increased, thereby electrons can be effectively trapped, and the data retention performance of the floating body effect memory unit in a p-channel metal oxide semiconductor (PMOS) structure is improved.

Owner:SHANGHAI HUALI MICROELECTRONICS CORP

One-time programmable memory cell, memory and manufacturing method thereof

InactiveUS9019741B2Reduce voltageEasily brokenTransistorSemiconductor/solid-state device detailsOptoelectronicsMedia layer

Owner:FUDAN UNIV

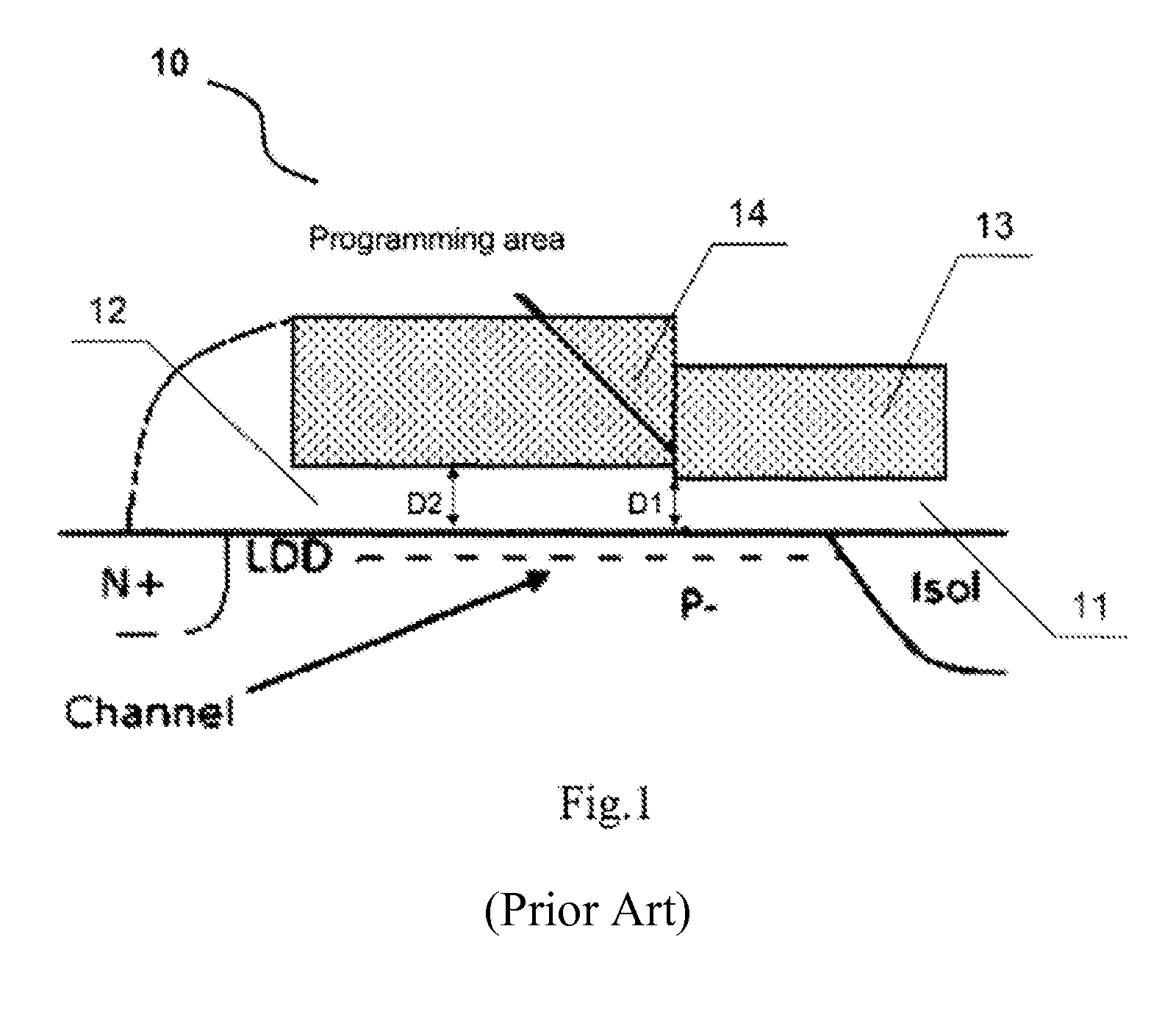

Flash memory device with single-poly structure and method for manufacturing the same

InactiveCN101140910ASmall unit areaSolid-state devicesSemiconductor/solid-state device manufacturingSilicon nitridePolycrystalline silicon

A flash memory device has a single-poly structure. A method for manufacturing the flash device includes forming an oxide layer over a semiconductor substrate having a P-well region or N-well region. A shallow trench isolation (STI) may be formed in the semiconductor substrate and the oxide layer. A drift region may be formed by injecting a dopant into a part of the P-well region or N-well region. A gate oxide layer and a poly-silicon layer may be formed over the well region, the drift region, and the STI. A control gate pattern may be formed by patterning the gate oxide layer and the poly-silicon layer. A source region and a drain region may be formed on opposite sides of the control gate pattern. A silicon nitride layer may be deposited over the control gate pattern and etching the silicon nitride layer to form a spacer around a sidewall of the control gate pattern. A plurality of insulating layers may be formed over the control gate pattern, and via-patterns may be electrically connected to the source region and the drain region, respectively. A drain electrode and a source electrode may be electrically connected to the via-patterns, respectively.

Owner:DONGBU HITEK CO LTD

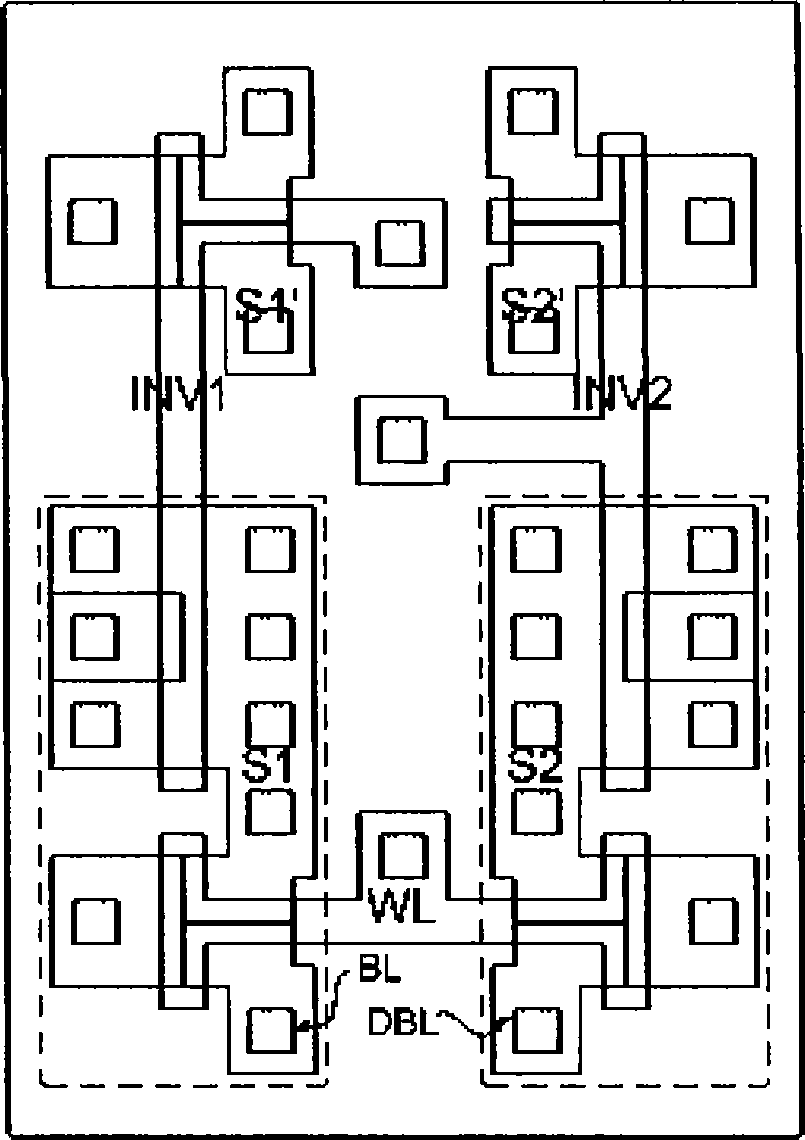

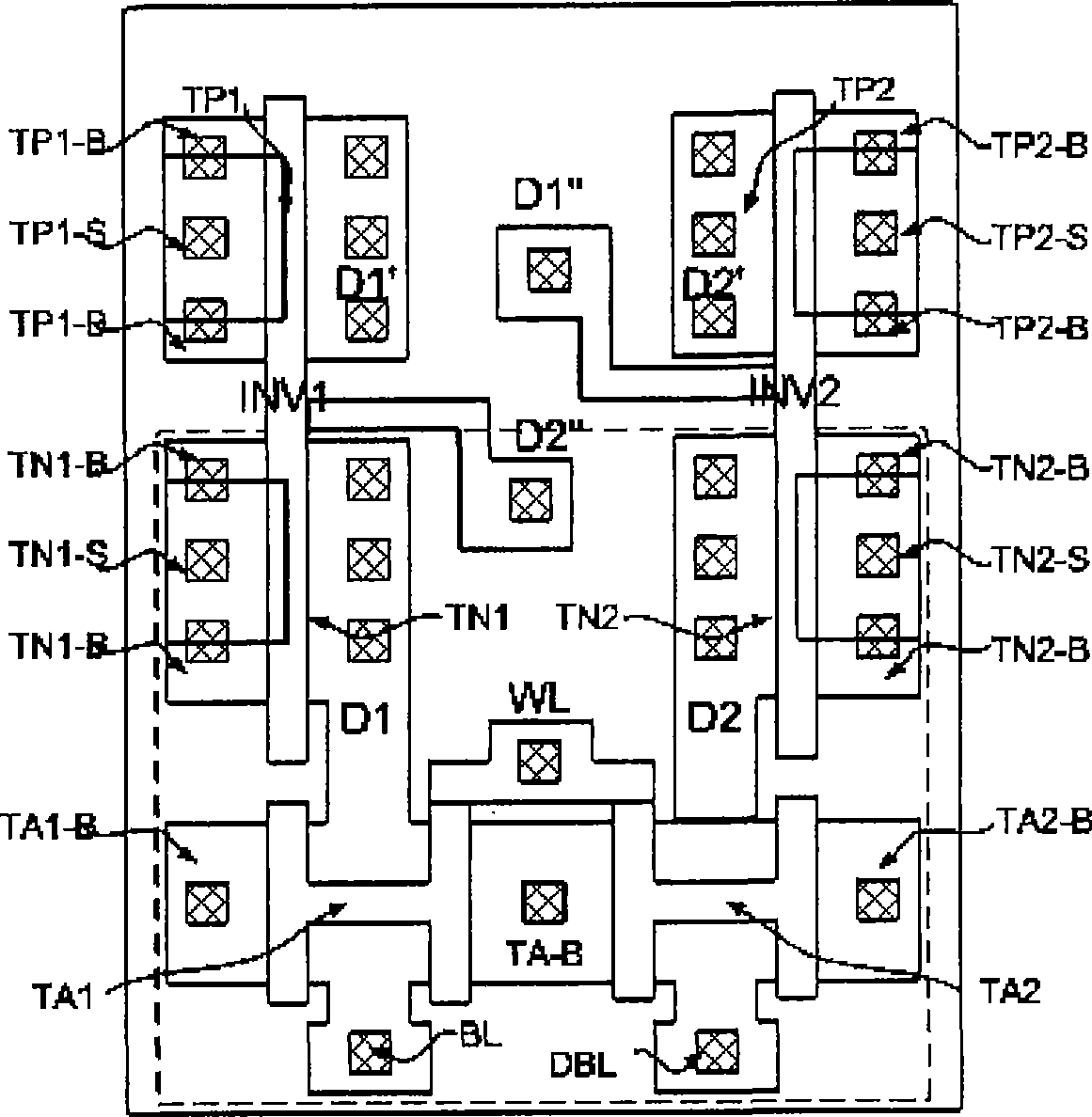

Improved memory cell for silicon static state stochastic memory of part depletion isolator

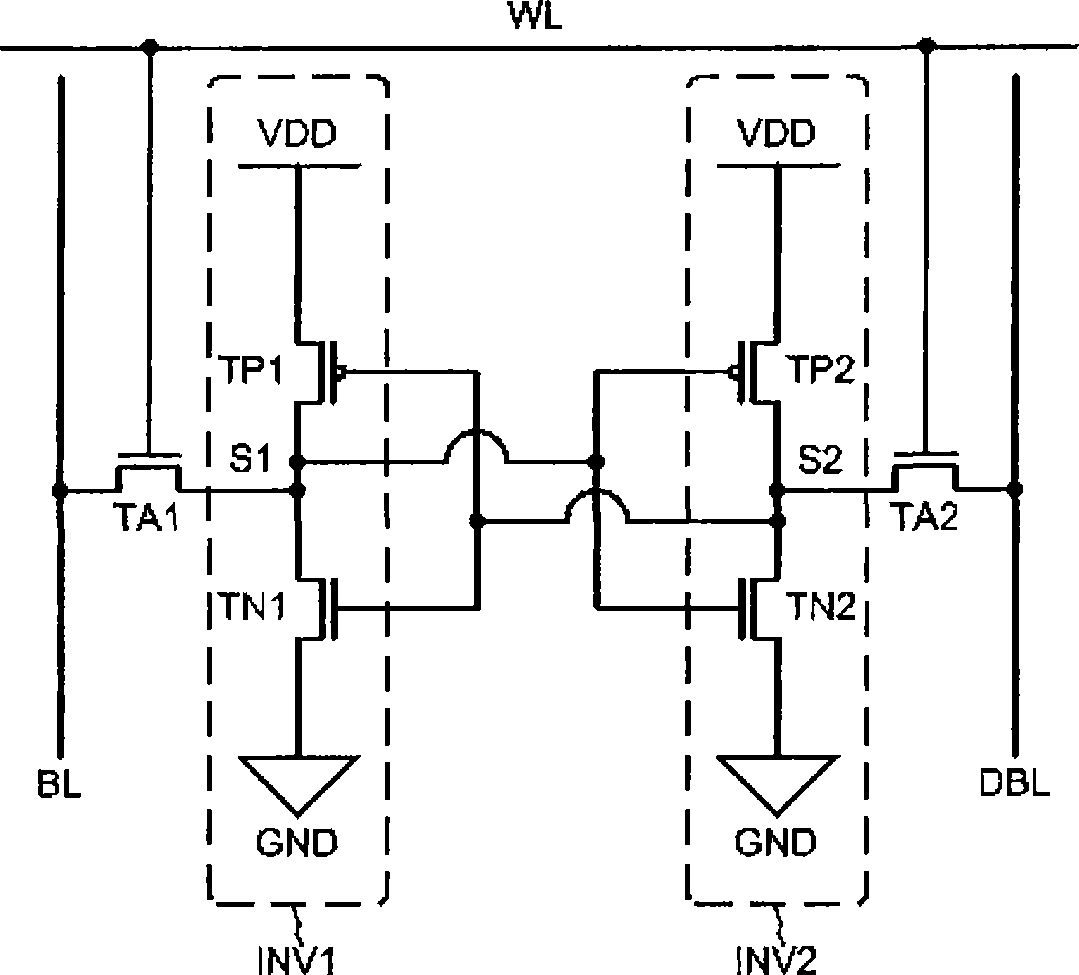

InactiveCN101442055AReduce power consumptionImprove the ability to deal with complex radiation environmentsSemiconductor/solid-state device detailsSolid-state devicesFloating body effectStatic random-access memory

The invention provides a storage unit for improving a static random access memory formed on a partially depleted SOI substrate, which relates to the technology of the static random access memory. The SRAM unit comprises six transistors, namely a first access NMOS transistor, a second access NMOS transistor, a first drive NMOS transistor, a second drive NMOS transistor, a first load PMOS transistor and a second load PMOS transistor. When body-area contact processing is carried out, T-type gate technology is not adopted, the NMOS transistors are accessed by an H-type gate body contact, and the load PMOS transistors and the drive NMOS adopt BTS-A type gate body contact. Therefore, not only floating body effect caused by the partially depleted SOI material can be avoided, but also island side creepage caused by a T-type gate structure can be inhibited. Two groups of inverters in the unit are linked in the middle of the unit so as to simplify cabling and reduce area of the unit. The storage unit improves the final performance of a chip.

Owner:INST OF SEMICONDUCTORS - CHINESE ACAD OF SCI