Improved memory cell for silicon static state stochastic memory of part depletion isolator

A storage unit, static random technology, applied in the direction of electric solid state devices, semiconductor devices, electrical components, etc., can solve the problems of increasing the static power consumption of the chip, increasing the leakage current, and the power consumption of the latch-up effect, so as to avoid the floating body effect and reduce the power consumption. The effect of simplifying power consumption and wiring

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment Construction

[0026] The content of the present invention is described in detail below through the accompanying drawings, so that the features and advantages of the present invention become clearer. These drawings include:

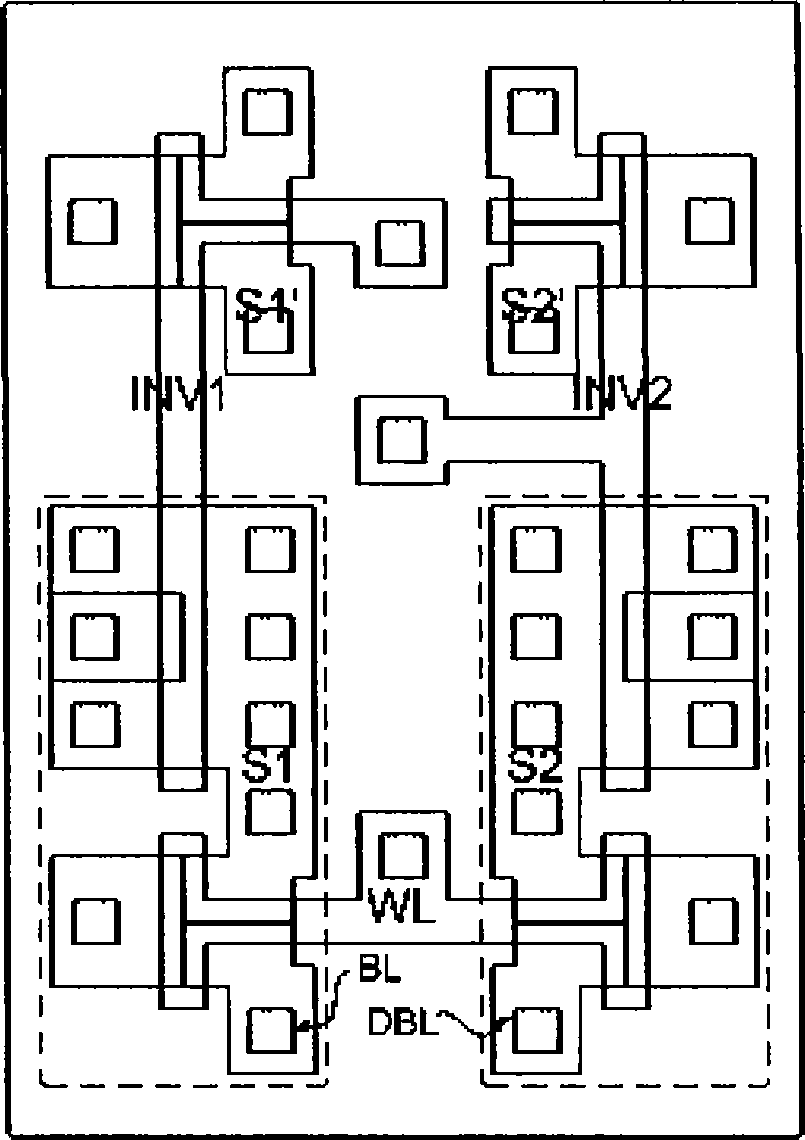

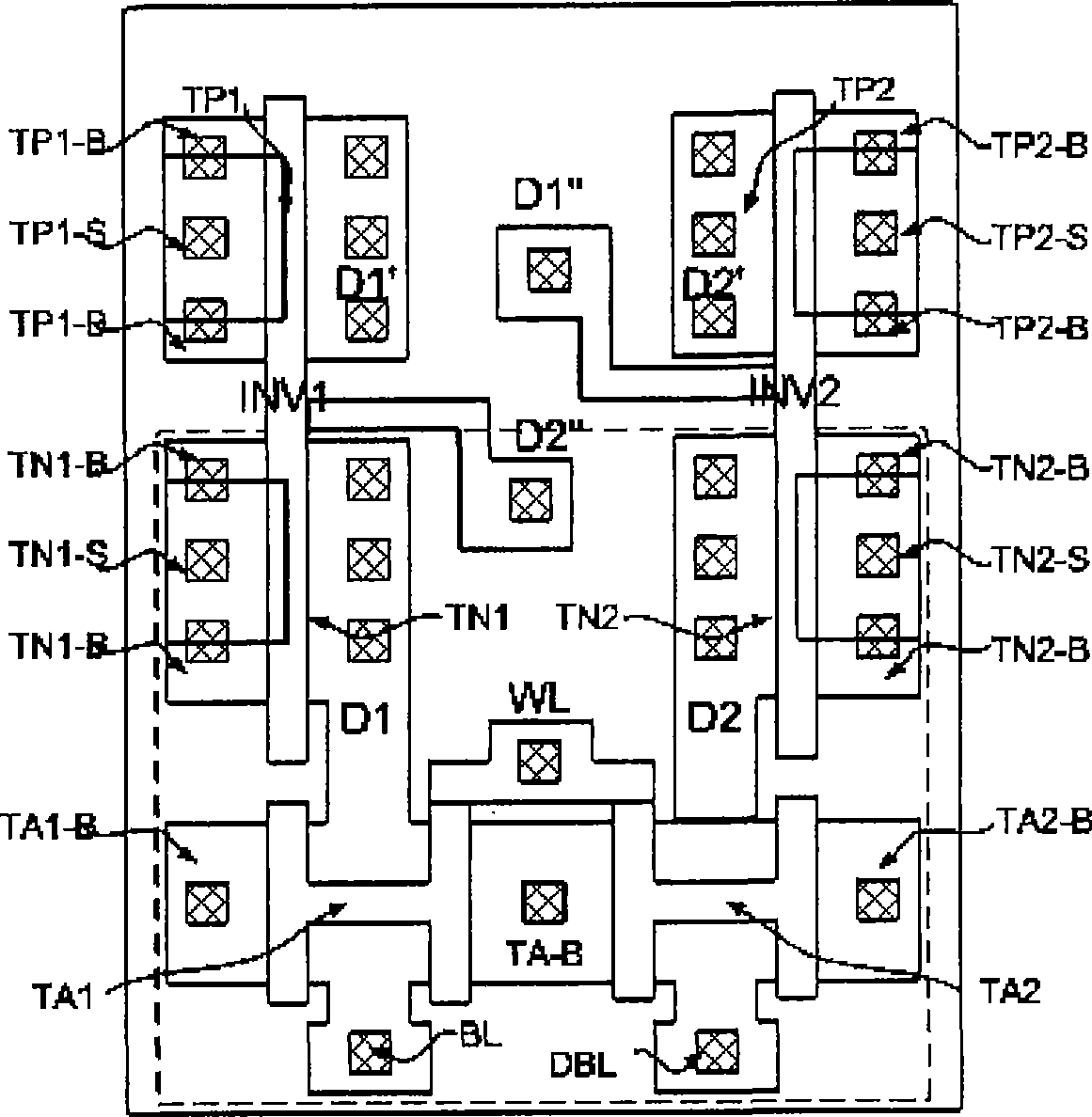

[0027] image 3 Shown is the improved PDSOI six-transistor memory cell of the present invention, attention should be paid to the body extraction method of the six transistors, especially the H-type gate body extraction structure used for accessing NMOS transistors.

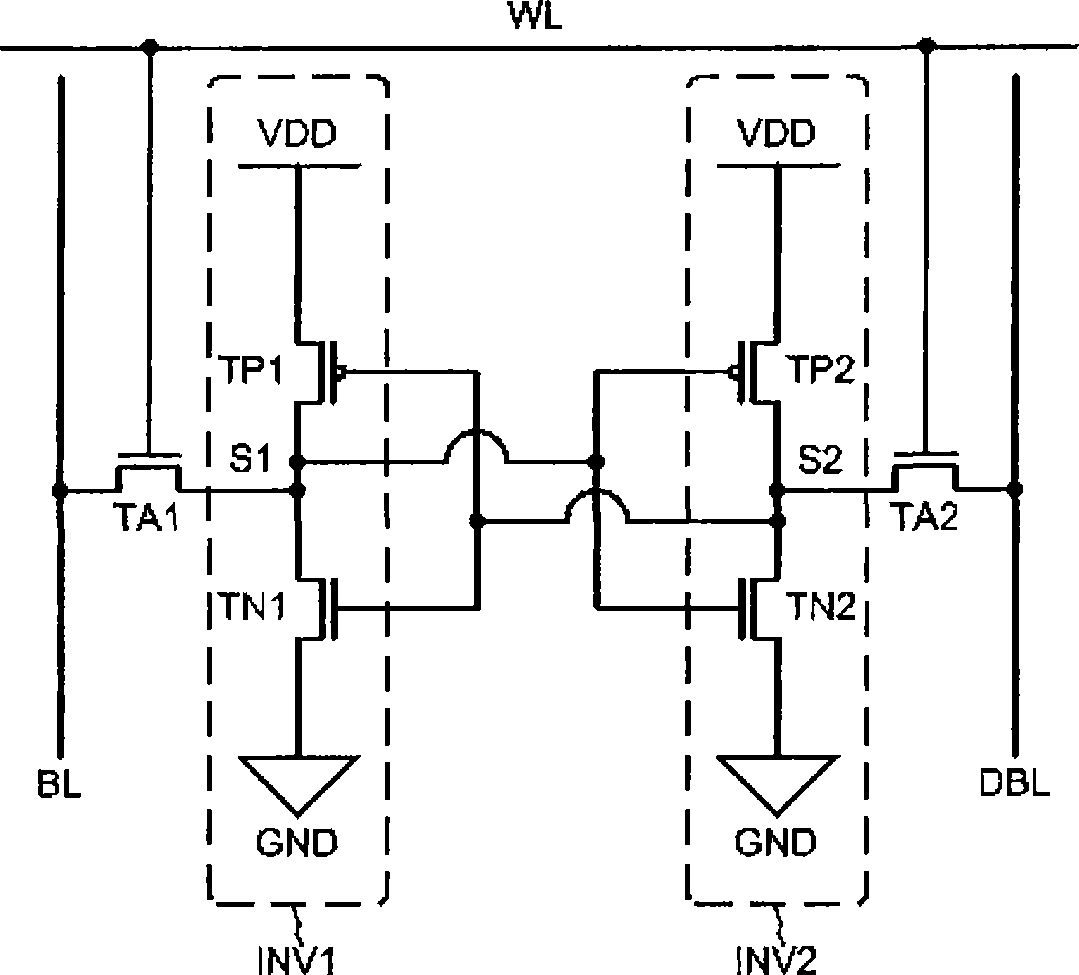

[0028] Figure 4 Shown is image 3 In the circuit connection diagram of the SRAM unit of the present invention, the body region of each transistor is connected to a corresponding fixed potential.

[0029] As shown in the figure, a CMOS SRAM cell with six transistors formed on a partially-depleted (PD) silicon-on-insulator (SOI) substrate.

[0030] The unit is implemented on a partially depleted silicon-on-insulator (PDSOI) substrate, and the six transistors are all subjected to body contact processing. A...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More