Method and device for outputting base station master clock

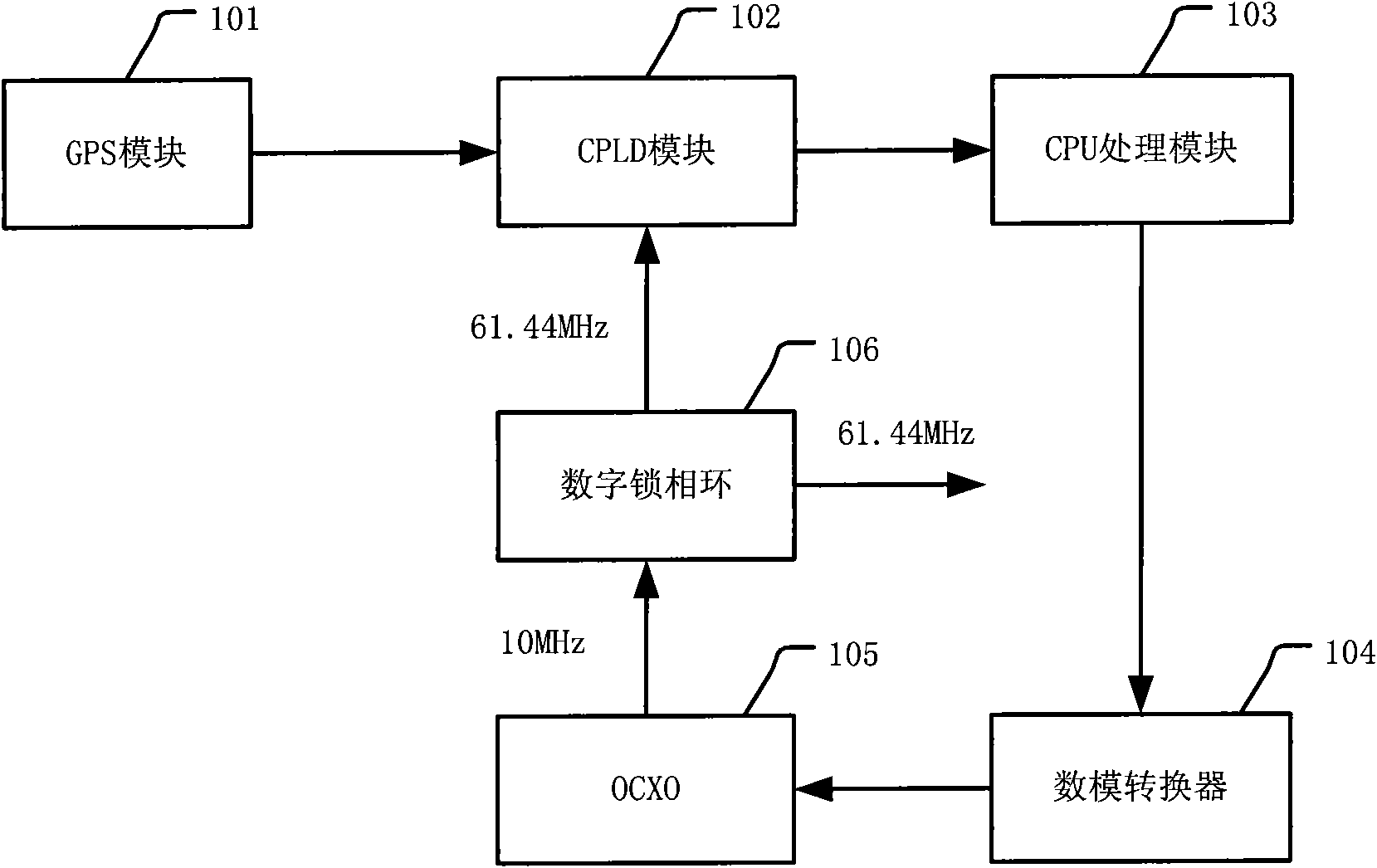

A technology for outputting clocks and master clocks, applied in synchronization devices, electrical components, wireless communications, etc., can solve problems such as clock deterioration, affecting system master clock output, high-frequency and low-frequency phase noise uncertainty of digital phase-locked loops, etc.

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment Construction

[0032] The core idea of the present invention is to dynamically adjust the working parameters of the loop filter of the digital phase-locked loop, calculate the corresponding clock jitter, find the loop filter working parameters that make the jitter of the main clock of the base station relatively small, and make the loop The filter works under this parameter, so as to obtain the master clock of the base station with relatively small phase noise and jitter.

[0033] In order to make the technical solution of the present invention clear and understandable, the technical principle of the present invention is introduced first.

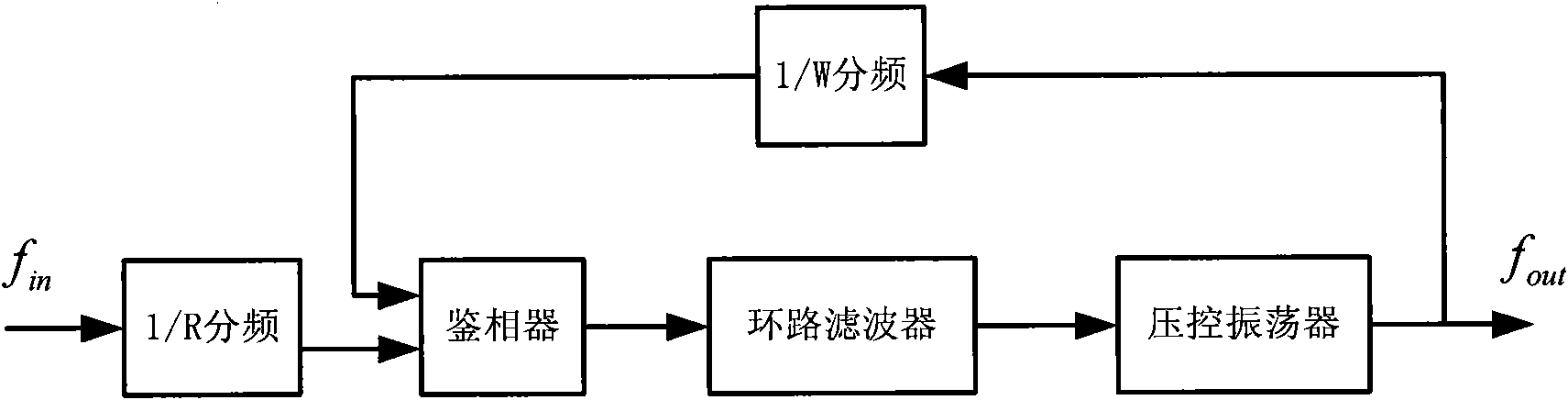

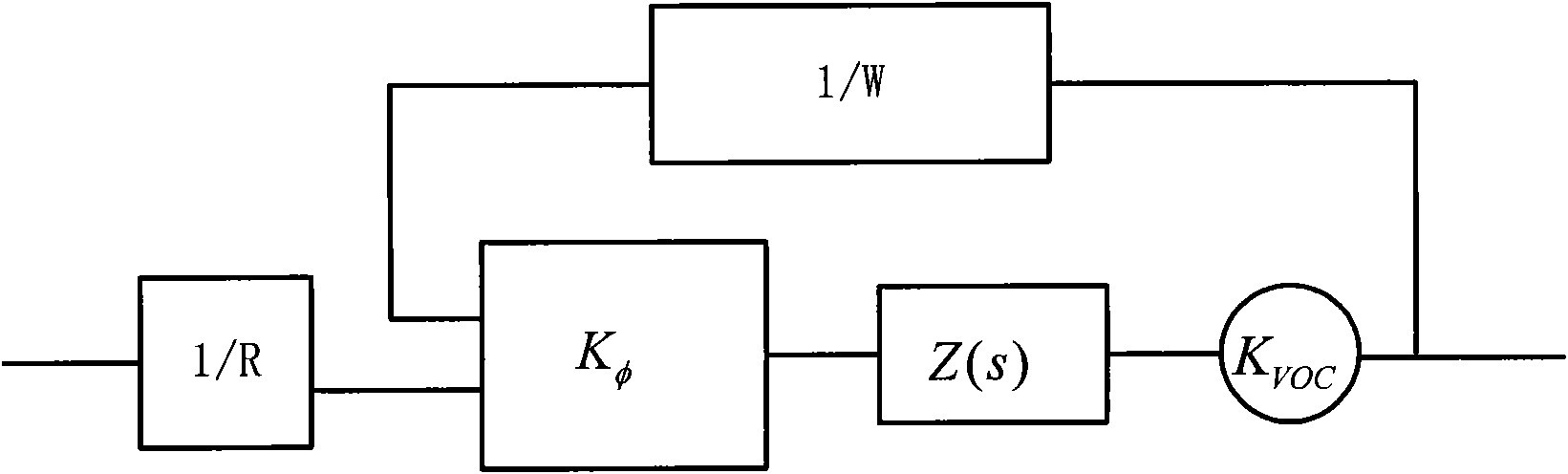

[0034] figure 2 It is the internal structure diagram of the digital phase-locked loop. Such as figure 2 As shown, the digital phase-locked loop is mainly composed of a phase detector (PD), a filter and a voltage-controlled oscillator (VOC). In practice, a digital phase-locked loop chip CDCE62005 is usually used, which integrates a phase detector, a...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More