Method for physically implementing special integrated circuit chip under deep sub-micron

A deep submicron, integrated circuit technology, applied in the direction of electrical digital data processing, special data processing applications, instruments, etc., can solve the problems of timing convergence, inability to predict, transistor threshold voltage shrinkage, etc., and achieve good practical results Effect

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment Construction

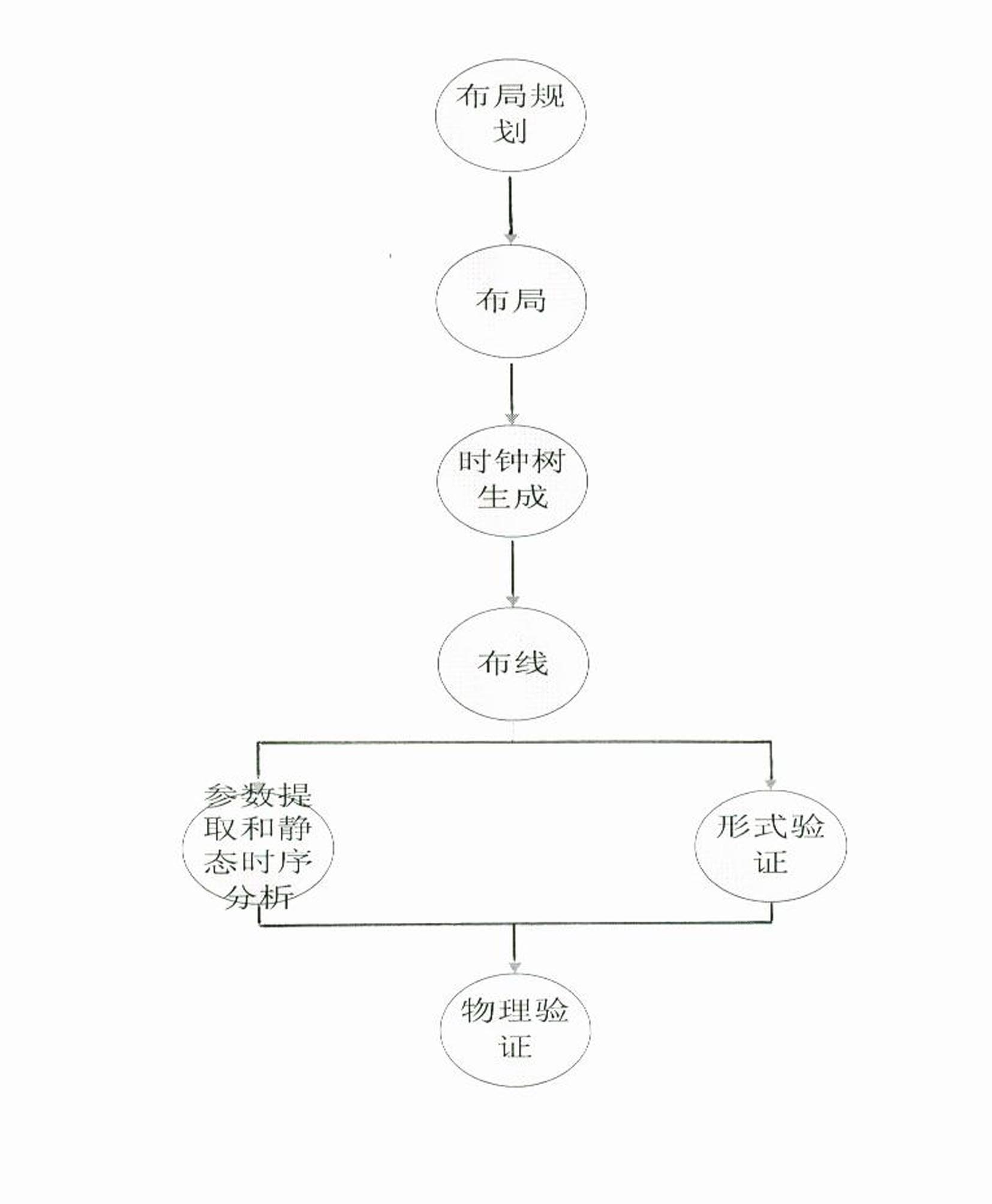

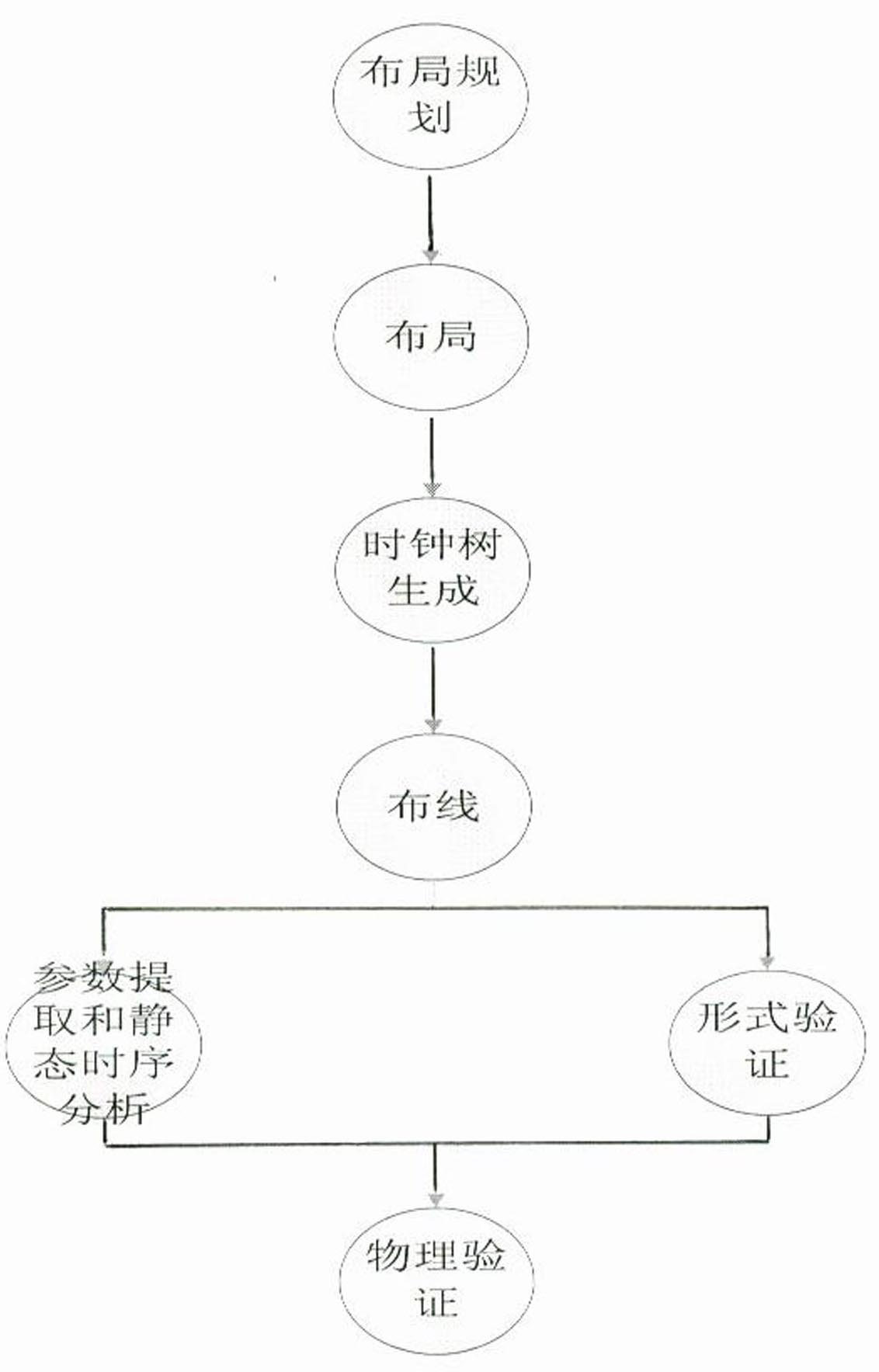

[0009] The present invention will be described in detail below in conjunction with accompanying drawing: figure 1 Shown: the physical realization method of the present invention comprises the following contents:

[0010] 1. Layout planning: Complete the determination of chip height and width, complete the arrangement of PAD, complete the placement of RAM, and complete power supply planning. The arrangement of the PAD also considers multiple factors such as the convenience of routing the chip to the PCB board in the future, the ease of implementation inside the chip, and SSO. Sensitive ports such as clocks use PADs with Schmitt hysteresis effects to improve noise immunity. The number of RAM units reaches 125, occupying 70% of the chip area. Combined with the reasonable planning of data flow, a certain space needs to be reserved between each RAM unit to place clock drive components. The electric-ground network adopts the combination of ring and stripe, and finally achieves...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More