Packaging substrate as well as manufacturing method and packaging structure thereof

A technology for packaging substrates and packaging structures, which is applied in semiconductor/solid-state device manufacturing, electrical components, electric solid-state devices, etc., can solve the problems of poor reliability of joints, influence on overall electrical properties, high cost, etc., and achieve good circuit shape and metal Effects of bump shape, stable package quality, and stable reliability

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

no. 1 example

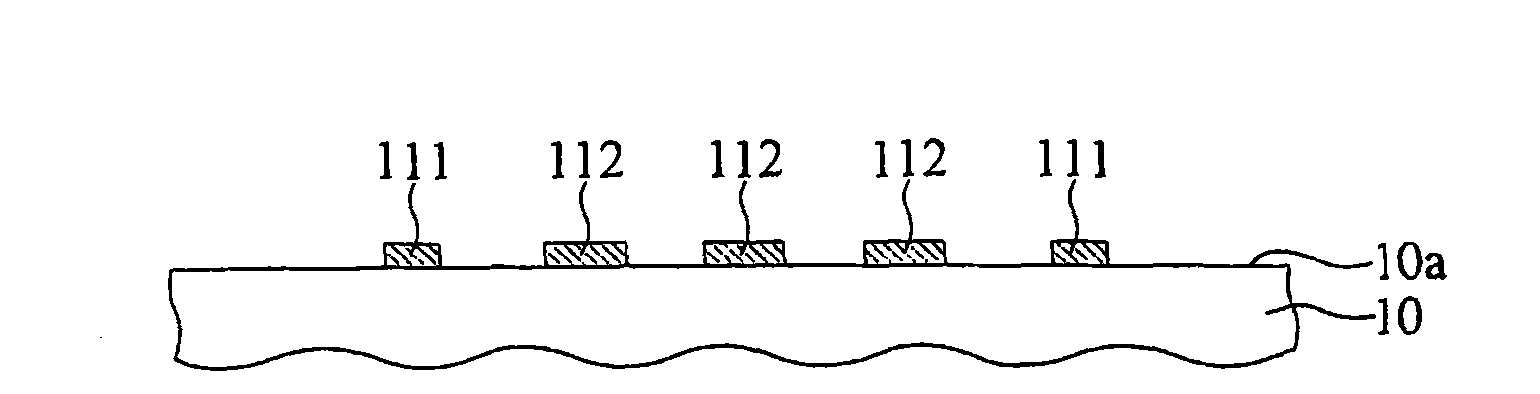

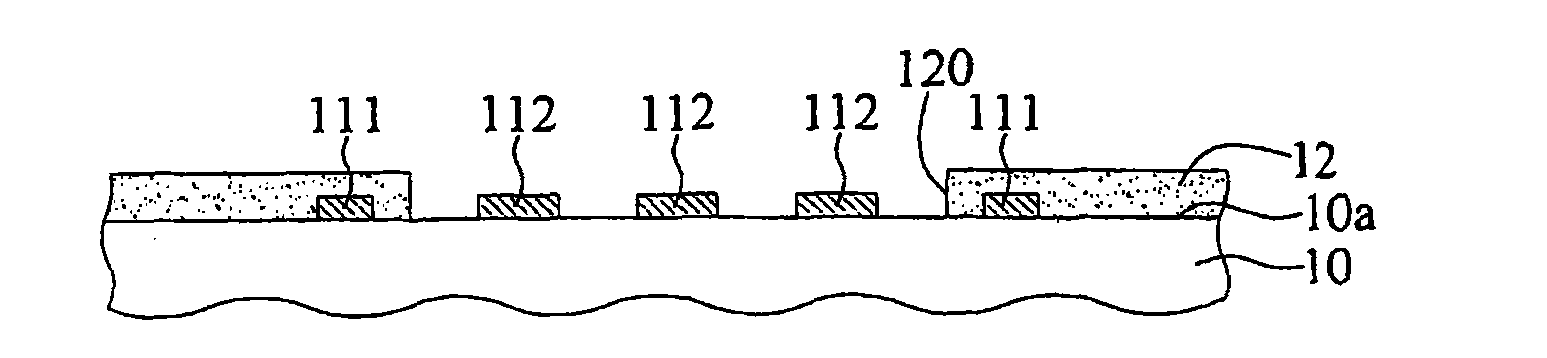

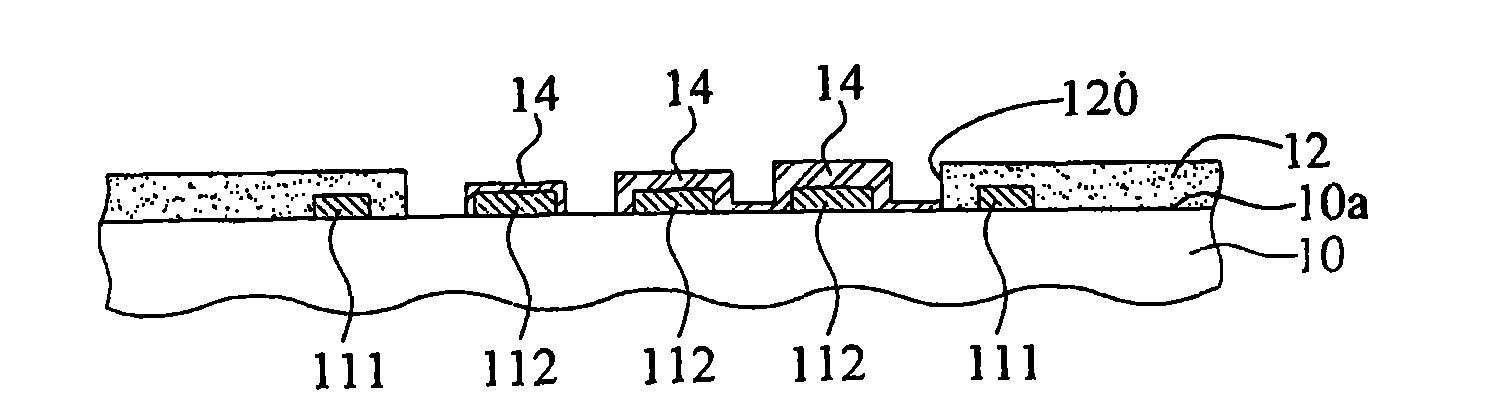

[0066] see Figure 2A to Figure 2F , is a schematic cross-sectional view of the first embodiment of the packaging substrate, its manufacturing method, and packaging structure of the present invention.

[0067] Such as Figure 2A As shown, first, a substrate body 30 is provided, at least one surface 30 a of which has a plurality of electrical contact pads 312 and circuits 311 , and the electrical contact pads 312 and circuits 311 can be made of copper material.

[0068] Such as Figure 2B As shown, an insulating layer 32 is formed on the surface 30a of these electrical contact pads 312, circuits 311 and the substrate body 30, and the thickness of the insulating layer 32 is smaller than the thickness of the electrical contact pads 312 and the circuits 311; Layer 32 can be the organic resin that has good binding force with copper, and the thickness of this insulation layer 32 can be 0.5 to 8 micron (μm) more preferably; In addition, the method for forming this insulation layer ...

no. 2 example

[0080] see Figure 3A to Figure 3H , is a schematic cross-sectional view of a second embodiment of the packaging substrate, its manufacturing method, and packaging structure of the present invention.

[0081] Such as Figure 3A As shown, firstly, a substrate body 50 is provided, at least one surface 50a of which has a conductive layer 51 .

[0082] Such as Figure 3B As shown, a first resistance layer 52 is formed on the conductive layer 51, and the first resistance layer 52 has a plurality of patterned openings 520; then, the conductive layer 51 is used to form lines in these openings 520 by electroplating layer 53, and the circuit layer 53 includes a plurality of electrical contact pads 532 and circuits 531, and the circuit layer 53 can be made of copper material.

[0083] Such as Figure 3C As shown, a second resistive layer 54 is formed on the first resistive layer 52 and the circuit layer 53 , and a plurality of resistive layer openings 540 are formed in the second re...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More