Array field effect transistor

A field-effect transistor, array-type technology, applied in the direction of electric solid-state devices, semiconductor devices, semiconductor/solid-state device parts, etc., can solve the problems of limited length of the interconnection well 202, which is difficult to meet, and improve the conduction of static charges. Ability, effect of increasing contact length

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment Construction

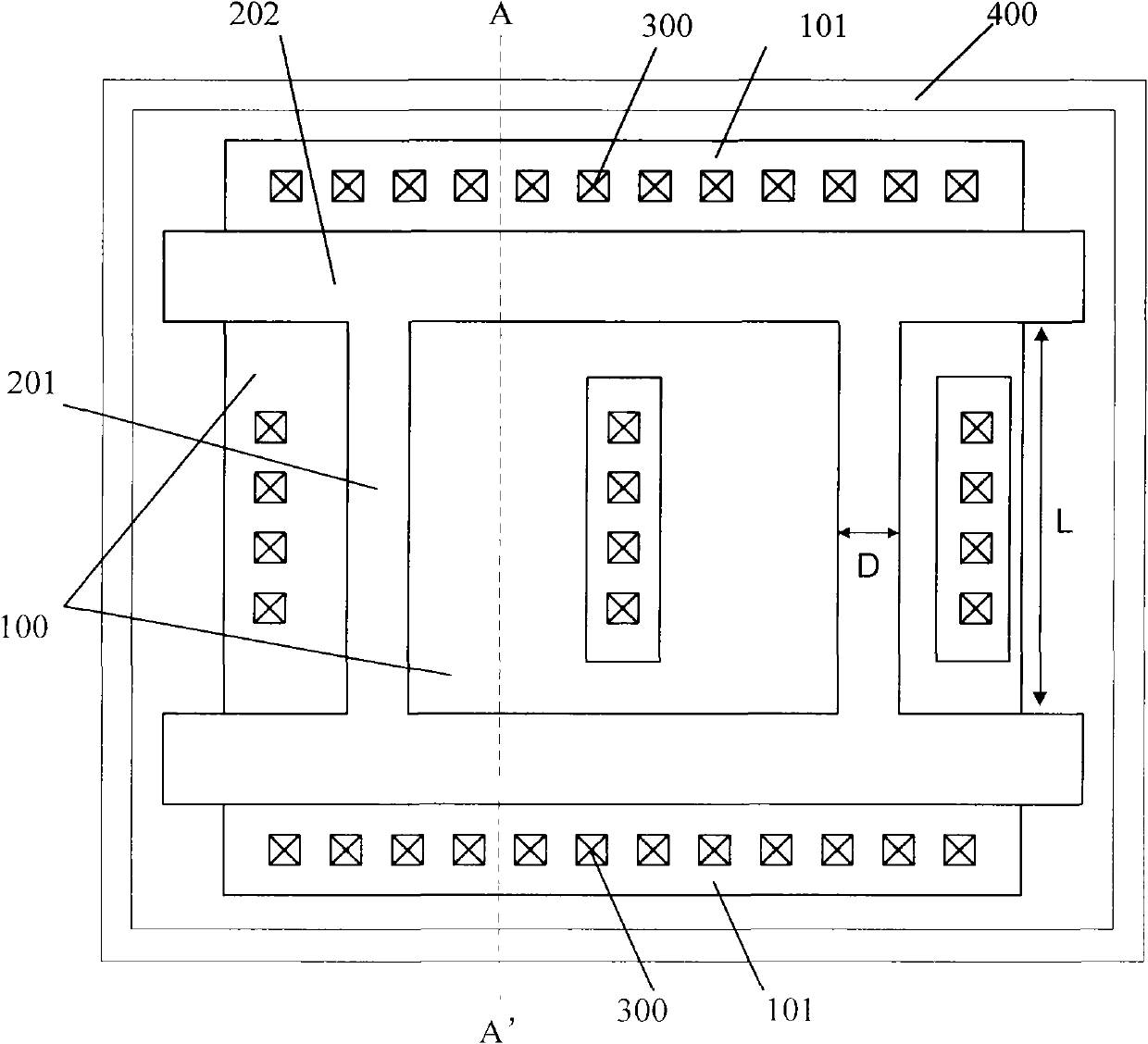

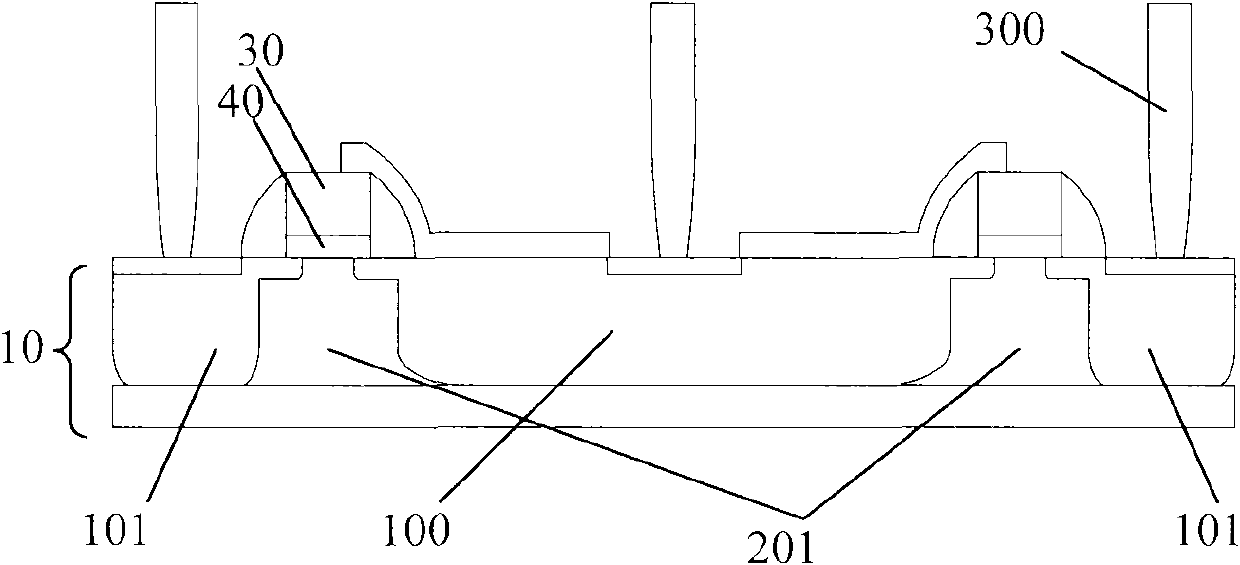

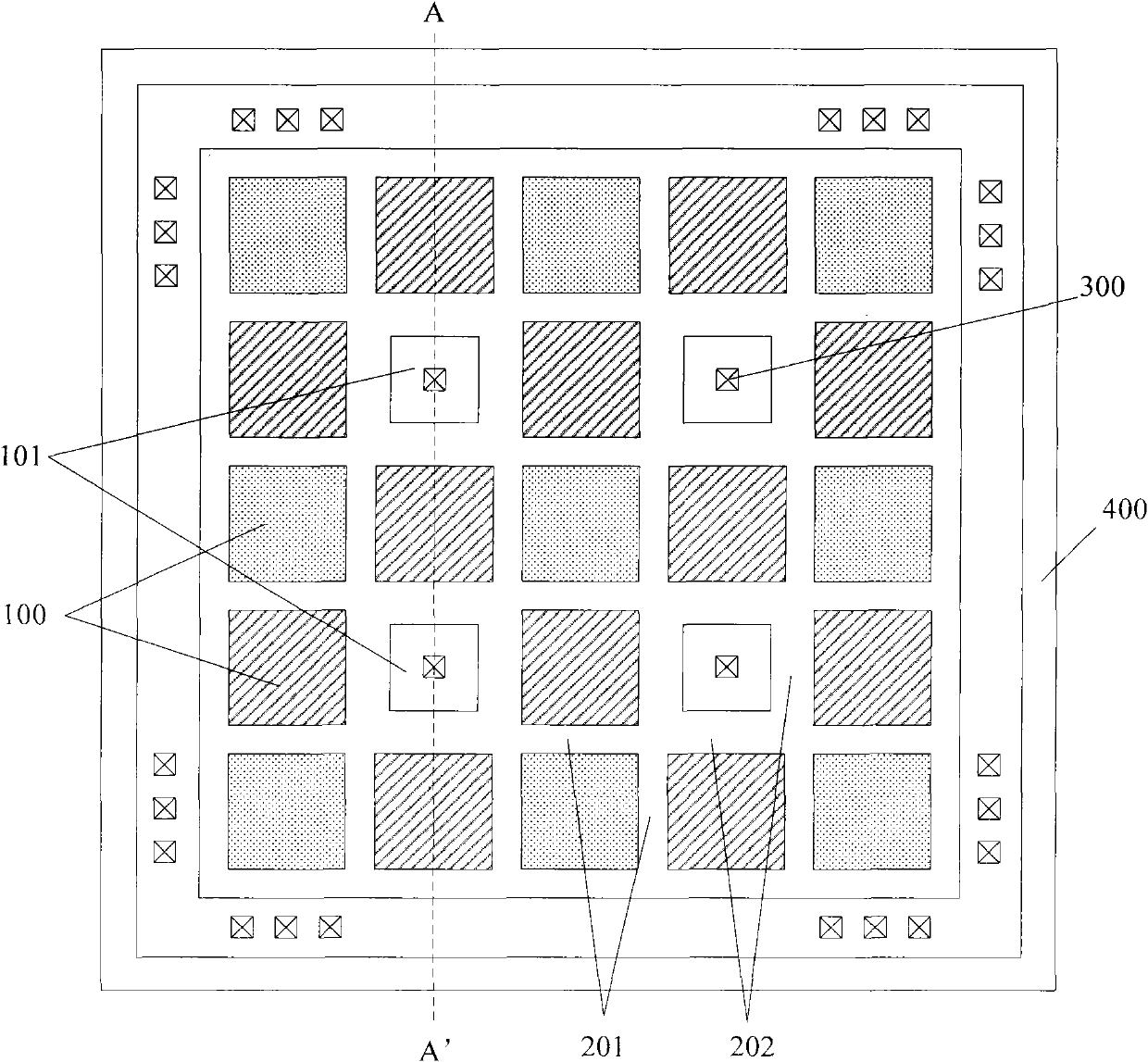

[0028] It can be seen from the background technology that in the existing finger-shaped field effect transistors, the interconnection well and the interconnection region are located on both sides of the diffusion region arranged in parallel, and the contact length between the diffusion region and the interconnection well is the longest of the entire field effect transistor area. The two sides of the diffusion region are long, so the parasitic diodes only exist on both sides of the diffusion region. However, the present invention arranges the diffusion regions and the interconnection regions in an array, so that the channel wells between adjacent diffusion regions and the interconnection wells between adjacent diffusion regions and interconnection regions form a network of “wells” The well line can greatly increase the contact length between the diffusion region and the interconnection well without reducing the channel width.

[0029] The array type field effect transistor prov...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More