SEU (single event upset)/SET (single event transient)-resistant dynamic comparator

A single-event transient and dynamic comparator technology, which is applied to multiple input and output pulse circuits, can solve the problems of output latch circuit storage node influence, weaken the reinforcement effect, etc., achieve the same driving capability and reduce power consumption , It is beneficial to the effect of high-speed system

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment Construction

[0021] The present invention will be described in further detail below in conjunction with the accompanying drawings.

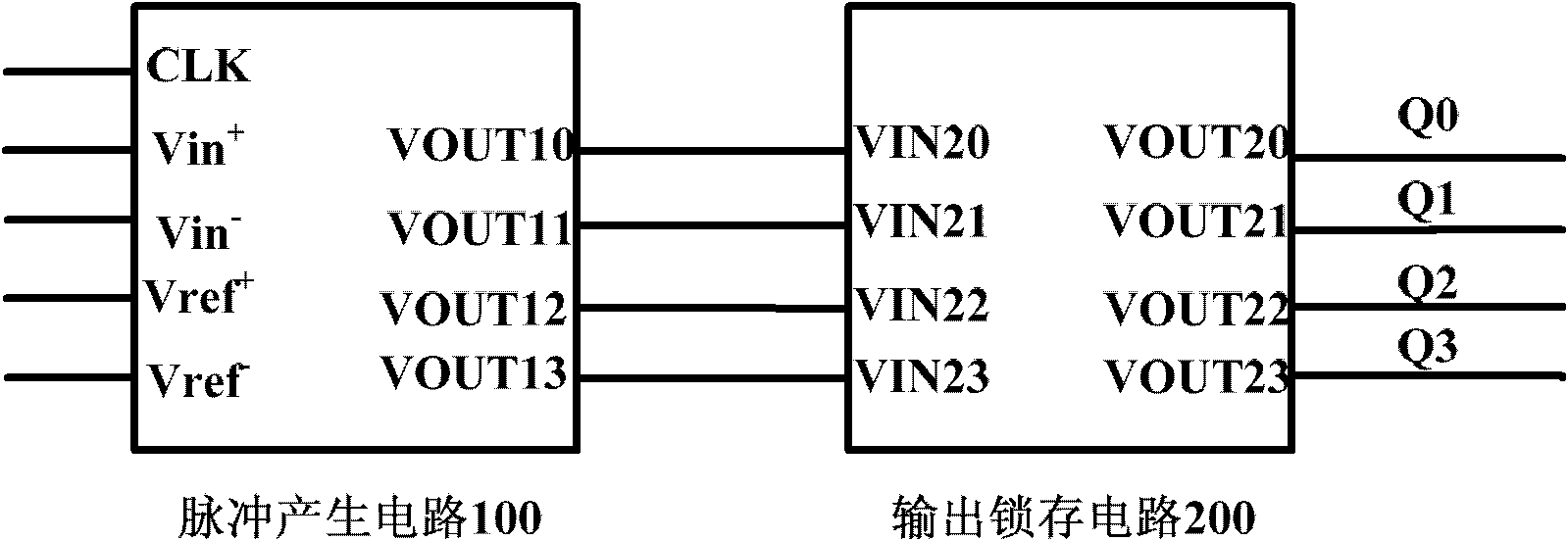

[0022] Such as figure 1 As shown, the dynamic comparator includes: a pulse generating circuit 100 based on a sense amplifier structure and an output latch circuit 200, the top layer of the entire comparator has five input ports and four output ports externally, and the five input ports are respectively connected to the clock signal CLK , input signal Vin + and Vin - and the reference voltage signal Vref + and Vref - , the output port is connected to the data output signal Q0, Q1, Q2, Q3, wherein: the pulse generation circuit 100 is connected to the clock signal, the input signal, the reference voltage signal, and the output latch circuit 200; the output latch circuit 200 is connected to the pulse generation circuit 100, Data output signal connection.

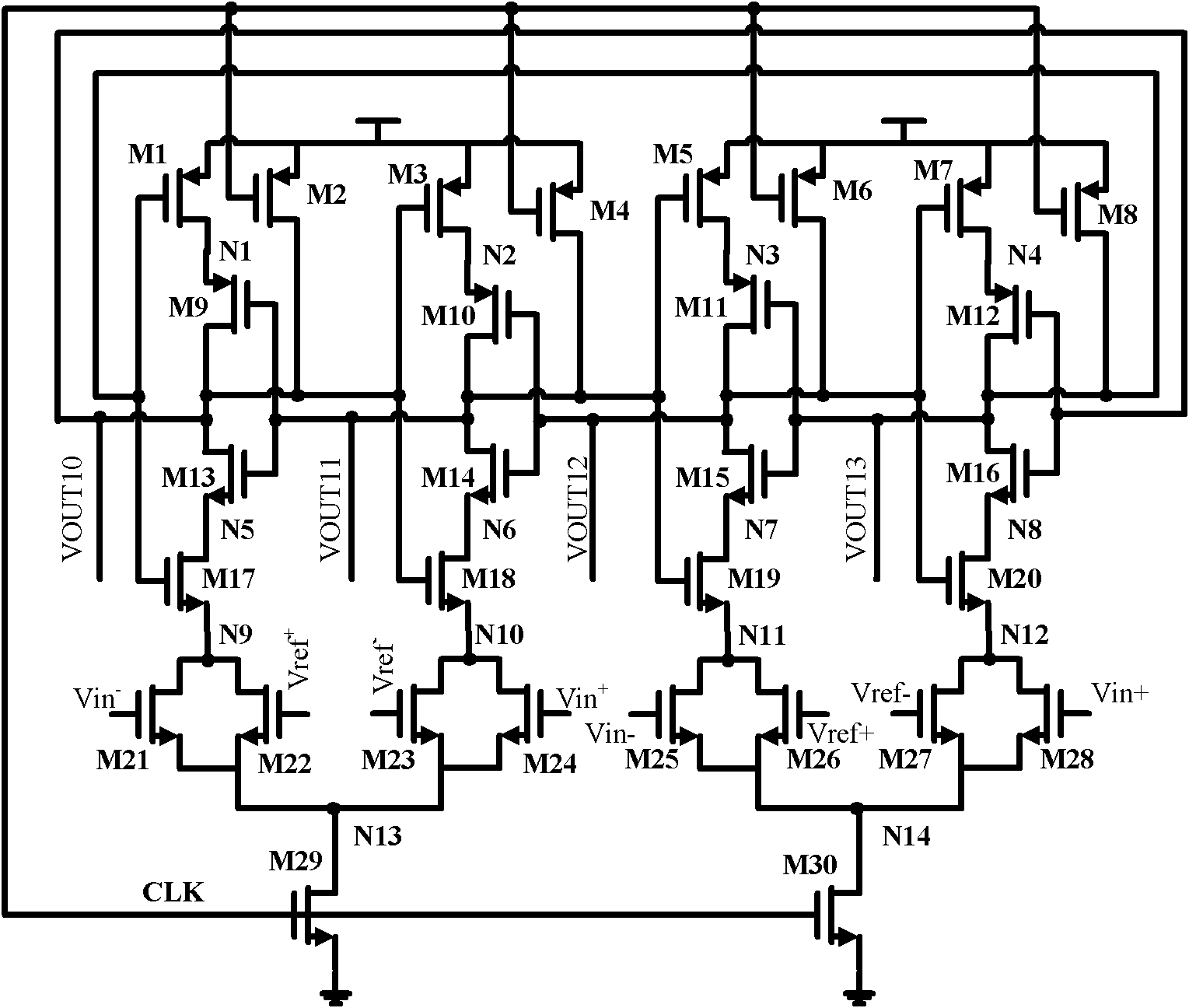

[0023] The pulse generation circuit 100 includes a clock signal input terminal CLK connected to the clo...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More