Anti-single event transient circuit

A transient circuit, anti-single event technology, applied in the direction of logic circuit connection/interface layout, logic circuit coupling/interface using field effect transistors, etc., can solve the problems of high area and power consumption, redundancy of latch units, etc. , to achieve the effect of simplified design, low power consumption, and reduced area

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment Construction

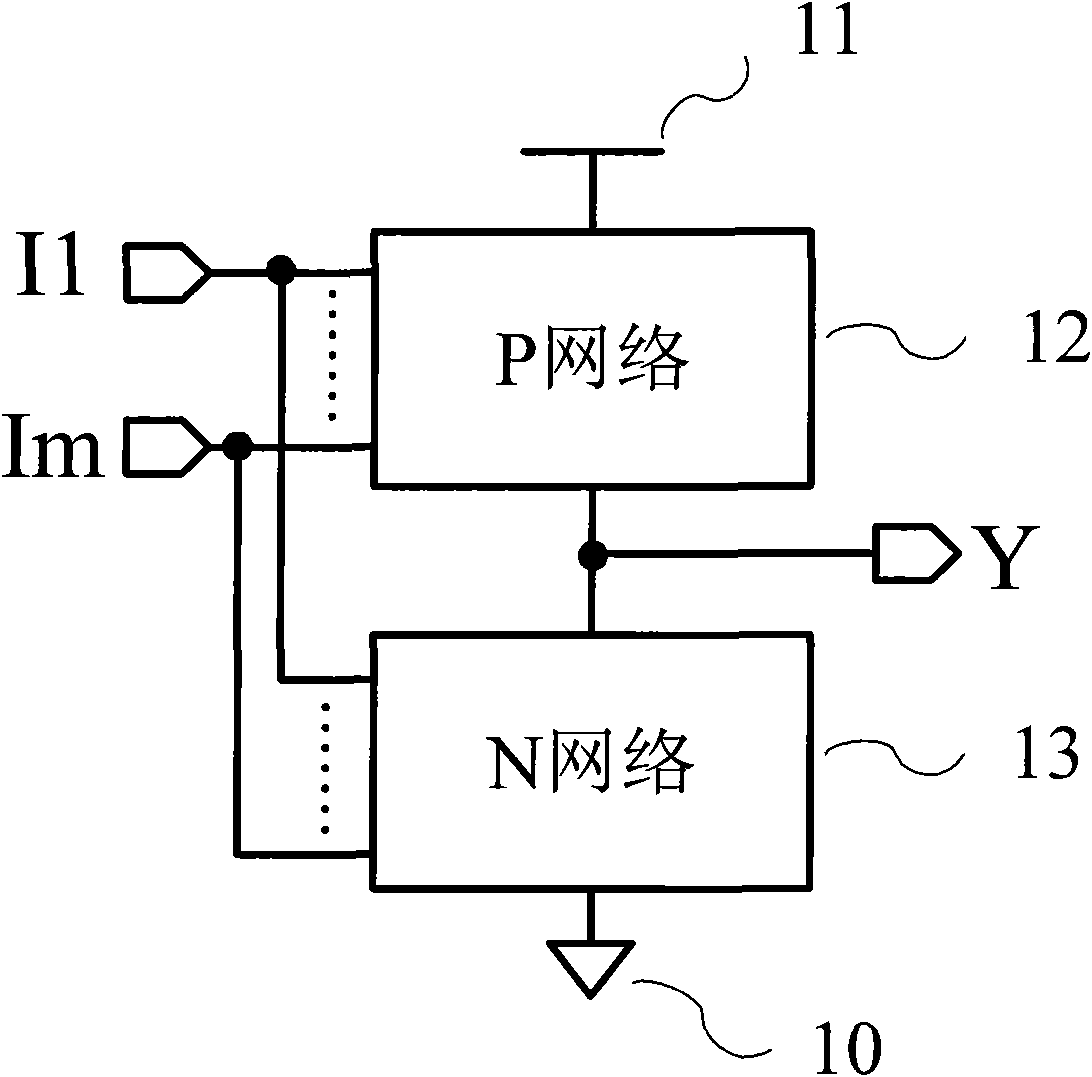

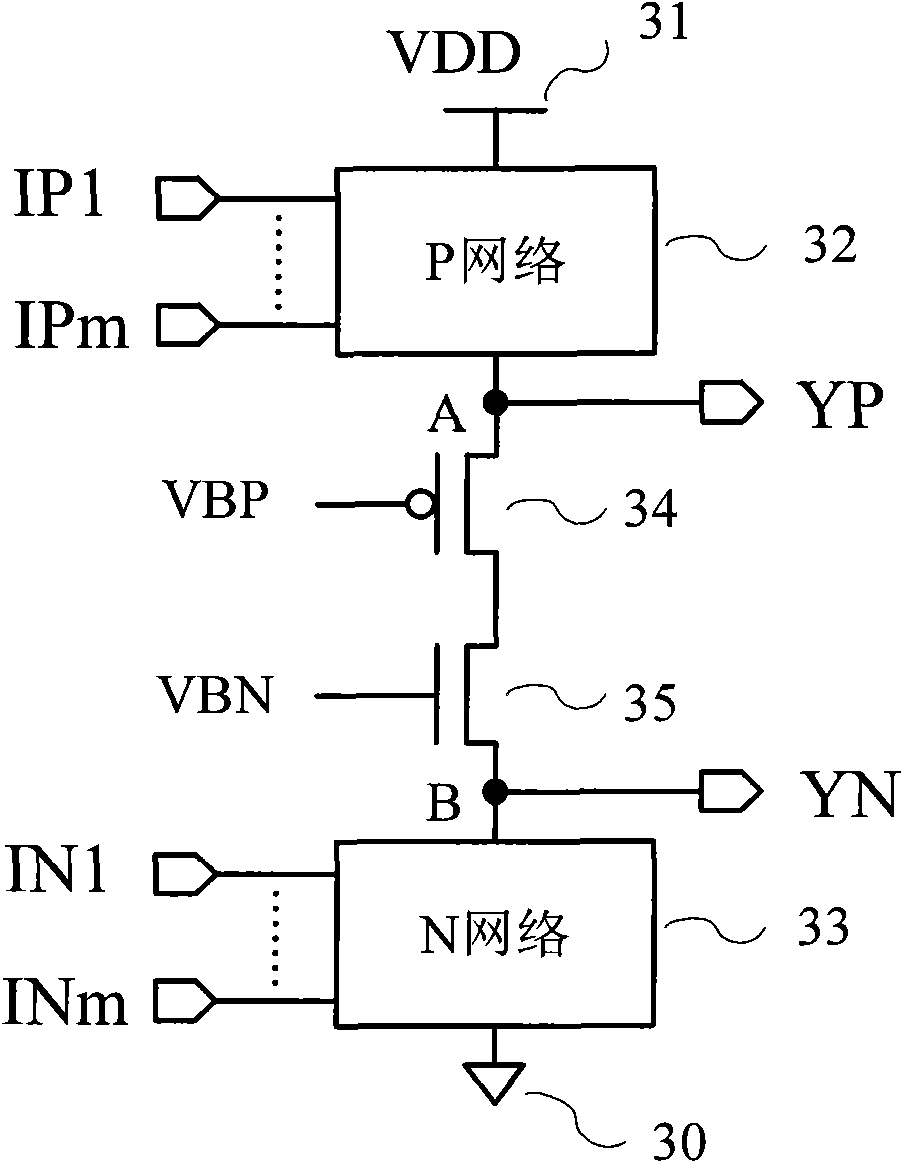

[0022] like image 3 Shown is the single-stage structure of the circuit of the present invention. The circuit is composed of power supply 31 (VDD), ground 30, P network 32, N network 33, and PMOS transistor 34 and NMOS transistor 35 between P network 32 and N network 33. P network 32 is connected to power supply 31 and PMOS transistor respectively. The source terminals of 34 are connected, and the output signal at the junction A of the P network 32 and the PMOS transistor 34 is YP, and the N network 33 is connected with the source terminals of the ground 30 and the NMOS transistor 35 respectively, and the N network 33 is connected with the NMOS transistor 35. The output signal at the connected node B is YN. The P network 32 is composed of PMOS transistor logic, that is, it is composed of several PMOS transistors connected in series and parallel. There may be multiple connection methods according to different functions. The N network 33 is composed of NMOS transistors. Logical...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More