On-chip heterogeneous multi-core system based on star type interconnection structure, and communication method thereof

A heterogeneous multi-core, architecture technology, applied in the fields of instruments, electrical digital data processing, computers, etc., can solve the problems of increasing the difficulty of layout and wiring, hardware overhead, and many hardware resources, and achieve the effect of reducing logic and improving throughput.

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment

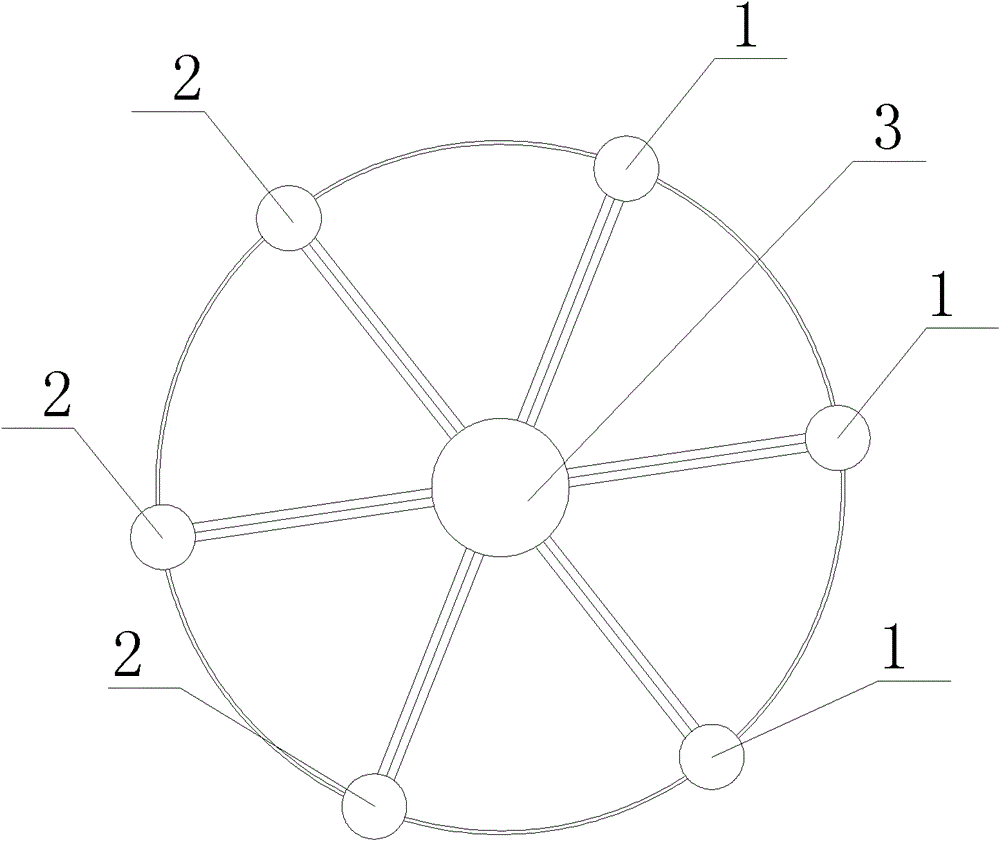

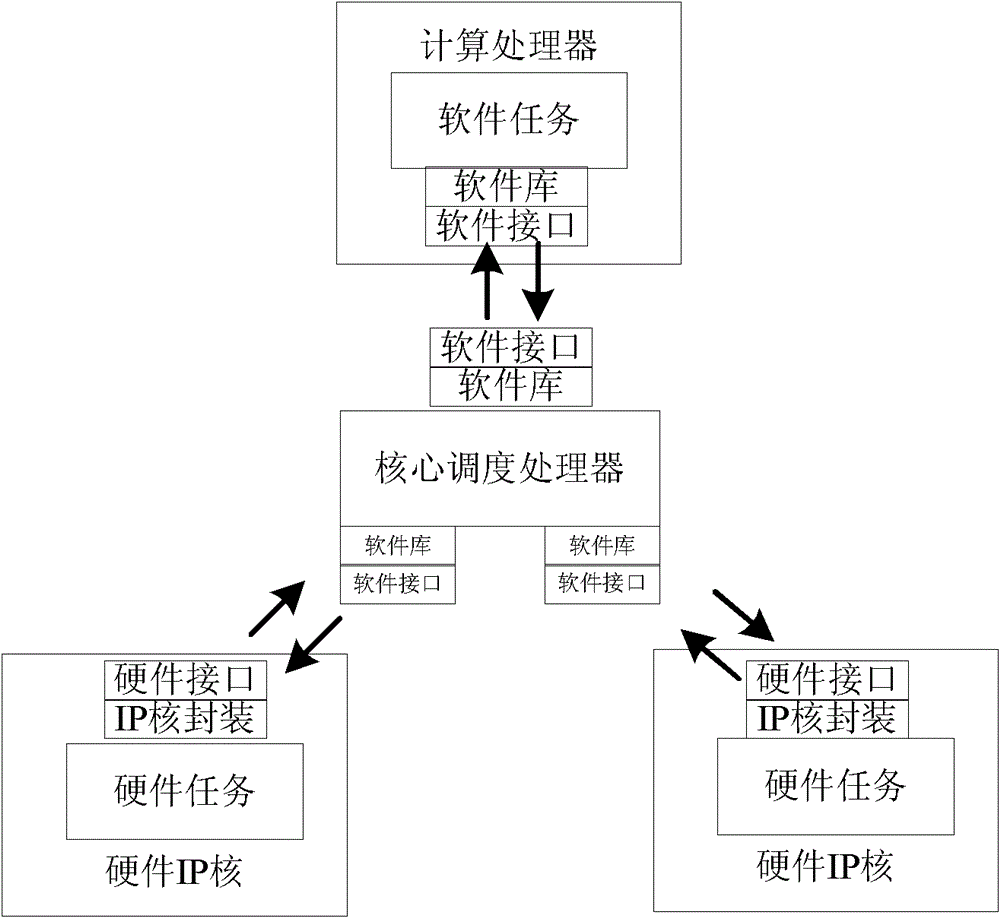

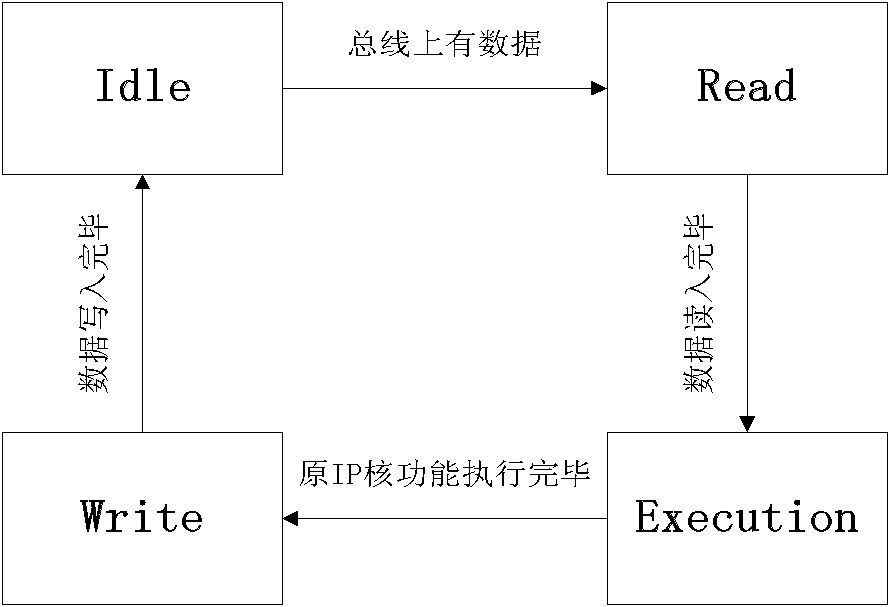

[0036] Such as figure 1 As shown, the on-chip heterogeneous multi-core system obtained in this embodiment is composed of a core scheduling processor 3, 3 computing processors 1 and 3 IP cores 2, and the core scheduling processor is connected to the computing processor and the IP core. The on-chip bus based on the point-to-point bus is used for interconnection, and the message transmission between the core scheduling processor and the computing processor is based on the communication model of the interconnection architecture. The communication model is implemented using a non-blocking interface. The core scheduling processor is responsible for receiving task requests from users, and sending the task requests to computing processors through the interconnection structure. The calculation processor is responsible for receiving task requests from the core scheduling processor and performing task calculations. The on-chip network based on the point-to-point bus is used for interco...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More