A method for testing the fault of embedded multi-bit memory in fpga

A test method and memory technology, applied in static memory, instruments, etc., can solve the problem of undetectable memory cell coupling faults, and achieve the effect of easy implementation and improved fault coverage.

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

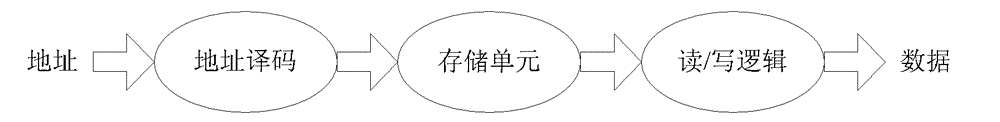

Method used

Image

Examples

Embodiment Construction

[0065] Taking Xilinx's Spartan-3 series XC3S400 FPGA embedded memory as the test object, a test method for the fault of the embedded multi-bit memory in FPGA is described. The specific implementation steps of the method are as follows:

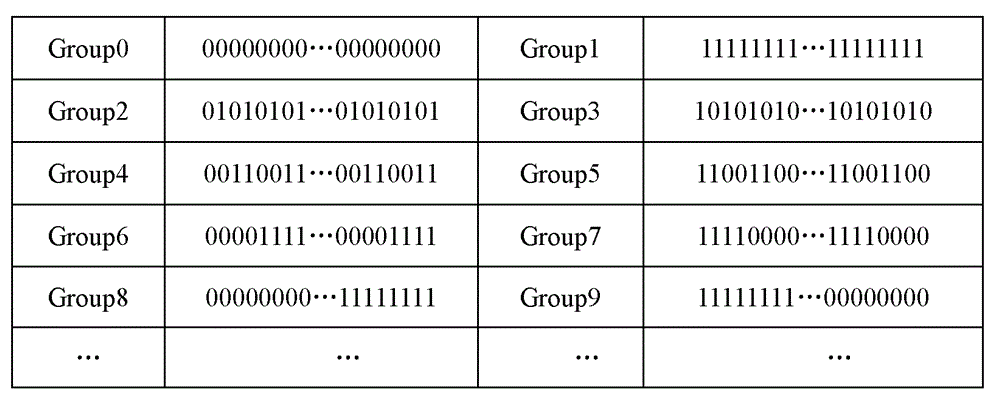

[0066] Step 1: First, add test patterns based on the March C-algorithm. For the embedded n-bit memory inside the FPGA, the number of test patterns should be 2×(1+log 2 n). XC3S400 FPGA embedded memory bit width is 16 bits, so the number of test patterns is 10. The test pattern looks like this:

[0067] Group0

0000000000000000

Group1

1111111111111111

Group2

0101010101010101

Group3

1010101010101010

Group4

0011001100110011

Group5

1100110011001100

Group6

0000111100001111

Group7

1111000011110000

Group8

0000000011111111

Group9

1111111100000000

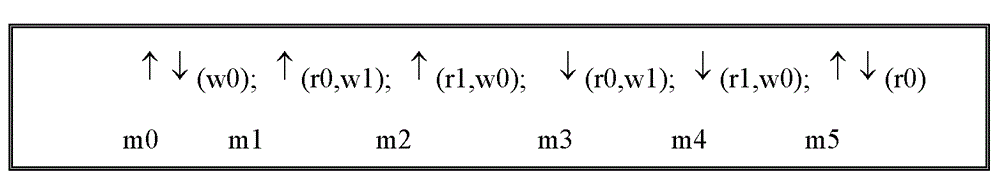

[0068] Step 2: Substituting 10 test patterns into the 6 March elements of the M...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More