Method for fabricating a gate dielectric layer

A gate dielectric layer and manufacturing method technology, applied in semiconductor/solid-state device manufacturing, circuits, electrical components, etc., can solve the problems of reduction, increase of equivalent thickness of high dielectric constant gate dielectric layer 112, etc., to achieve The effect of maintaining the performance characteristics of the device

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment Construction

[0028] The present invention will provide many different embodiments to implement different features of the present invention. The composition and configuration of each specific embodiment will be described below to simplify the present invention. These are examples and do not limit the present invention. In addition, "above", "on", "under" or "on" a first element formed on a second element may include that the first element is in direct contact with the second element in the embodiment, or may also include There are other additional elements between the first element and the second element so that the first element and the second element do not directly contact. Various elements may be shown in arbitrarily different scales for clarity and simplicity of illustration.

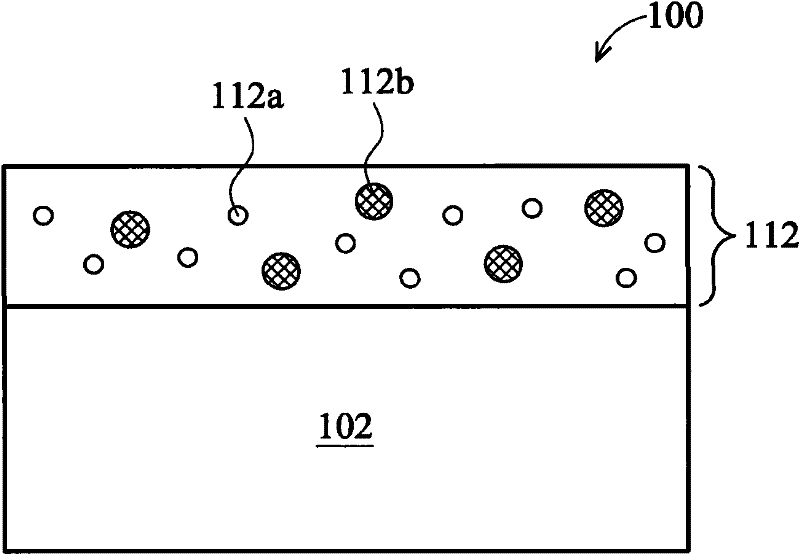

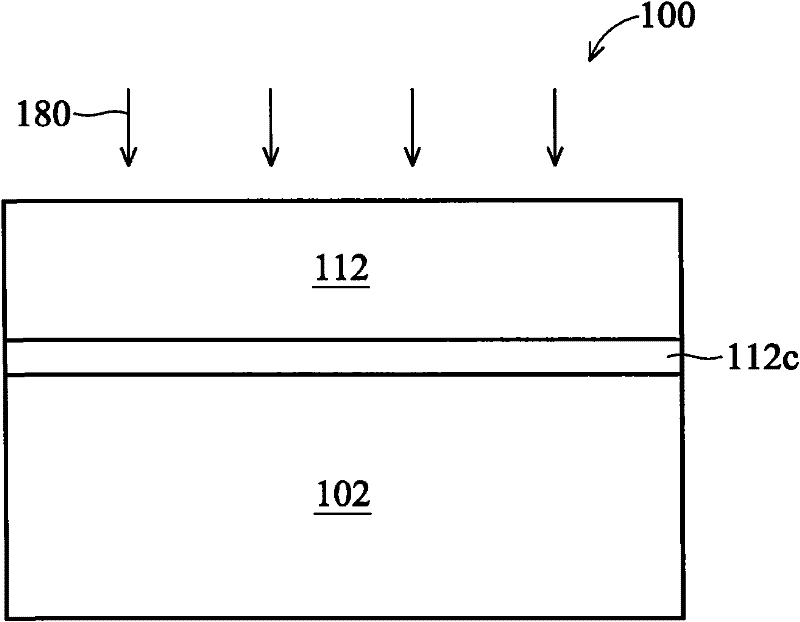

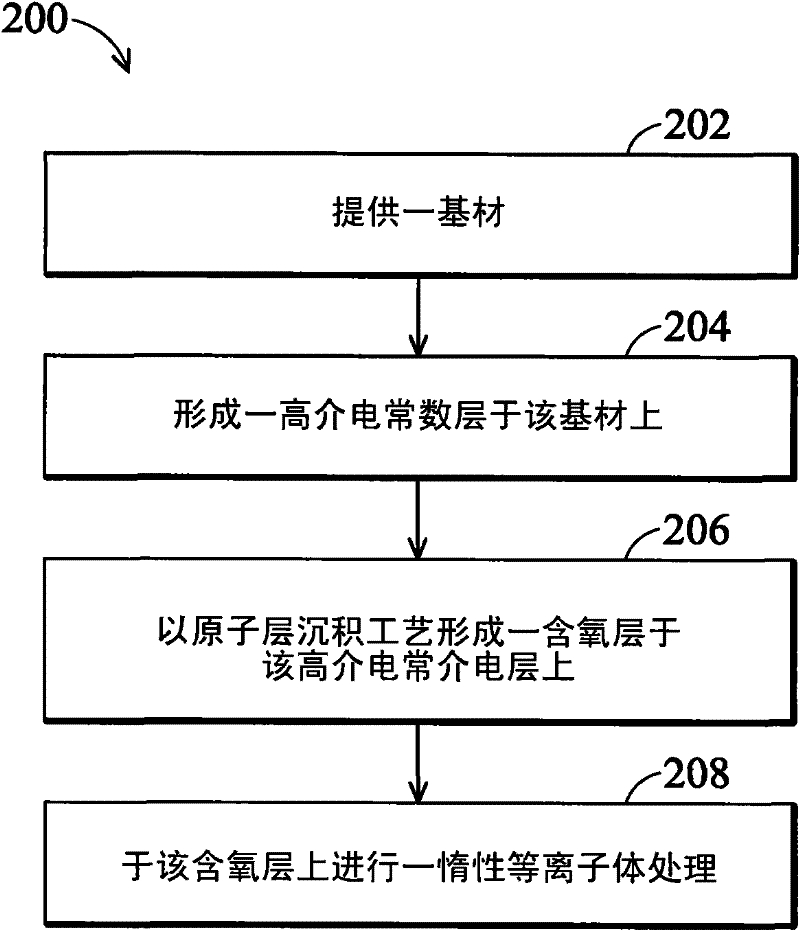

[0029] figure 2 A method 200 of fabricating the high-k gate dielectric layer 312 (shown in FIG. 3 ) in accordance with an embodiment of the present invention is shown. Figure 3A-Figure 3H A cross-sectional...

PUM

| Property | Measurement | Unit |

|---|---|---|

| thickness | aaaaa | aaaaa |

| thickness | aaaaa | aaaaa |

| thickness | aaaaa | aaaaa |

Abstract

Description

Claims

Application Information

Login to View More

Login to View More